恒压产生电路的制作方法

1.本发明涉及例如在比较低的输入输出间电位差的情况下也进行动作的低压差稳压器(以下称为ldo)等恒压产生电路。

背景技术:

2.以往,在与输出电压值、输出电流值或者端子施加电压的极性相应地切换多个模式的电源电路的结构中,在共享基准电压源的情况下,在各模式的切换时与基准电压源连接的晶体管的漏极以及源极的一方或者双方的电位发生变动。在上述切换时晶体管的寄生电容作为耦合电容作用,噪声重叠于基准电压源而在切换前后基准电压发生变化。由此,电源电路的输出电压跟随于此从而发生输出电压变化,或者与电源电路的输出电压变化相伴而发生输出电流的变化。并且,由于输出电压变化、或者与电源电路的输出电压变化相伴的输出电流的变化而诱发意外的模式迁移,在最坏的情况下,存在导致在各模式间持续迁移的误动作这样的问题点。

3.作为避免上述的误动作的手段,已知为了不对另一方的电路动作造成影响而在发生电位变动的电路与另一方的电路间使用不同的基准电压源的方法。进而,为了对重叠至基准电压源的噪声的绝对值进行抑制,在模式切换时,减小漏极以及源极的一方或者双方的电位变动的与基准电压源连接的晶体管的尺寸来减少寄生电容,该方法也是已知的事实。并且,对差分放大器赋予偏置,以使在基准电压在切换前后发生了变化时,不会由于存在电源电路的输出电压跟随于基准电压的控制引起电源电路的输出电压变化、或者与其相伴的输出电流的变化从而导致模式发生切换,该方法也作为已知技术存在。

4.例如,在专利文献1中公开了一种串联稳压器,具有:第一放大器,对被连接在电源与负载之间的第一晶体管进行驱动;第二放大器,对与第一晶体管并联连接的第二晶体管进行驱动;以及放大器控制电路,对第一放大器以及第二放大器分别进行控制。在该串联稳压器中,第二晶体管的电流能力设定为比第一晶体管的电流能力小,第二放大器的消耗电流设定为比第一放大器的消耗电流小。放大器控制电路对第一放大器以及第二放大器分别进行控制,以使在流向负载的输出电流比规定的放大器切换阈值小的第一负载区域中,使在第一晶体管中流动的第一输出电流成为零值,由在第二晶体管中流动的第二输出电流供给全部输出电流。另一方面,在输出电流比放大器切换阈值大的第二负载区域中,使第二输出电流成为零值或者比放大器切换阈值小的固定值。此外,对第一放大器以及第二放大器分别进行控制,以使由第一输出电流供给全部输出电流或者从输出电流减去第二输出电流而得到的差分。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2019-185095号公报

技术实现要素:

8.发明要解决的课题

9.但是,作为以往的避免在各模式间持续迁移的误动作的手段,使用不同的基准电压源的方法会导致芯片面积增大,而且由于基准电压源的加工偏差,各模式的输出电压之差会导致精度劣化。此外,使晶体管尺寸变小的方法会发生晶体管间的错误匹配,造成比较器或者差分放大器的特性偏差增大,这也会引起各模式间产生的输出电压之差变大,而导致输出电压精度劣化。进而,对差分放大器赋予偏置的方法需要赋予基准电压源上重叠的噪声以上的偏置,因此与上述同样存在输出电压的精度劣化等问题点。

10.本发明的目的在于解决以上的问题点,提供与现有技术相比能够抑制输出电压的精度劣化、并且防止在多个模式间持续迁移的误动作的恒压产生电路。

11.用于解决课题的手段

12.本发明的一方式所涉及的恒压产生电路具备:

13.晶体管,被连接在电源与负载之间,对输出电流进行控制;

14.第一放大电路,基于来自所述电源的基准电压,对所述晶体管进行驱动;

15.第二放大电路,与所述第一放大电路并联连接,比所述第一放大电路更快速地动作,基于来自所述电源的基准电压,对所述晶体管进行驱动;

16.保护电路,在规定动作时,限制从所述晶体管流向所述负载的输出电流;以及

17.控制电路,对所述第二放大电路的动作进行控制,

18.所述控制电路进行控制,以使在所述输出电流从轻负载时增大到规定的第二阈值电流为止不使所述第二放大电路动作,在成为所述第二阈值电流以上时使所述第二放大电路动作,另一方面,在所述输出电流从重负载时减少到比所述第二阈值电流小的规定的第一阈值电流为止使所述第二放大电路动作,在成为所述第一阈值电流以下时不使所述第二放大电路动作,

19.所述第二放大电路还包含:在非动作时将所述第二放大电路的内部节点的动作电位固定的第一动作电位固定电路。

20.发明效果

21.从而,根据本发明所涉及的恒压产生电路,能够抑制由于经由耦合电容的噪声重叠而产生的基准电压源的输出电压的变化。由此,能够将差分放大器的偏置电压设定得小,抑制在各模式中作为输出电压之差而发生的输出电压的精度的劣化,并且防止电源电路在多个模式间持续迁移的误动作。

附图说明

22.图1是表示实施方式所涉及的恒压产生电路2及其周边电路的结构例的框图。

23.图2是表示图1的差分放大电路21、22的详细结构的电路图。

24.图3是表示图1的恒压产生电路2的差分放大电路21以及用于保护执行电路13的差分放大电路22的停止动作的定时图。

25.图4是表示变形例1所涉及的差分放大电路21a的结构例的框图。

26.图5是表示变形例2所涉及的差分放大电路21b的结构例的框图。

27.图6是表示变形例3所涉及的差分放大电路21c的结构例的框图。

28.图7a是说明在图1的差分放大电路21中使用的阈值电流ith1、ith2的设定值的图。

29.图7b是说明在图1的差分放大电路22中使用的阈值电流ith3、ith4的设定值的图。

具体实施方式

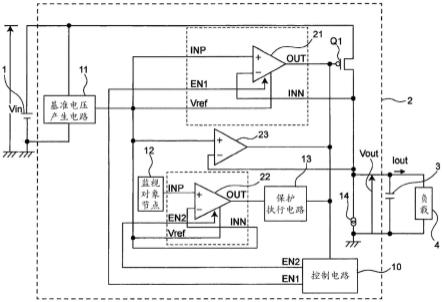

30.以下,参照附图说明本发明所涉及的实施方式。另外,针对相同或者同样的结构元素附加相同的标号。

31.(发明人的知识和见识)

32.在专利文献1所公开的串联稳压器中发现了如下情况:在动作模式发生切换时,差分放大器的噪声经由mos晶体管的寄生电容而重叠于来自具有高输出电阻的基准电压源的输出电压,从而发生在2个动作模式间相互切换的切换振荡这样的电路的误动作。以下的实施方式的目的在于防止该误动作。

33.(实施方式)

34.图1是表示实施方式所涉及的恒压产生电路2及其周边电路的结构例的框图。

35.在图1中,从直流电压源1将输入电压vin向恒压产生电路2输入。恒压产生电路2例如是ldo,基于输入电压vin,产生一定的恒压vout,经由输出电容器3向负载4输出。

36.恒压产生电路2构成为具备基准电压产生电路11、监视对象节点12、保护执行电路13、p沟道mos晶体管q1、电流源14、3个差分放大电路21、22、23、以及对所述差分放大电路21、22的动作进行控制的控制电路10。

37.基准电压产生电路11将输入电压vin变换为规定的基准电压vref并输出。差分放大电路21、22例如是具有相同电路结构的“带电压变动抑制功能的差分放大电路”,基于来自控制电路10的使能信号en1、en2,例如以10mhz~数100mhz的动作频率动作,比差分放大电路23更快速且以更高的功耗动作。在此,差分放大电路21、22分别响应于来自控制电路10的h电平(level)的使能信号en1、en2而动作,另一方面,响应于l电平的使能信号en1而不动作。在此,差分放大电路21是恒压产生电路2的主差分放大器,产生规定的恒压并供应给负载4。此外,差分放大电路23是恒压产生电路2的副差分放大器,产生规定的恒压并供应给负载4。

38.在此,差分放大电路21构成在重负载时在控制上占支配地位的主差分放大电路,差分放大电路22构成为在重负载时在控制上不占支配地位的副差分放大电路。即,在重负载时两个差分放大电路21、22动作,此时消耗电流大的差分放大电路21构成主差分放大电路,与差分放大电路21相比消耗电流小的差分放大电路22构成副差分放大电路。

39.进而,差分放大电路22例如对电压与vout成比例变化的监视对象节点12的电压进行检测,与包含差分放大器的保护执行电路13一起,构成例如使用公知的brickwall限流法或者foldback限流法等执行输出电流iout的限制等保护处理的保护电路。

40.差分放大电路21、23以及保护执行电路13的输出端子连接至与栅极电压相应地对输出电流iout进行控制的mos晶体管q1的栅极,由此,差分放大电路21、23以及保护执行电路13对mos晶体管q1进行驱动,对mos晶体管q1中流动的输出电流iout进行控制。此外,输入电压vin的正极经由mos晶体管q1的源极及漏极、电流源14而被接地。

41.图7a是说明在图1的差分放大电路21中使用的阈值电流ith1、ith2的设定值的图。此外,图7b是说明在图1的差分放大电路22中使用的阈值电流ith3、ith4的设定值的图。控

制电路10将mos晶体管q1的栅极电压换算为输出电流iout,或者,基于来自对输出电压端子中流动的输出电流iout进行检测的电流传感器的表示输出电流iout的电流信号,以如下方式动作。

42.(1)控制电路10如图7a所示,在输出电流iout从电流0或者轻负载时增大到阈值电流ith2为止,将l电平的使能信号en1向差分放大电路21输出,在成为iout≥ith2时,将h电平的使能信号en1向差分放大电路21输出。另一方面,在输出电流iout从重负载时减少到阈值电流ith1(<ith2)为止,将h电平的使能信号en1向差分放大电路21输出,在成为iout≤ith1时,将l电平的使能信号en1向差分放大电路21输出。即,通过图7a那样的滞后动作,控制电路10对差分放大电路21进行控制。

43.(2)控制电路10如图7b所示,在输出电流iout从电流0或者轻负载时增大到阈值电流ith4为止,将l电平的使能信号en2向差分放大电路22输出,在成为iout≥ith4时,将h电平的使能信号en2向差分放大电路22输出。另一方面,在输出电流iout从重负载时减少到阈值电流ith3(<ith4)为止,将h电平的使能信号en2向差分放大电路22输出,在成为iout≤ith3时,将l电平的使能信号en2向差分放大电路22输出。即,通过图7b那样的滞后动作,控制电路10对差分放大电路22进行控制。

44.另外,各阈值电流ith1~ith4的关系如下设定。

45.ith1≤ith3<ith2

ꢀꢀꢀꢀꢀꢀ

(1)

46.ith2≤ith4

ꢀꢀꢀꢀꢀꢀ

(2)

47.在此,作为“阈值电流的简单设定例”,也可以设定为阈值电流ith1=ith3,ith2=ith4。

48.图2是表示图1的差分放大电路21、22的详细结构的电路图。在图2中,差分放大电路21、22具有以下的5个端子t1~t5。

49.(1)反转输入端子(inn)t1;

50.(2)非反转输入端子(inp)t2;

51.(3)输出端子t3;

52.(4)使能信号端子t4;以及

53.(5)基准电压端子t5。

54.在图2中,差分放大电路21、22构成为具备逆变器33、偏置电压产生电路31、开关sw11、sw12、以及差分放大器32。另外,在图2中,多个mos晶体管q11~q34之中的mos晶体管q12、q22、q32由耗尽型构成,但也可以由增强型构成,以下是同样的。

55.偏置电压产生电路31构成为具备p沟道mos晶体管q11、n沟道mos晶体管q12和n沟道mos晶体管q13,这些mos晶体管被串联连接。mos晶体管q11的源极被施加电源电压vin,mos晶体管q11的栅极与其漏极连接。mos晶体管q12、q13的各栅极被相互连接并连接至端子t5。mos晶体管q12的源极与mos晶体管q13的漏极的连接点p1经由开关sw11,连接至差分放大器32内的mos晶体管q22的源极与mos晶体管q23的漏极的连接点p6。进而,mos晶体管q13的源极经由连接点p2且经由电流源41而被接地。连接点p2经由开关sw12连接至差分放大器32内的连接点p7。

56.如上构成的偏置电压产生电路31将端子t5被施加的基准电压vref变换为规定的偏置电压,并经由开关sw11施加至差分放大器32内的连接点p6。

57.图2的差分放大器32构成为具备mos晶体管q21、q22、q23、q31、q32、q33、q34、开关sw1、sw2、sw3、sw13、sw14、以及电流源42、43。mos晶体管q21、连接点p4、mos晶体管q22、连接点p6以及mos晶体管q23被相互串联连接,mos晶体管q21的源极与电源电压vin连接,mos晶体管q23的源极经由开关sw2以及电流源42而被接地。此外,mos晶体管q31、连接点p5以及mos晶体管q32、33被相互串联连接,mos晶体管q31的源极与电源电压vin连接,mos晶体管q33的源极经由开关sw2以及电流源42被接地。进而,mos晶体管q21、q31的各栅极被相互连接的连接点p3经由开关sw13连接至电源电压vin,并且经由开关sw1连接至连接点p4。

58.mos晶体管q32、q33的各栅极被相互连接之后连接至端子t2。连接点p5与mos晶体管q34的栅极连接,mos晶体管q34的栅极经由开关sw14连接至电源电压vin以及mos晶体管q34的源极。mos晶体管q34的漏极经由与端子t3连接的连接点、开关sw3以及电流源43而被接地。

59.端子t4被输入的使能信号en1、en2向开关sw1~sw3的各控制端子输入,并且向逆变器33输入,从逆变器33输出的反转使能信号/en1、/en2向开关sw11~sw14的各控制端子输入。在开关sw1~sw3的各控制端子被输入h电平的使能信号en1、en2时,各开关sw1~sw3被接通,另一方面,在被输入l电平的使能信号en1、en2时,各开关sw1~sw3被断开。此外,在开关sw11~sw14的各控制端子被输入h电平的反转使能信号/en1、/en2时,各开关sw11~sw14被接通,另一方面,在被输入l电平的反转使能信号/en1、/en2时,各开关sw11~sw14被断开。

60.在如上构成的差分放大电路21、22中,在被输入h电平的使能信号en1.en2时,开关sw1~sw3被接通且开关sw11~sw14被断开。此时,在来自偏置电压产生电路31的规定的偏置电压未被施加至差分放大器32的状态下,差分放大器32成为动作状态。从而,差分放大器32从非反转输入端子t2被输入的非反转输入电压inp减去反转输入端子t1被输入的反转输入电压inn,将通过对相减结果的电压进行放大而得到的输出电压从端子t3输出。另外,差分放大电路21的端子t3与图1的mos晶体管q1的栅极连接,差分放大电路22的端子t3经由图1的保护执行电路13连接至mos晶体管q1的栅极。

61.此外,在被输入l电平的使能信号en1.en2时,开关sw1~sw3被断开且开关sw11~sw14被接通。此时,在来自偏置电压产生电路31的规定的偏置电压施加至差分放大器32的状态下,差分放大器32成为非动作状态。从而,差分放大器32不进行所述的差分放大,成为从端子t3不输出的停止状态,但被施加着规定的偏置电压,因此抑制接点p6以及p7的电压变动,由此抑制经由mos晶体管q22、q23所具有的寄生电容的、mos晶体管q22、q23的栅极电压的变动。

62.即,差分放大电路21、22在动作时分别进行差分放大动作,在非动作时不进行差分放大动作,但在此时,规定的偏置电压施加至内部节点(连接点p6、p7),因此能够抑制基准电压的变动。

63.图3是表示图1的恒压产生电路2的差分放大电路21以及用于保护执行电路13的差分放大电路22的停止动作的定时图。另外,图3表示在设定为阈值电流ith1=ith3,ith2=ith4的情况下的阈值电流的简易设定例的情况。

64.在图3的时间期间t11,使能信号en1、en2被设为h电平,因此差分放大电路21为动作状态,用于保护执行电路13的差分放大电路22成为动作状态,保护电路进行动作。接着,

在时刻t1,从重负载变化为轻负载,从而输出电流iout变小,成为输出电流iout≤ith3,控制电路10中,使能信号en2成为l电平,因此用于保护执行电路13的差分放大电路22的动作停止。此外,使能信号en1被设为l电平,差分放大电路21在偏置电压被施加至差分放大器32的状态下,差分放大器32成为非动作状态。从而,差分放大电路21成为不进行所述的差分放大的状态,但由于被施加着规定的偏置电压,因此抑制经由mos晶体管q22、q23所具有的寄生电容的基准电压的变动。所述的效果在差分放大级22中也同样得到发挥。此时,作为偏置电压的效果,基准电压源的输出电压的变化小,因此输出电流iout的变动也小,用于保护执行电路13的差分放大电路22、以及差分放大电路21不进行误动作,输出电压vout不振荡。

65.如以上所说明的那样,如图2所示由“带电压变动抑制功能的差分放大电路”构成差分放大电路21、22,在各差分放大电路21、22成为停止状态时,差分放大电路21、23的各差分放大器32被施加着规定的偏置电压,因此抑制经由mos晶体管q22、q23所具有的寄生电容的基准电压的变动。此时,作为偏置电压的效果,输出电压vout的电压变动小,因此输出电流iout的变动也小,差分放大电路21、22以及保护执行电路13不进行误动作,输出电压vout不振荡。即,通过抑制基准电压源的输出电压的变化,能够将差分放大器的偏置电压设定得小,能够抑制在模式间输出电压vout的精度劣化,并且防止电源电路在多个模式间持续迁移的误动作。

66.(实施方式的变形例)

67.在以上的实施方式中设置:在用于保护执行电路13的差分放大电路22成为停止状态时,使保护执行电路13所使用的差分放大电路22的动作停止的停止控制电路、或将该差分放大电路22的偏置电压固定的偏置电压产生电路31。本发明不限于此,既可以仅对差分放大电路21设置上述功能电路而不对差分放大电路22设置上述功能电路,也可以不具有根据来自控制电路10的使能信号en2使动作与输出电流相应地停止的功能。

68.在以上的实施方式中,由不带电压变动抑制功能的通常的差分放大电路构成差分放大电路23。本发明不限于此,也可以与差分放大电路21、22同样,由带电压变动抑制功能的差分放大电路构成差分放大电路23。

69.在以上的实施方式中,将mos晶体管q12、q13、mos晶体管q22、q23、mos晶体管q32、q33分别级联连接。本发明不限于此,也可以不级联连接,而分别仅由1个mos晶体管q13、q23、q33构成。

70.(其他变形例)

71.在以上的实施方式中,说明了在恒压产生电路2中使用的差分放大电路21、22,以下针对差分放大电路21、22的变形例1、2、3进行说明。另外,在以下,设为差分放大电路21a、21b、21c,但也可以将它们的结构同样地应用于差分放大电路21以及22。

72.(变形例1)

73.图4是表示变形例1所涉及的差分放大电路21a的结构例的框图。在图4中,针对与图2同样的结构元素附加相同的标号。图4的差分放大电路21a与图2的差分放大电路21、22相比具有以下的差异点。

74.(1)代替偏置电压产生电路31,而具备偏置电压产生电路31a。

75.(2)代替差分放大器32,而具备差分放大器32a。

76.以下,针对差异点进行说明。

77.在图4中,偏置电压产生电路31a构成为具备mos晶体管q11、q13、电流源41、44、以及mos晶体管q41、q42。偏置电压产生电路31a与偏置电压产生电路31相比具有以下的差异点。

78.(1)删除了mos晶体管q12。

79.(2)由mos晶体管q41、q42构成电流镜电路cm1,从而由电流镜电路cm1产生与mos晶体管q13的源极电位对应的偏置电压,并经由开关sw15向连接点p7输出。

80.端子t4被输入的使能信号en1向开关sw1~sw3的各控制端子输入,并且经由逆变器33向开关sw13~sw15的各控制端子输入。

81.根据如上构成的差分放大电路21a,在非动作时,由电流镜电路cm1产生与mos晶体管q13的源极电位对应的偏置电压,并向差分放大器32a的连接点p7输出,由此能够抑制基准电压源的输出电压的变化。

82.(变形例2)

83.图5是表示变形例2所涉及的差分放大电路21b的结构例的框图。在图5中,针对与图2以及图4同样的结构元素附加相同的标号。图5的差分放大电路21b与图4的差分放大电路21a相比具有以下的差异点。

84.(1)代替偏置电压产生电路31a,而具备包含内部基准电压产生电路50以及电压产生电路60的偏置电压产生电路。

85.(2)代替差分放大器32a,具备差分放大器32aa。另外,差分放大器32aa与差分放大器32a相比,代替开关sw15,而具备将电压产生电路60的连接点p22与差分放大器32aa的连接点p6连接的开关sw11。

86.从而,差分放大电路21b构成为具备内部基准电压产生电路50及电压产生电路60、以及差分放大器32aa。以下,针对差异点进行说明。

87.在图5中,内部基准电压产生电路50具备差分放大器51、p沟道mos晶体管q51、以及分压电阻r1、r2,构成为公知的基准电压产生电路。从而,内部基准电压产生电路50基于端子t5被输入的基准电压vref,产生规定的内部基准电压并经由连接点p21向电压产生电路60的mos晶体管q61的源极输出。在此,也可以将连接点p21的电压向该块之外输出,从而作为基准电压使用。

88.电压产生电路60构成为具备p沟道mos晶体管q60~q62、以及n沟道mos晶体管q63、q64。在此,由mos晶体管q51和q60构成电流镜电路cm2。此外,由mos晶体管q61~q64构成电流镜电路。从而,电压产生电路60针对来自内部基准电压产生电路50的恒压,由电流镜电路cm2对输出阻抗进行调整并向差分放大器32aa输出。

89.端子t4被输入的使能信号en1向开关sw1~sw3的各控制端子输入,并且经由逆变器33向开关sw11、sw13、sw14的各控制端子输入。

90.根据如上构成的差分放大电路21b,在非动作时,由电流镜电路cm2产生与mos晶体管q51的漏极电位对应的偏置电压,并向差分放大器32aa的连接点p6输出,由此能够抑制基准电压源的输出电压的变化。

91.(变形例3)

92.图6是表示变形例3所涉及的差分放大电路21c的结构例的框图。图6的差分放大电路21c与图2的差分放大电路21相比具有以下不同点。

93.(1)代替偏置电压产生电路31,而具备包含2个并联晶体管电路70、80以及电流源电路90的电流产生电路。

94.(2)代替差分放大器32,而具备差分放大器32b。

95.以下,针对差异点进行说明。

96.差分放大器32b构成为具备开关sw3、sw13、sw14、sw20、mos晶体管q21、q31、q32、q33、q34、以及电流源43。在此,由mos晶体管q34和电流源43构成输出放大电路。

97.2个并联晶体管电路70、80在mos晶体管q21与电流源电路90之间被相互串联连接。在此,并联晶体管电路70构成为具备2个mos晶体管q71、q72、以及开关sw21。此外,并联晶体管电路80构成为具备2个mos晶体管q81、q82、以及开关sw23。进而,电流源电路90构成为具备2个电流源91、92、以及开关sw25。从而,在使开关sw21~sw25断开时(差分放大器32b非动作时),与使开关sw21~sw25接通时(差分放大器32b动作时)相比流动的电流变小,特别是,在不使差分放大器32b动作时,使该小电流从所述电流产生电路流向差分放大器32b的内部节点(连接点p4、p6、p7),将其动作电位固定,从而抑制基准电压源的输出电压的变化。

98.另外,并联晶体管电路70、80中的与开关连接的mos晶体管分别不限于1个,也可以是多个mos晶体管。

99.在上述的实施方式以及变形例1、2中,在差分放大器32、32a、32aa非动作时,从偏置电压产生电路31、31a以及电压产生电路60将规定的偏置电压分别施加至差分放大器32、32a、32aa的内部的节点,从而将差分放大器32、32a、32aa的该动作电位固定(构成动作电位固定电路),从而抑制基准电压的电位变动。相对于此,在变形例3中,在不使差分放大器32b动作时,使规定的小电流流向差分放大器32b的内部节点(连接点p4、p6、p7)(电流产生电路),将其动作电位固定(构成动作电位固定电路),从而抑制基准电压的电位变动。

100.(进一步的变形例)

101.在以上的实施方式以及变形例中,具备开关sw1~sw25。在此,开关sw1~sw25例如由mos晶体管所构成的半导体开关元件构成。

102.在以上的实施方式以及变形例中,使用了差分放大器32、32a、32b,但本发明不限于此,也可以使用对输入电压进行放大的放大器。

103.工业上的可利用性

104.如以上详述的那样,根据本发明所涉及的恒压产生电路,能够抑制由于经由耦合电容的噪声重叠而产生的基准电压源的输出电压的变化。由此,能够将差分放大器的偏置电压设定得小,抑制在各模式中作为输出电压之差而发生的输出电压的精度的劣化,并且防止电源电路在多个模式间持续迁移的误动作。

105.标号说明

106.1 直流电压源

107.2 恒压产生电路

108.3 输出电容器

109.4 负载

110.10 控制电路

111.11 基准电压产生电路

112.12 监视对象节点

113.13 保护执行电路

114.14 电流源

115.21~23、21a、21b、21c 差分放大电路

116.31、31a 偏置电压产生电路

117.32、32a、32aa、32b 差分放大器

118.33 逆变器

119.41~45 电流源

120.50 内部基准电压产生电路

121.51 差分放大器

122.60 电压产生电路

123.70、80 并联晶体管电路

124.90 电流源电路

125.91~92 电流源

126.p1~p22 连接点

127.cm1、cm2 电流镜电路

128.q1~q82 mos晶体管

129.r1、r2 分压电阻

130.sw1~sw25 开关

131.t1~t5 端子

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1