低压降调节器电路以及产生稳定电压的方法与流程

1.本专利文件中描述的技术大体而言是关于半导体记忆体系统,并且更特定言之,是关于用于半导体记忆体系统的电力管理系统及方法。

背景技术:

2.系统中的记忆体可能经历不作用的期间(例如数分钟、数秒、几分之一秒),在该期间数据并不会写入记忆体或从记忆体中被读取。当记忆体在启用模式时,即便记忆体并未执行写入或读取操作,记忆体仍会汲取电力。为了节省电力,特别是在电力受限的装置(例如以电池供电的装置)中,可将记忆体置于低电力、睡眠或者关闭状态。

技术实现要素:

3.本案的一实施例提供一种低压降调节器电路,包括误差放大运算放大器、反馈分压器以及电源切断开关电路。误差放大运算放大器用以接收参考电压并将反馈电压输出至传输晶体管。反馈分压器连接至误差放大运算放大器、输出电压接脚及接地。电源切断开关电路连接至误差放大运算放大器。电源切断开关电路用以回应于电源切断信号向运算放大器提供额外的电流,以在电源切断模式期间维持输出电压。

4.本案的另一实施例提供一种产生稳定电压的方法,包括:在调节器的运算放大器处接收参考电压,其中参考电压、分压器及运算放大器用以设置输出电压;在晶体管的源极处接收输入电压,其中运算放大器的输出连接至晶体管的栅极;在晶体管的漏极处产生稳定的输出电压;以及回应于电源切断信号,向运算放大器提供电流提升。

5.本案的另一实施例提供一种低压降调节器电路,包括误差放大运算放大器、反馈分压器以及多个额外晶体管。误差放大运算放大器用以接收参考电压并将反馈电压输出至传输晶体管。反馈分压器连接至误差放大运算放大器、输出电压接脚及接地。多个额外晶体管连接至运算放大器以操作于二极管配置中并降低跨多个运算放大器晶体管的电压降,从而稳定化运算放大器输出以维持传输晶体管上的饱和。

附图说明

6.当结合附图阅读时,从以下详细描述可以最好地理解本揭露的各方面。

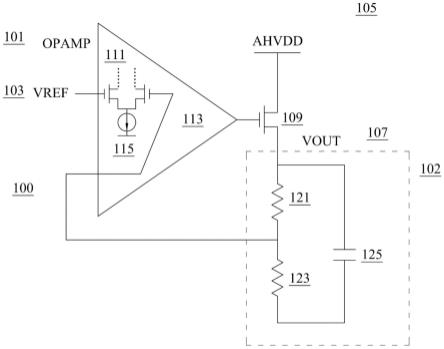

7.图1是描绘根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图;

8.图2a至图2b是描述根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图;

9.图3是描绘根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图;

10.图4是描绘根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图;

11.图5是电路图,描绘了根据一个实施例用于在轨道电源切断模式期间维持至低压降调节器的电力的电力部件;

12.图6是时序图,描绘了根据一个实施例的低压降调节器电路调节到记忆体的电压的电压调节功能;

13.图7是根据一个实施例的用于制造用于低电流电源切断的低压降调节器电路的示例性方法的流程图;

14.图8是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图;

15.图9是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图;

16.图10是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图。

17.【符号说明】

18.100:低压降调节器调节器电路

19.101:运算放大器

20.102:分压器

21.103:参考电压

22.105:模拟高vdd电源

23.107:输出电压

24.109:传输晶体管

25.111:运算放大器晶体管

26.113:运算放大器晶体管

27.115:电流提升器

28.121:第一电阻器

29.123:第二电阻器

30.125:保护电容器

31.200:电路图

32.201:第一p型金属氧化物半导体晶体管

33.203:第二p型金属氧化物半导体晶体管

34.205:电流镜晶体管配置

35.207:保护电路系统配置/保护电路系统

36.209:第一n型金属氧化物半导体晶体管

37.211:第二n型金属氧化物半导体晶体管

38.300:低压降调节器调节器

39.301:保护晶体管

40.303:保护晶体管

41.400:低压降调节器电路

42.401:电源切断开关

43.403:电源切断开关

44.500:电源切断开关电路

45.501:外部电路

46.503:运算晶体管

47.505:运算晶体管

48.507:电流比晶体管

49.509:电源切断信号

50.511:电流比晶体管

51.513:电源切断晶体管

52.515:保护电容器

53.601:avdd

54.603:avdd

55.605:电源切断信号

56.607:负载电压

57.609:vout回应电压

58.610:功率上升

59.611:电压尖峰

60.613:尖峰

61.620:线路调节测试

62.630:负载调节测试

63.640:功率下降

64.700:方法

65.701:步骤

66.703:步骤

67.705:步骤

68.800:方法

69.801:步骤

70.803:步骤

71.805:步骤

72.807:步骤

73.809:步骤

74.900:方法

75.901:步骤

76.903:步骤

77.905:步骤

78.907:步骤

79.1000:方法

80.1001:步骤

81.1003:步骤

82.1005:步骤

83.1007:步骤

84.1009:步骤

85.ahvdd:模拟高vdd

86.c1:保护电容器

87.m0:电流比晶体管

88.m1:电源切断晶体管

89.m2:电流比晶体管

90.opamp:运算放大器

91.pdb:电源切断板

92.vout:输出电压

93.vref:参考电压

具体实施方式

94.以下揭露内容提供了用于实施所提供标的的不同特征的许多不同实施例或实例。以下描述了部件和布置的特定实例以简化本揭露内容。当然,此些仅仅是实例,而并且意欲为限制性的。此外,本揭露案可以在各个实例中重复参考数字和/或字母。该重复是出于简单和清楚的目的,并且其本身并不指示所论述的各种实施例和/或配置之间的关系。

95.作为记忆体低功率/睡眠/停机操作的一部分,电源栅极可用于关闭周边设备及记忆体阵列。当记忆体退出睡眠模式(例如,停机、深度睡眠及轻度睡眠)时,大电源栅极可用于升高记忆体的内部电源电压。过驱动低压降调节器(low dropout regulator,ldo)在实施电源切断操作时可能会经历安全操作区(safe operating area,soa)问题。例如,soa问题可包括掉到低于调节器上的电压阈值,或者在输出端上经历意外的频率回应。某些ldo实施例使用高接地作为中间位准电压以在电源切断模式期间供应偏置。此可导致额外的ldo以提供中间位准电压。

96.过驱动ldo调节器可能在电源切断期间维持soa操作范围中经历困难。可以实施利用较大vdd的过驱动ldo,以确保调节晶体管维持饱和状态。此类ldo可用以基于参考电压将电压维持在指定范围内,并利用电流提升或模拟高压vdd连接来供电。该些系统可包含至系统的配电板的额外连接以用于电源切断。本文描述了用于在电源切断期间在维持低电流的同时维持soa操作范围的系统及方法。以此种方式,可以维持稳定化的输出电压,直到输入电压小于输出电压加上压差。通常,ldo被设计为具有低压差。在实施例中,该方法可包括在不利用额外的高接地(high ground,hg)中间位准电压的情况下,调节具有非常接近的输入电压(例如,小于1v)的电路的输出电压的方法。

97.在过驱动ldo的vdd是最大持续电压的大于两倍的电路配置中,设计可利用多于一个hg中间位准电压,相应的妥协可能增加面积/功耗。此种特性亦可能增加在提供此类hg ldo方面的协同模拟复杂性及系统级复杂性。

98.某些实施例可赋能可在没有hg电源的情况下实施的电路。如本文所述,可以通过针对规格指定适当的电流,随后修改设计以提供电源切断能力来设计电路。该些实施例可被设计为以最小电流满足soa区域,随后提升电流以满足期望的电气效能。此种用于稳定化输出电压的方法可减少对提供hg电压的额外ldo的需求。没有hg电压的电路可产生具有减

少的面积损失(area penalty)的稳定化的输出电压,并且不需要用额外的电压位准来协同模拟电路操作。

99.在一个示例性实施例中,电路以低电流(例如,极低电流)操作并且保持在soa区域中。该电路包括至电流源的连接,例如金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet)电流镜。电流源经由与受电源切断(power down,pd)信号控制的晶体管开关连接,提供额外的电流来提高效能。当电路转换到电源切断模式时,电路仍然通过从电流源汲取额外电流来发挥功能。以此种方式,电路以接近最小的电流要求操作,以在正常操作期间维持soa操作范围,并且在电源切断模式及转换至电源切断模式期间以稍大的电流要求操作。

100.针对特定设计标准,进一步的过驱动ldo调节器系统可包括运算放大器(operational amplifier,opamp)。此外,用于在电源切断期间维持电压调节的方法可使用opamp来比较输出电压。例如,opamp可用于提供电压增益、电压调节、调整相位余裕、驱动电容性负载、作为带宽滤波器操作、提升带宽、或以其他方式建立电气标准。本文所述的示例性调节器电路是过驱动ldo调节器。过驱动ldo调节器用调节器可用的电压驱动晶体管达到饱和。通常,ldo被设计为最小化输入与输出之间的电压差,称为压差。以此种方式,输入电压可以下降(例如,从2.0v至1.6v),而输出电压保持恒定(例如,1.2v)。压差可以是跨控制晶体管或传输晶体管两端的压差。传输晶体管的压差可能超过调节器的最大设计压差,以将输出电压适当地维持在设计范围内。该系统可配置有额外的晶体管以降低传输晶体管的源极处的输入电压,从而维持输出电压上的soa操作范围。例如,有源负载mosfet配置可经由输入接脚(例如,模拟高vdd)提供额外的电流。调节器电流可以经由传输晶体管的漏极上的模拟高vdd连接来驱动。若模拟高vdd上的电压大于设计的最大电压阈值,则额外的晶体管将被饱和并作为电压递降操作。此种电压递降可由二极管连接的互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)电路执行。opamp接收参考电压,该参考电压将输出电压设置在设计的电压范围内。

101.在其他实施例中,ldo调节器系统可操作以在电源切断期间调节输出电压。特别地,ldo调节器可以用以在电源切断期间最小化电压尖峰,控制输出带宽,并调整潜时。ldo调节器晶体管可操作以增加在电源切断模式与正常操作模式之间切换的潜时,从而减少模式转换期间输出电压上的电压尖峰。

102.在另外的实施例中,将电流提升以满足电气效能要求。电流提升可以在opamp处提供,opamp基于来自电源切断板的外部控制电压提供额外的电流。可能需要额外的电流来在维持带宽、驱动能力及降低的输出电压波动的同时保持soa操作范围。电流源可以基于电源切断信号操作,使得电流源在正常操作期间不操作。此外,可以基于电源切断单元内的晶体管通道比来指定供应给opamp的电流的量。在其他实施例中,可能需要额外的电流来保持正常的操作功能特性,诸如驱动能力、增益及相位余裕。由于该电路被设计为在非常低的电流下操作,因此只有在需要维持soa操作范围时才会汲取额外的电流,并维持大约最小的电流泄漏。

103.图1是图示示例性低压降调节器电路的图,该低压降调节器电路可以例如是基于本文所述的设计及制造方法的电路设计。ldo调节器电路100的该示例实施例包括opamp 101、第一电阻器121、第二电阻器123、保护电容器125、电流提升器115、第一opamp晶体管

111、第二opamp晶体管113及传输晶体管109。ldo调节器电路100包括模拟高vdd(analog high vdd,ahvdd)电源105及输出电压(vout)107。传输晶体管109、第一电阻器121、第二电阻器123及opamp 101用作调节模块。特别地,该些部件形成线性电压调节器,其中电阻器121、123用作分压器102,并且opamp 101以非反相opamp方案使用。本实施例中的vout 107可以基于电阻器121、123的电阻比及参考电压(vref)103来设计。输出电压是vref 103乘以第一电阻器121加上第二电阻器123与第二电阻器123的电阻比。调节模块亦包括保护电容器125,该保护电容器用于调节vout 107的瞬态回应。

104.opamp 101配置有连接至vref 103的非反相输入、连接在第一电阻器121与第二电阻器123之间的节点处的反相输入,以及连接至传输晶体管109的栅极的输出。opamp 101包括第一opamp晶体管111、第二opamp晶体管113及电流提升器115。在其他实施例中,opamp 101将包括连接至第一opamp晶体管111及第二opamp晶体管113的漏极的额外保护电路系统。例如,该电路可以被设计成在opamp晶体管111、113的源极与漏极之间具有大于1伏的压差。在该些实施例中,可以利用额外的保护电路系统,诸如有源负载mosfet或电流镜电路配置,来确保opamp晶体管111、113上有足够的电流供应。基于opamp 101的电压最大值、瞬态回应特性及功率损耗,在电路设计中可以利用不同的opamp 101。opamp 101可以例如是反相放大器。

105.传输晶体管109配置有连接至ahvdd电源105的漏极、连接至vout 107的源极,及连接至opamp 101的输出的栅极。ahvdd电源105可以具有电压范围(例如,+/-10%)。ahvdd电源105为ldo调节器供电,并且可以连接至外部配电板。在该些实施例中,传输晶体管109通常在导通状态下操作,使得电流将从漏极流向源极。当vout 107低于vref 103时,传输晶体管109允许电流流动,以将vout 107驱动至设计电压。该些实施例利用过驱动ldo调节器模块,其中ldo的vdd实质上大于最大持续电压(例如,两倍)。

106.ldo调节器电路100利用opamp 101、传输晶体管109及电阻器121、123来调节vout 107,而无需配置额外的ldo调节器来建立hg(中间接地)电压。ldo调节器的特征在于输入电压与输出电压之间的低压差,与此同时维持稳定化的输出电压(vout 107)。由于该设计不利用额外的ldo调节器,因此其已经减少了面积及电力成本。电流提升器115提供额外的电流,但是取决于用于维持电气效能的soa要求,可以以非常低的电流操作。电流提升器115基于控制电压提供电流,该控制电压可以是来自外部装置的电源切断信号。外部装置可例如是配电板。在此种配置中,电流提升器115确保电路在电源切断期间保持在soa操作范围内,具有非常小的泄漏电流。

107.vout 107被设置为设计电压,并且被ldo调节器100保持至近似设计电压。基于电阻器121、123的电阻比及vref 103来计算设计电压。若vout 107大于设计电压,则电流将从vout 107流过第一电阻器121,另外,由于误差放大器调节跨传输晶体管109两端的电压降,所以更少的电流将从ahvdd电源105流过传输晶体管109。从vout 107流过第一电阻器121的电流的量基于vout 107与vref 103之间的电压差。若vout 107小于设计电压,则电流将从ahvdd电源105流过传输晶体管109,以将电压拉高至设计电压。以此种方式,vout 107由ldo调节器100调节。

108.vout 107进一步连接至保护电容器125。保护电容器125连接在vout 107与接地之间。输出电容器125控制瞬态回应,影响输出电压波动,并且基于等效串联电阻及频率来调

节负载瞬态回应。保护电容器125是用于维持安全操作特性的保护电路系统的实例。特别地,保护电容通过允许某些频率流过电容器到达接地来影响输出的带宽及相位余裕。

109.图2a至图2b是描述根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图。图2a与图1相同,其中用圆圈标识opamp晶体管111、113,以便理解改写opamp晶体管可能是图2b中相同的opamp晶体管。图2b类似于图2a中的电路并描绘了opamp晶体管111、113上的电压降及电流限制。电路图200描绘了opamp晶体管111、113的压降区(vds),该压降区具有包括电流镜晶体管配置205及示例性保护电路系统配置207的额外电路系统。电流镜晶体管配置205亦包括第一p型金属氧化物半导体(p-type metal oxide semiconductor,pmos)晶体管201及第二pmos晶体管203。因为跨第一pmos晶体管201两端的电流设定第二pmos晶体管203的电流,所以第一pmos晶体管201可以被称为偏置晶体管。保护电路系统配置207包括第一n型金属氧化物半导体(n-type metal oxide semiconductor,nmos)晶体管209、第二nmos晶体管211、至电压源(例如,ahvdd 105)的连接,以及至opamp晶体管111、113的漏极的连接。此种配置是cmos差分放大器配置。

110.电流镜晶体管配置205确保当两个晶体管的电压差及栅极宽度匹配时,跨第一pmos晶体管201两端的电流与跨第二pmos晶体管203两端的电流相同。此允许第一pmos晶体管的漏极处的输入设置跨opamp晶体管111、113两端的电流,以及设置第一pmos晶体管201及第二pmos晶体管203的栅极上的电压,以将晶体管转换至导通状态。然而,在一些情况下,跨opamp晶体管111、113两端的电压降将大于ldo调节器电路100被设计来维持的量。同样,当输入上的电压太接近或小于输出上的电压时,电路可能无法产生设计的输出电压。当电压或电流可用于传输晶体管109时。如图2b所示,跨opamp晶体管的漏极至源极两端的电压降可大于soa,并且因此将利用额外的保护电路系统来确保稳定的vout 107。

111.电流镜晶体管配置205配置为第一pmos晶体管201的栅极是连接至第二pmos晶体管的栅极及第一pmos晶体管201的漏极。第一pmos晶体管201及第二pmos晶体管203的源极连接至接地。第一pmos晶体管201的漏极连接至用于设置设计参考电压及电流(例如vref 103)的一些外部电路。第一pmos晶体管201的漏极可以连接至外部电流源,诸如下面在图5中描述的电源切断开关500。第二pmos晶体管203的漏极连接至opamp晶体管111、113的源极。

112.保护电路系统207配置为第一nmos晶体管209的栅极是连接至第二nmos晶体管211的栅极及第一nmos晶体管209的源极。第一nmos晶体管209及第二nmos晶体管211的漏极连接至电流源,诸如ahvdd 105。第一nmos晶体管209的漏极连接至第一opamp晶体管111的漏极。漏极nmos晶体管209的源极连接至第二opamp晶体管113的漏极。保护电路系统207操作以维持opamp晶体管的漏极上的适当电压,然而,当输入电压超出soa操作范围时,可以利用额外的保护电路系统。nmos晶体管209、211的源极连接至电压源,诸如ahvdd 105。

113.图3是描绘根据一个实施例的用以在电源切断期间维持稳定输出的低压降调节器电路的电路图。图3类似于图2b,不同之处在于图3中的电路亦包括保护电路系统。特别地,该电路包括用于第一opamp晶体管111的第一保护晶体管301及用于第二opamp晶体管113的第二保护晶体管。

114.图3描绘了在一个实施例中添加了保护晶体管301、303的ldo调节器300的电路图实施例。在该实施例中,在没有额外保护晶体管301、303的电路中,opamp晶体管111、113的

漏极与源极之间的电压降超过了ldo调节器被设计来处理的最大电压。因此,调节器超出了soa操作范围。ldo调节器300包括用以维持soa操作范围的额外保护电路系统。

115.第一保护晶体管301被配置为以其栅极连接至其漏极,以其漏极及栅极连接至第一opamp晶体管111的漏极,并且以其源极连接至第一nmos晶体管209的漏极。在此种配置中,只有当栅极上的电压小于阈值电压时,晶体管才会进行传输。由于栅极连接至opamp晶体管的漏极,此意味着只有当opamp晶体管的漏极处的电压低于设定值,特别是soa操作范围时,晶体管才会进行传输。此是二极管配置的nmos晶体管,该二极管配置的nmos晶体管作为电压降操作并且仅允许电流从第一nmos晶体管209向下流到第一opamp晶体管111。

116.第二保护晶体管303被配置为以其栅极连接至其漏极,以其栅极及漏极连接至第二opamp晶体管113的漏极,并且以其源极连接至第二nmos晶体管211的漏极。在此种配置中,只有当栅极上的电压小于阈值电压时,晶体管才会进行传输。由于栅极连接至opamp晶体管的漏极,此意味着只有当opamp晶体管的漏极处的电压低于设定值,特别是soa操作范围时,晶体管才会进行传输。此是二极管配置的nmos晶体管,该二极管配置的nmos晶体管作为电压降操作并且仅允许电流从第二nmos晶体管211向下流到第二opamp晶体管113。

117.在其他实施例中,额外保护电路系统可用于传输晶体管109。额外的电路系统可以向传输晶体管的栅极提供额外的电流,以确保其保持饱和状态以使电流流动。通常,ldo调节器被设计为跨传输晶体管109两端具有非常低的电压降,因此额外晶体管配置,诸如在ldo调节器电路300中论述的额外晶体管配置,可操作以确保传输晶体管的漏极与源极之间具有低电压降的soa操作范围。

118.图4是附图示例性低压降调节器电路的图,该低压降调节器电路可以例如是基于本文所述的设计流程的电路设计。图4所示的实例ldo调节器电路400与图1所示的ldo调节器电路100相同,区别在于图1所示的实例100利用电流源电路,该电流源电路具有配置在电流提升模块115及vout 107处的额外电流源及电源切断开关电路401、403。第一电流源及电源切断开关电路401用以从电流提升模块115的输入至opamp 101内的接地。第二电流源及电源切断开关电路603从输出电压107及接地连接。电流源及电源切断开关电路401、403连接至来自外部配电板的外部电源切断信号。第一电流源及电源切断开关电路401经由电流源晶体管配置将电流源115连接至接地。回应于电源切断信号,第一电流源及电源切断开关电路401在电源切断期间向opamp提供额外的电流。

119.第二电流源及电源切断开关403经由电流源晶体管配置将vout 107连接至接地。回应于电源切断信号,第二电流源及电源切断开关403可以在电源切断期间提供额外的电流。在一些实施例中,opamp的电流源及输出电压皆是连接至相同的电源切断信号。电流源及电源切断开关电路401、403操作以在opamp 101及vout 107处提供额外的电流来提高效能。

120.电流源及电源切断开关401、403被接通,使得调节器可以继续在电源切断模式下操作。当电源切断开关401、403从外部装置(例如,电源切断板)接收到电源切断信号时,该些电源切断开关被接通,使得电流流过开关。在一些实施例中,电源切断开关401、403在正常功能期间处于关断状态,使得电流不流动。

121.图5是图示具有电源切断开关的电流源的示例性电路的图,该电路可以例如是基于本文所述的设计流程的电路设计。该示例性实施例是用于电源切断开关500的电路,该电

源切断开关可以例如是如图4中在ldo调节器400处描绘的电源切断开关401、403。电源切断开关电路500包括电源切断晶体管(m1)513、第一电流比晶体管(m0)507、第二电流比晶体管(m2)511、保护电容器(c1)515、第一运算晶体管503、第二运算晶体管505及额外的外部电路501。在一些实施例中,外部电路包括额外的保护电路。该电路包括至电源切断板(power down board,pdb)的额外连接,该pdb提供电源切断信号509。

122.第一运算晶体管503配置为以其漏极连接至外部电路501,以其栅极连接至参考电压,并且以其源极连接至电流比晶体管(m0)507、晶体管(m2)511的漏极。第二操作晶体管505配置为以其漏极连接至外部电路501,以其栅极连接至操作输出端,并且以其源极连接至电流比晶体管507、511的漏极。运算晶体管503、505可以是opamp晶体管111、113,如在图4中的ldo调节器电路400中所示。

123.电源切断晶体管(m1)513配置为以其漏极连接至第二电流比晶体管(m2)511的源极,以其栅极连接至来自电源切断板(pdb)509的外部电源切断信号,并且以其源极连接至接地。电源切断晶体管(m1)513在电路的正常操作期间是导通的,并且当它从外部电源切断板(pdb)接收到电源切断信号509时关断。以此种方式,当电源切断晶体管(m1)513接收到电源切断信号509时,电流不会流过该电源切断晶体管。因此,在电源切断期间,电流源将是高的,使得额外的电流被提供至外部电路系统501。在一些实施例中,当电源切断晶体管(m1)513是导通的时,电流继续流过运算晶体管503、505,使得电路继续作为电流源操作。在其他实施例中,电源切断晶体管(m1)513将第二电流比晶体管(m2)511的源极连接至接地,使得电源切断开关500在正常操作期间不作为电流源操作。以此种方式,电源切断开关仅在电源切断模式期间作为电流源操作,以维持传输晶体管109上的误差放大opamp饱和并稳定化vout 107。

124.与第二电流比晶体管(m2)511相比,第一电流比晶体管(m0)507的通道宽度与压降之比确定了提供给外部电路系统501的额外电流相对于参考电流的因数。该电流源电路可以例如基于穿过第一运算晶体管503的参考电流及电流比晶体管(m0)507、晶体管(m2)511的通道宽度比,经由第二运算晶体管505向外部电路系统501提供电流。在第二电流比晶体管(m2)511的通道宽度显著大于第一电流比晶体管(m0)507的通道宽度的设计中,电源切断晶体管(m1)513可以更小。电流比允许电路以低电流成本维持ldo调节器电压。

125.保护电容器(c1)515连接在第二电流比晶体管(m2)511的源极与接地之间。并非在所有实施例中都利用保护电容晶体管,而使保护电容晶体管可操作以增加在电源切断模式与正常功能之间切换的潜时。增加的潜时允许减少的电压尖峰,此基于设计规范可为有益的。

126.图6是时序图,描绘了根据一个实施例的低压降调节器电路调节到记忆体的电压的电压调节功能。图6描绘了图4的时序图以显示了电流提升电源切断单元,诸如图5所示的电流提升电源切断单元。该图在横轴上描绘了各种输入信号的电压及电流以及随时间推移回应于该些信号的输出电压。时序图描绘了输入电压信号avdd 601、603的功率、电源切断信号605、负载电压607及在vout回应电压609处的输出电压回应。测试ldo调节器电路在功率上升610之后、线路调节测试620期间、负载调节测试630期间以及在功率下降640之前,在已经切换了电源切断信号605之后的效能。电源切断信号可以例如是由电源切断板产生并供应给图5中的电源切断晶体管(m1)513的相同的电源切断信号509。输入电压avdd可以例

如是图1或图4中的ahvdd 105。

127.在该实施例中,vout 107被稳定化至为1.2v的输出电压。在输入信号范围为1.62v至1.98v时,ldo调节器电路100能够在vout 107产生1.2v的输出。该调节操作由1.98v的高端avdd 601及1.62v的低端avdd 603显示。在正常操作期间,vout回应电压609维持在1.2v。vout分别在输入电压的功率上升610及输入电压的功率下降640期间类似地上升及下降。

128.输入电压短暂地跳跃0.1v,而vout回应电压609回应没有变化。此表明ldo调节器有效地稳定化了输出电压。

129.时序图另外描绘了在电源切断期间保持稳定输出电压的实施例能力。电源切断信号从逻辑高状态切换至逻辑低状态,以发信号通知电源切断。此禁用了电源切断晶体管,例如电源切断晶体管(m1)513,此导致了vout回应电压609上的电压尖峰611。此将触发电源切断开关作为电流源操作。可以通过经由在保护电容器(例如图5中的保护电容器(c1)515)上的小电源切断晶体管或额外电容引入额外潜时来减少电压尖峰。类似地,当电源切断信号切换回逻辑高状态时,电源切断晶体管被赋能,导致输出电压中的尖峰613为约1.1v。当电源切断开关导通并且电路处于正常功能(例如,非电源切断模式)时,该电源切断开关500不作为电流源操作。

130.在输出电压下测试负载调节,此时存在大于输入电压的负载电压。负载电压可能导致输出电压中的微小尖峰,此可以由保护电容器(诸如图1及图4中的保护电容器125)来调整。

131.图7是根据一个实施例的用于制造用于低电流电源切断的低压降调节器电路的示例性方法的流程图。图7的步骤是为了便于理解而关于结构提供的,但是应当理解的是,该些步骤可以使用各种结构来执行。在用于制造ldo调节器电路的示例性方法700中,通过以下方式来配置ldo调节器电路设计:首先将调节器设计成在低电流下在soa操作范围内操作(步骤701)。第二,将电流提升器添加到ldo调节器电路设计,使得电流提升器回应于电源切断信号(步骤703)。最后,制造具有电流提升器的ldo调节器电路设计(步骤705)。

132.图7的方法可用于产生过驱动ldo调节器,例如在图1至图5中在ldo调节器电路100、电路图200、ldo调节器300、400、电源切断开关500处描述的那些。示例性ldo调节器包括用于驱动电容性负载、滤波、维持相位余裕或提供增益的电路(例如,示例性电路ldo调节器电路100、电路图200、ldo调节器300、400)的调节器。调节器可以在具有电源切断开关电路(例如,示例性电路ldo调节器400、电源切断开关500)的配置中操作,以在电源切断模式期间维持电路功能。首先,ldo调节器电路设计被设计为在soa区域中操作(步骤701)。该步骤可以经由多次叠代来完成,因为需要额外的电流或保护电路系统来满足效能规格。接下来,根据需要经由电流提升增加额外的电流,以确保电路在电源切断模式及模式切换期间维持在soa操作范围内(步骤703)。可以使用设计表规范、使用者量测、模拟电路或老化模型来计算soa区域。在一些实施例中,运算放大器与晶体管、电阻器及电容器结合利用,以作为过驱动ldo调节器操作,而不需要中间位准电压。多个电源切断开关可以连接至电流源及输出电压,以允许电路在电源切断模式期间操作。该等开关用以回应于来自外部装置(例如,配电板)的电源切断信号。

133.此外,保护电路系统可以结合到设计方法中,以确保输出电压及电气效能保持在soa区域中。保护电路可包括连接至vdd、输出电压、运算放大晶体管及其他部件的额外晶体

管及电容器。例如,可以用保护电路系统来制造电路,其中从漏极至源极的电压大于电路可以其他方式调节以维持soa操作范围的电压(例如,大于1.0v)。该保护电路系统可以包括如下面图3所述的晶体管配置。

134.参照图1,ldo调节器电路100可以基于图7中700处描述的方法制造。ldo调节器电路100被设计为结合制造方法的第一步骤(步骤701)在低电流下操作。该电路包括电流提升器115,该电流提升器回应于电源切断信号,如方法的步骤二(步骤703)中所述。该电路可以利用额外元件,诸如保护电容器125,来维持soa操作范围。例如,保护电容器125修改瞬态回应以维持soa操作范围(步骤701)。将设计的ldo调节器电路与额外保护电路一起制造(步骤705)。

135.在另外的实施例中,用于制造ldo调节器700的方法包括将调节器设计为在非常低的电流下操作,而不使用中间接地电压。该方法包括产生ldo调节器电路设计,该ldo调节器电路设计用以以维持安全操作条件所需的近似最低的电流在soa操作范围内操作(步骤701)。接下来,该调节器被设计为包含一个电流提升模块,该模块连接至电源切断信号。该电路是使用ldo调节器设计及电流升压来制造的。电源切断信号可以导致电流源在电源切断模式(步骤703)期间提供额外的电流。电源切断信号通常外部地产生。在一些实施例中,电路被设计为在电源切断模式(步骤705)期间发挥功能。特别地,在电源切断期间,输出电压维持在设计电压值。该些实施例可以利用保护电路系统来跨较大的输入电压波动维持输出电压。此外,并联电容器及晶体管可以用作保护电路系统,以减少电源切断期间的电压尖峰。

136.参照图4,ldo调节器电路400可以基于图7中700处描述的方法制造。ldo调节器电路400包括传输晶体管109、分压器102及opamp 101,它们被设计为结合制造方法700的第一步骤在低电流下操作。该电路另外包括电流提升器115,该电流提升器回应于电源切断信号,如设计方法的步骤二(步骤703)中所述。此外,该电路连接至电源切断开关401、403,该些电源切断开关回应于电源切断信号,如设计方法的步骤二(步骤703)中所述。该电路被设计为使得opamp 101及传输晶体管109将在电源切断期间继续操作,如方法的第三步骤(步骤705)中所述。

137.图8是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图。图8的步骤是为了便于理解而关于结构提供的,但是应当理解的是,该些步骤可以使用各种结构来执行。示例性方法800包括在调节器的opamp处接收参考电压,其中该参考电压、分压器及该opamp用以设置输出电压(步骤801)。此外,在晶体管的漏极处接收输入电压,其中opamp的输出连接至晶体管的栅极(步骤803)。接下来,基于保护电路系统来调整opamp晶体管或传输晶体管的漏极上的电压,以维持soa操作范围(步骤805)。类似地,基于输出电压与接地之间的电容器来调节输出电压的瞬态回应(步骤807)。当保护电路系统适当地维持soa操作范围并且输入电压在ldo调节器能够操作的范围内时,此在晶体管的漏极上产生稳定的输出(步骤809)。

138.示例性方法旨在以非常低的电流提供稳定化的输出,并且不需要额外的中间接地电压。此减少了调节器电路的面积损失,并且防止了在不同电压位准下进行协同模拟的需要。类似地,保护电路系统可以是二极管配置的nmos晶体管,以降低opamp晶体管的漏极上的电压并确保跨opamp晶体管两端的电压降不太高(例如,大于1.0v)。此可以允许跨传输晶

体管两端的电压降小于0.5v。例如,在图4以及图6的时序图中所描述的示例性电路具有为1.68v的输入电压及为1.2v的输出电压。

139.该示例性方法可以由图1中的ldo调节器电路100来执行。在该电路中,误差放大opamp 101配置为连接至参考电压103、分压器102,并设置输出电压。输入电压ahvdd 105在传输晶体管109的栅极处被接收,并且基于参考电压、分压器上的电阻值来设置跨晶体管两端的压降的量。此是因为误差放大opamp 101的输出调节传输晶体管109的栅极上的电压。以此种方式,输出电压vout 107可以被设置在稳定化的点处,而不需要额外的hg电压位准。另外,如图3中的电路图300处所示,当漏极上的电压大于用于没有该些晶体管的设计的soa操作范围时,额外的保护晶体管301、303可以作为二极管来操作,以降低opamp晶体管111、113的漏极上的电压。

140.图9是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图。图9的步骤是为了便于理解而关于结构提供的,但是应当理解的是,该些步骤可以使用各种结构来执行。示例性方法900包括在调节器的opamp处接收参考电压,其中该参考电压、分压器及该opamp用以设置输出电压(步骤901)。此外,在晶体管的漏极处接收输入电压,其中opamp的输出连接至晶体管的栅极(步骤903)。ldo调节器电路在晶体管的漏极处产生稳定化的输出电压(步骤905)。最后,通过回应于电源切断信号向opamp提供电流提升,在电源切断期间维持输出电压(步骤907)。

141.该示例性方法可以由图4中的ldo调节器电路400来执行。在该电路中,误差放大opamp 101配置有电流源,以在输出电压107下向opamp晶体管111、113供应额外电流。在该实施例中,电流源电路是电源切断开关。当电流供应电路接收到电源切断信号时,电源切断开关供应电流。参照图5,此可以在电源切断晶体管(m1)513处执行,该电源切断晶体管用以从外部配电板509接收电源切断信号。

142.图10是根据一个实施例的用于稳定化用于记忆体的调节电路中的输出的示例性方法的流程图。图10的步骤是为了便于理解而关于结构提供的,但是应当理解的是,该些步骤可以使用各种结构来执行。图10的示例性方法类似于图9,不同之处在于ldo调节器电路进一步调整保护电路系统处的输入电压以在电源切断期间维持设计目标,并且电容器调节在正常操作模式与电源切断模式之间切换的潜时。

143.示例性方法1000包括在调节器的opamp处接收参考电压,其中该参考电压、分压器及该opamp用以设置输出电压(步骤1001)。此外,在晶体管的漏极处接收输入电压,其中opamp的输出连接至晶体管的栅极(步骤1003)。ldo调节器电路在晶体管的漏极处产生稳定化的输出电压(步骤1005)。电流源电路,诸如电源切断开关,接收电源切断信号,该电源切断信号触发电路作为电流源操作(步骤1007)。此允许ldo调节器在电源切断期间维持输出电压。最后,通过增加在正常操作模式与电源切断模式之间切换的潜时,减少输出电压处的电压尖峰(步骤1009)。参照图5,此可以由与电源切断晶体管(m1)513并联配置的保护电容器(c1)515来执行。

144.根据一些实施例,提供了用于ldo调节器的系统及方法,该系统及方法在不使用中间接地电压的情况下维持稳定化的输出电压。ldo调节器包括ldo模块、电流提升模块及配置为分压器的电阻器。ldo调节器用以在soa操作范围内操作。soa的操作范围是基于模拟、直接量测或老化模型设计的。为了维持soa操作范围,电路可设计有额外的保护电路系统,

该额外的保护电路系统被配置为opamp晶体管的漏极或传输晶体管的漏极。保护电路系统例如可以是电压递降电路、电流镜、二极管连接的cmos、或mosfet有源负载电路。此外,可以在输出电压接脚与接地之间配置电容器,以调节输出电压的瞬态回应。该电路利用电流提升模块,诸如电流镜,以形成cmos差分放大器。该电路可以另外利用以二极管配置配置的晶体管来调节跨opamp晶体管两端的压降。该电路在接收到电源切断信号时切换至电源切断模式。根据一些实施例,为具有带宽考虑的输出提供系统及方法,使得电容器被配置在输出电压与接地之间。

145.在另一个实施例中,提供了用于ldo调节器的系统及方法,该系统及方法在不使用中间接地电压的情况下维持稳定化的输出电压。ldo调节器包括ldo模块、电流提升模块及配置为分压器的电阻器。ldo模块包括误差放大opamp、至参考电压的连接、以及传输晶体管。ldo调节器用以在soa操作范围内操作。该电路设计有至电源切断开关的额外连接,该电源切断开关回应于电源切断信号而作为电流源操作。电源切断开关向误差放大opamp提供额外电流,以确保传输晶体管保持饱和并在电源切断期间维持输出电压。此外,电容器可被配置在电源切断开关内,以调整在正常操作模式与电源切断模式之间切换的潜时,从而减少电压尖峰。

146.在另一个实施例中,描述了用于经由ldo调节器维持稳定化的输出电压的系统及方法。调节器被设计为以保持在soa操作范围内所需的近似最小电流操作。该电路包括ldo调节器、电流提升器、电源切断开关、及用于电源切断信号的至配电板的连接。该电路被设计为使得电流提升器在设计的操作期间提供额外的电流来提高效能,以维持soa操作范围。电源切断开关用以限制提供给opamp的额外电流及输出电压,使得仅在电源切断模式期间提供额外电流。当电源切断开关接收到电源切断信号时,发信号通知电源切断模式。此外,当需要在电源切断模式期间及在各种模式之间切换时维持soa操作范围时,电流提升器可操作来提供额外的电流。此种方法通常涉及在非常低的电流下检查电路操作的多次叠代,以确保在正常功能、设计的操作、电源切断模式及模式改变期间满足soa操作范围。若电路不在soa操作范围内,则可以经由电流源来提供额外的电流。或者,可以基于晶体管及opamp特性进行设计变更。在一些实施例中,利用额外的保护电路系统来增加电源切断期间功率尖峰的潜时。在其他实施例中,保护电路系统降低opamp晶体管或调节晶体管的漏极处的电压。

147.本案的一实施例提供一种低压降调节器电路,包括误差放大运算放大器、反馈分压器以及电源切断开关电路。误差放大运算放大器用以接收参考电压并将反馈电压输出至传输晶体管。反馈分压器连接至误差放大运算放大器、输出电压接脚及接地。电源切断开关电路连接至误差放大运算放大器。电源切断开关电路用以回应于电源切断信号向运算放大器提供额外的电流,以在电源切断模式期间维持输出电压。

148.在一实施例中,电流以近似最小操作电流操作,以在不处于电源切断模式时保持设计规格。

149.在一实施例中,在电压轨的电源切断期间,电源切断信号由外部电源切断板传输至电源切断开关。

150.在一实施例中,低压降调节器电路还包括在输出电压与接地之间的多个电容器,以设置输出电压的带宽。

151.在一实施例中,电源切断开关电路还包括一对晶体管,该对晶体管用作电流镜以向误差放大运算放大器提供额外的电流。

152.在一实施例中,电源切断开关电路还包括电容器,电容器是在用作电流镜的该对晶体管中的其中一个晶体管的源极与接地之间,以增加切换到电源切断模式的潜时。

153.在一实施例中,电源切断开关电路还包括禁用晶体管,禁用晶体管与用作电流镜的该对晶体管中的其中一个晶体管串联并且用以接收电源切断信号,其中当禁用晶体管处于关断状态时,电源切断开关正在供电。

154.在一实施例中,电源切断开关电路连接至输出电压接脚,以在电源切断期间将额外的电流驱动至电压输出中。

155.本案的另一实施例提供一种产生稳定电压的方法,包括:在调节器的运算放大器处接收参考电压,其中参考电压、分压器及运算放大器用以设置输出电压;在晶体管的源极处接收输入电压,其中运算放大器的输出连接至晶体管的栅极;在晶体管的漏极处产生稳定的输出电压;以及回应于电源切断信号,向运算放大器提供电流提升。

156.在一实施例中,运算放大器在电源切断过程期间维持低压差调节器上的输出电压,直到输入电压下降至低于阈值电压。

157.在一实施例中,由电流提升提供给运算放大器的额外电流提升通过电源切断单元内的电流镜晶体管的电压降及通道宽度比建立。

158.在一实施例中,电流提升装置包括在电流镜晶体管的源极与接地之间的多个额外电容器,以将电源切断模式切换的潜时增加设计量,从而将输出电压上的电压尖峰降低至低于设计量。

159.在一实施例中,方法还包括透过在输出电压与接地之间的电容器引导电流的特定频率,以调节输出电压的瞬态回应。

160.在一实施例中,方法还包括二极管连接晶体管配置,二极管连接晶体管配置连接至运算放大器晶体管以确保运算放大器电压降保持在操作区域内,从而维持电压输出。

161.在一实施例中,方法还包括在指定模式期间提供电流提升;其中指定模式涉及维持驱动能力、最大电压尖峰、增益、相位余裕或带宽。

162.在一实施例中,调节器被设计为以近似正常操作所需的最小电流操作,并且电流提升操作为将电流增加小增量,以维持经由指定模式及电源切断模式进行的操作。

163.本案的另一实施例提供一种低压降调节器电路,包括误差放大运算放大器、反馈分压器以及多个额外晶体管。误差放大运算放大器用以接收参考电压并将反馈电压输出至传输晶体管。反馈分压器连接至误差放大运算放大器、输出电压接脚及接地。多个额外晶体管连接至运算放大器以操作于二极管配置中并降低跨运算放大器晶体管的电压降,从而稳定化运算放大器输出以维持传输晶体管上的饱和。

164.在一实施例中,低压降调节器电路还包括额外电容器,额外电容器连接在输出电压与接地之间,以调节输出带宽及相位余裕。

165.在一实施例中,低压降调节器电路还包括电流源,电流源被设计为在指定模式期间向运算放大器提供额外电流,以维持输出电压上的电压及频率条件;其中电流源回应于外部信号以指示指定模式。

166.在一实施例中,指定模式包括电源切断模式、电压驱动模式或开关模式。

167.先前概述了若干实施例的特征,使得本领域技艺人士可以更好地理解本揭露的各态样。本领域技艺人士应当理解,他们可以容易地使用本揭露作为设计或修改其他制程和结构的基础,以实现与本文介绍的实施例相同的目的及/或实现与本文介绍的实施例相同的优点。本领域技艺人士亦应当认识到,此类等同构造不脱离本揭露的精神和范围,并且在不脱离本揭露的精神和范围的情况下,他们可以在本文中进行各种改变、替换和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1