一种用于电力芯片的保护控制电路的制作方法

1.本发明属于智能电网领域技术领域,尤其涉及一种用于电力芯片的保护控制电路。

背景技术:

2.智能电网数字化变电站将原变电站内的保护和安全自动装置等功能全部纳入了变电站自动化系统,其中保护控制功能是变电站自动化的一个重要衡量指标,在电力系统中的所有一次设备都必须装设保护控制装置。

3.在传统的保护控制设计方案中,多采用cpu/dsp+mcu的架构实现,具有一定的灵活性和可操作性,但这种方案是串行执行的,在硬件底层表现为对少量运算单元的时分复用,运算单元的速度、数量限制了保护算法的整体执行速度,限制了装置的速动性。同时,该方案还具有技术成本高和硬件电路复杂等缺点。因此,随着智能电网的不断发展,现有的cpu/dsp+mcu的保护控制方案有待改进。

技术实现要素:

4.本发明要解决的技术问题:提供一种用于电力芯片的保护控制电路,以解决现有技术的保护控制电路限制了装置的速动性、技术成本高和硬件电路复杂等技术问题。

5.本发明技术方案:

6.一种用于电力芯片的保护控制电路,包括印刷电路板以及分别集成在印刷电路板上的数据采样模块、fpga模块和开关控制模块,fpga模块内嵌有片内软核cpu模块,fpga模块分别与片内软核cpu模块、数据采样模块和开关控制模块电连接,数据采样模块与片内软核cpu模块电连接;

7.数据采样模块用于采集模拟量信号;

8.片内软核cpu模块用于对模拟量信号分别进行处理,得到开关量输入信号;

9.fpga模块用于根据开关量输入信号进行并行逻辑运算,生成开关控制信号;

10.开关控制模块用于根据开关控制信号进行运行,完成保护控制。

11.数据采样模块包括一个以上模拟量输入电路、一个以上隔离电路和多路复用开关,模拟量输入电路的数量和隔离电路的数量相同,且所有模拟量输入电路与所有隔离电路对应设置;

12.每个模拟量输入电路均通过对应的隔离电路与多路复用开关电连接,多路复用开关还分别与片内软核cpu模块和fpga模块电连接。

13.片内软核cpu模块包括片内cpu软核、数据处理电路、a/d转换电路和采样数据寄存器;

14.多路复用开关依次通过数据处理电路和a/d转换电路与采样数据寄存器电连接,数据处理电路、a/d转换电路和采样数据寄存器均与片内cpu软核电连接,片内cpu软核还与fpga模块电连接。

15.fpga模块包括数据调度子模块、cpu软核总线接口、频率提取子模块、采样脉冲生成子模块、保护算法子模块和开关量生成子模块;

16.片内cpu软核通过cpu软核总线接口与数据调度子模块电连接,数据调度子模块分别与多路复用开关、频率提取子模块、采样脉冲生成子模块、保护算法子模块和开关量生成子模块电连接,频率提取子模块还与采样脉冲生成子模块电连接,开关量生成子模块还与开关控制模块电连接。

17.保护算法子模块包括特征量计算单元、数据源调度单元、分合闸逻辑判断单元和一个以上算法判断单元;

18.数据调度子模块的输出端与数据源调度单元的输入端电连接,数据调度子模块的输出端还通过特征量计算单元与数据源调度单元的输入端电连接,数据源调度单元的输出端分别与每个算法判断单元的输入端电连接,每个所述算法判断单元的输出端均与分合闸逻辑判断单元的输入端电连接,分合闸逻辑判断单元的输出端与数据调度子模块的输入端电连接。

19.每个算法判断单元均包括数据读取子单元、与门、时间继电器、启动子单元、录波子单元和开出子单元;

20.在每个算法判断单元中,数据读取子单元的输入端与数据源调度单元的输出端电连接,数据读取子单元的输出端通过对应的与门与对应的时间继电器的输入端电连接,时间继电器的输出端分别与对应的启动子单元、录波子单元和开出子单元电连接,启动子单元、录波子单元和开出子单元还均与分合闸逻辑判断单元的输入端电连接。

21.fpga模块还包括goose报文接收子模块和goose报文发送子模块;

22.goose报文接收子模块和goose报文发送子模块均与数据调度子模块电连接。

23.fpga模块还包括通信接口和存储器访问接口;

24.数据调度子模块通过通信接口与外部的通信设备通信连接,数据调度子模块通过存储器访问接口与外部的存储器通信连接。

25.数据调度子模块利用cpu软核总线接口从片内软核cpu模块中得到的数据,输入特征量计算单元,计算得到一个以上的特征量数据,输出至数据源调度单元;数据源调度单元根据各个算法判断单元中的算法逻辑,对各种特征量数据进行挑选、复制和组合,得到每个算法判断单元对应的计算结果;将所有的计算结果输出至分合闸逻辑判断单元,根据分合闸逻辑判断规则,判断出分合闸信号集合;最后将这些分合闸信号集合再反馈至数据调度子模块,实现多种保护算法的并行逻辑运算,达到保护控制的目的。

26.数据源调度单元根据启动算法判断单元、保护特征算法实现单元、特殊情况识别单元包含的各种算法的需要,对各种特征量数据流、处理过的采样值数据流、开入量数据流、定值控制字、压板信息、配置及变更信息进行挑选、复制和组合,以采样间隔为节拍,每节拍发送由一个采样脉冲对应的数据生成的数据集,并行分配到这三个单元内部各算法单元的数据入口,同时提供时标,即三个数据读取子单元的入口,使后续的每个子单元专注于各自所负责算法的实现,在对应的节拍内生成相应的带时标的启动信号、动作信号和识别信号。

27.本发明的有益效果:

28.本发明通过数据采样模块采集多路模拟量信号,实现多通道的数据采样,再通过

片上软核cpu模块实现数据处理,为后续fpga模块的并行逻辑运算提供合适的数据来源;通过fpga模块进行并行逻辑运算,得到的开关控制信号输出至后级的开关控制模块,实现并行执行的保护控制方案;

29.本发明的用于电力芯片的保护控制电路,在fpga上嵌入片内软核cpu模块,实现了cpu+fpga的单芯片集成架构,基于该单芯片集成架构,以并行执行的方式实现保护控制的逻辑运算,有效提升了传统cpu+mcu架构的运算能力和执行速度,保证了系统的速动性、安全性和可靠性;同时实现了保护控制方案的小型化和集成化,技术成本低、电路结构简单。

30.解决了现有技术的保护控制电路限制了装置的速动性、技术成本高和硬件电路复杂等技术问题。

附图说明

31.图1为本发明实施例中一种用于电力芯片的保护控制电路的结构示意图;

32.图2为本发明实施例中另一种用于电力芯片的保护控制电路的结构示意图;

33.图3为本发明实施例中保护算法子模块的结构示意图;

34.图4为本发明实施例中算法判断单元的结构示意图。

具体实施方式

35.以下结合附图对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

36.下面结合附图,对本发明进行说明。

37.实施例、如图1所示,一种用于电力芯片的保护控制电路,包括印刷电路板以及分别集成在所述印刷电路板上的数据采样模块、fpga模块和开关控制模块,所述fpga模块内嵌有片内软核cpu模块,所述fpga模块分别与所述片内软核cpu模块、所述数据采样模块和所述开关控制模块电连接,所述数据采样模块与所述片内软核cpu模块电连接;

38.所述数据采样模块用于采集多路模拟量信号;

39.所述片内软核cpu模块用于对多路所述模拟量信号分别进行处理,得到多路开关量输入信号;

40.所述fpga模块用于根据多路所述开关量输入信号进行并行逻辑运算,生成开关控制信号;

41.所述开关控制模块用于根据所述开关控制信号进行运行,完成保护控制。

42.通过数据采样模块采集多路模拟量信号,实现多通道的数据采样,再通过片上软核cpu模块实现数据处理,为后续fpga模块的并行逻辑运算提供合适的数据来源;通过fpga模块进行并行逻辑运算,得到的开关控制信号输出至后级的开关控制模块,实现并行执行的保护控制方案。

43.本实施例的用于电力芯片的保护控制电路,在fpga上嵌入片内软核cpu模块,实现了cpu+fpga的单芯片集成架构,基于该单芯片集成架构,以并行执行的方式实现保护控制的逻辑运算,有效提升了传统cpu+mcu架构的运算能力和执行速度,保证了系统的速动性、安全性和可靠性;同时实现了保护控制方案的小型化和集成化,技术成本低、电路结构简单。

44.其中,片内软核cpu模块是利用fpga片内提供的可编程逻辑/寄存器/连线资源、基础dsp硬核、ram模块等硬件资源以及片外flash存储器搭建的cpu系统,可以实现普通cpu的功能,并可像普通cpu一样进行软件开发。fpga模块中的各个部件在该片内软核cpu模块的协调下各司其职、互相协作和并行运行。

45.优选地,如图2所示,所述数据采样模块包括多个模拟量输入电路、多个隔离电路和多路复用开关,所述模拟量输入电路的数量和所述隔离电路的数量相同,且所有所述模拟量输入电路与所有所述隔离电路对应设置;

46.每个所述模拟量输入电路均通过对应的所述隔离电路与所述多路复用开关电连接,所述多路复用开关还分别与所述片内软核cpu模块和所述fpga模块电连接。

47.通过多个模拟量输入电路实现多通道(例如16通道)的电流模拟量和电压模拟量的数据采样,通过与每个模拟量输入电路一一对应设置的隔离电路,可以实现数据隔离和保护作用,提高数据采样的可靠性;将每个经过隔离电路后的模拟量输入多路复用开关,实现对输入的多通道模拟量按照预设的采样波点选择合适的通道模拟量进入后级的电路中;其中,多路复用开关与fpga模块电连接,用于在fpga模块的调度下选择合适的采样波点和通道;多路复用开关与片内软核cpu模块电连接,用于将选择的通道模拟量输入到片内软核cpu模块内进行数据处理。通过上述结构的数据采样模块,基于fpga模块的优势,实现了高速的实时信号采样,便于后续的逻辑运算,芯片占用资源小,运行速度快。

48.优选地,如图2所示,所述片内软核cpu模块包括片内cpu软核、数据处理电路、a/d转换电路和采样数据寄存器;

49.所述多路复用开关依次通过所述数据处理电路和所述a/d转换电路与所述采样数据寄存器电连接,所述数据处理电路、所述a/d转换电路和所述采样数据寄存器均与所述片内cpu软核电连接,所述片内cpu软核还与所述fpga模块电连接。

50.数据处理电路用于在片内cpu软核的控制下,对多路复用开关输入的模拟量信号进行调理,例如将电压模拟量信号转换为低于2.5v的电压信号;a/d转换电路用于在片内cpu软核的控制下,将调理后的模拟量信号进行模数转换,得到对应的数字量信号;采样数据寄存器用于在片内cpu软核的控制下,将模数转换后的数字量信号进行存储,便于后续fpga模块的信号调度和逻辑运算,得到开关控制信号,进而实现保护控制;上述各模块均嵌入fpga模块内,只占用了fpga的一少部分硬件资源,以片内cpu软核为核心,实现初始化、人机化等功能,并在该cpu软核的协调下实现逻辑运算数据源的预处理,与传统保护控制方案相比,既有效提升了运算能力和执行速度,又实现了小型化和集成化。

51.优选地,如图2所示,所述fpga模块包括数据调度子模块、cpu软核总线接口、频率提取子模块、采样脉冲生成子模块、保护算法子模块和开关量生成子模块;

52.所述片内cpu软核通过所述cpu软核总线接口与所述数据调度子模块电连接,所述数据调度子模块分别与所述多路复用开关、所述频率提取子模块、所述采样脉冲生成子模块、所述保护算法子模块和所述开关量生成子模块电连接,所述频率提取子模块还与所述采样脉冲生成子模块电连接,所述开关量生成子模块还与所述开关控制模块电连接。

53.数据调度子模块利用fpga片内的可编程逻辑构成多路并行运行、互相协作的状态机,完成各模块之间的数据、信号的调度工作,包括为多路复用开关提供通道选择控制信号,便于选择合适的通道模拟量,还包括为保护算法子模块提供所需的数据,便于进行保护

逻辑运算,达到保护控制的目的。数据调度子模块通过cpu软核总线接口与片内cpu软核实现数据交互,包括获取其采样数据寄存器中的数字量信号,再利用频率提取子模块和采样脉冲生成子模块,得到数据调度的采样脉冲。保护算法子模块根据数据调度子模块提供的数据进行并行逻辑运算,并将计算后的数据返回给数据调度子模块,再利用开关量生成子模块生成开关控制信号,输出至开关控制模块,实现保护控制。本实施例上述结构的fpga模块,将各通道上的算法模块融合到fpga芯片中,能实现保护控制算法的分布式运算和并行处理,最大化地提升了运算能力和执行速度。

54.优选地,如图2所示,所述保护算法子模块包括特征量计算单元、数据源调度单元、分合闸逻辑判断单元和多个算法判断单元;

55.所述数据调度子模块的输出端与所述数据源调度单元的输入端电连接,所述数据调度子模块的输出端还通过所述特征量计算单元与所述数据源调度单元的输入端电连接,所述数据源调度单元的输出端分别与每个所述算法判断单元的输入端电连接,每个所述算法判断单元的输出端均与所述分合闸逻辑判断单元的输入端电连接,所述分合闸逻辑判断单元的输出端与所述数据调度子模块的输入端电连接。

56.数据调度子模块利用cpu软核总线接口从片内软核cpu模块中得到的数据,输入特征量计算单元,计算得到多种特征量数据,输出至数据源调度单元;数据源调度单元根据各个算法判断单元中的算法逻辑,对各种特征量数据进行挑选、复制、组合等,得到每个算法判断单元对应的计算结果;将所有的计算结果输出至分合闸逻辑判断单元,能够根据分合闸逻辑判断规则,判断出分合闸信号集合;最后将这些分合闸信号集合再反馈至数据调度子模块,实现多种保护算法的并行逻辑运算,达到保护控制的目的。

57.具体地,数据调度子模块获取到的数据中包含时间数据,根据该时间数据可以生成对应的时标,在特征量计算单元计算得到的特征量数据上打上时标,并在后续的的数据传输的过程中,均带上对应的时标,将特征量数据和对应的时标组合成一个新的数据窗,便于实现fpga模块在逻辑运算过程的每帧上仅携带一个采样时刻的特征量数据,各个特征量数据由fpga模块硬件上的独立模块以流水线的方式予以并行执行,与传统cpu/dsp+mcu基于对运算单元进行时分复用的串行运算相比,具有显著的速度优势。

58.具体地,特征量数据包括变压器保护中的各相差动电流的三次谐波幅值等数据。

59.优选地,如图4所示,每个所述算法判断单元均包括数据读取子单元、与门、时间继电器、启动子单元、录波子单元和开出子单元;

60.在每个所述算法判断单元中,所述数据读取子单元的输入端与所述数据源调度单元的输出端电连接,所述数据读取子单元的输出端通过对应的所述与门与对应的所述时间继电器的输入端电连接,所述时间继电器的输出端分别与对应的所述启动子单元、所述录波子单元和所述开出子单元电连接,所述启动子单元、所述录波子单元和所述开出子单元还均与所述分合闸逻辑判断单元的输入端电连接。

61.在每个算法判断单元中均设置上述子单元,既能够实现每种保护控制算法的逻辑判断,还能相应地配置保护控制措施和录入故障波形,便于每种保护控制算法的动作执行;将上述逻辑判断结果、保护控制措施和故障波形作为对应的算法判断单元的计算结果集合,输入后续的分合闸逻辑判断单元,进行综合分析和权衡,综合判断出最终输出的分合闸信号状态信号并反馈至数据调度子模块,便于生成开关控制模块最终的开关控制信号。

62.具体地,算法判断单元包括启动算法判断单元、保护特征算法实现单元、特殊情况识别单元等。每个单元均包括上述的数据读取子单元、与门、时间继电器、启动子单元、录波子单元和开出子单元,便于实现每个保护算法中的逻辑判断、保护控制措施、录入故障波形等功能。

63.具体地,本实施例中,启动算法判断单元、保护特征算法实现单元、特殊情况识别单元中的各算法单元在每个节拍(亦即采样间隔,下同)并行接收数据源调度单元提供的数据集,并行、独立完成各自负责的启动条件判断算法、动作判断算法、特殊情况识别算法,输出相应的启动信号集合、动作信号集合、识别信号集合(三者都携带时标)到分合闸闸逻辑判断单元。

64.数据源调度单元根据启动算法判断单元、保护特征算法实现单元、特殊情况识别单元包含的各种具体算法的需要,对各种特征量数据流、处理过的采样值数据流、开入量数据流、定值控制字、压板信息、配置及其变更信息等进行挑选、复制、组合,以采样间隔为节拍,每节拍发送由一个采样脉冲对应的数据生成的数据集,并行分配到这三个单元内部各算法单元的数据入口(同时提供时标),即三个数据读取子单元的入口,使后续的每个子单元可以专注于各自所负责算法的实现,在对应的节拍内生成相应的带时标的启动信号、动作信号和识别信号。

65.具体地,本实施例中,分合闸逻辑判断单元在每个节拍并行接收上述三个单元输出的启动信号集、动作信号集和识别信号集,将时标相同的三个信号集组合起来(即按时标对齐),形成一个二级集合。然后,在每个节拍,根据各种保护跳闸逻辑(例如零序过流保护跳闸逻辑)对信号源的要求,将一个二级集合内各动作信号以及与之对应的启动信号集和识别信号集选出来,进行逻辑运算(即用本节拍的各启动信号和识别信号决定本节拍的各动作信号是否有效),最后将与各动作信号组合所对应的、并行完成的逻辑运算结果输出,形成本节拍输出的分合闸信号集。

66.需要说明的是,本实施例中分合闸逻辑判断单元可以采用受限于更多条件、更复杂的条件间逻辑关系、时序关系的判据,以期获得更好的可靠性、速动性、选择性、灵敏性。

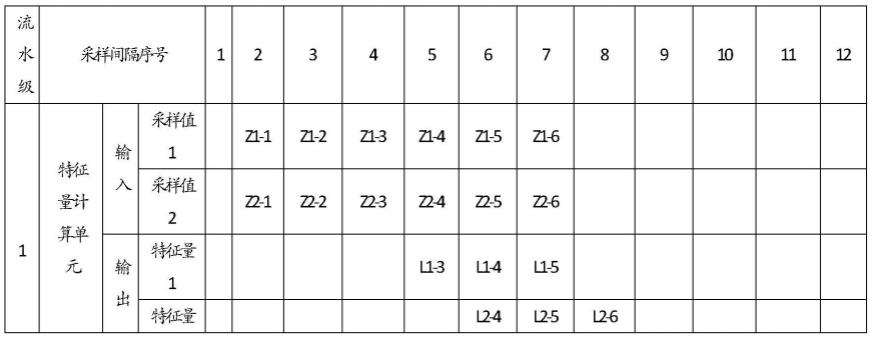

67.本实施例提供保护算法子模块进行逻辑运算所实现的流水线控制策略的一个简化示例,如表1所示。

68.表1保护算法子模块逻辑运算得到的流水线控制策略

69.[0070][0071]

在表1中,各物理量名称中横线后面的数字是时标的简化形式,表示参与生成这个物理量的最后一个采样值由第几个采样脉冲获得;加黑的物理量表示启动条件得到满足、动作信号有效、出现特殊情况、分合闸信号有效的情况,而不加黑的物理量则表示相反的情况。空白表格表示本采样间隔内相应的数据、状态是无效的。

[0072]

在表1中,假设:采样间隔n生成的采样值在采样间隔n+1可用,对应的采样值时标为n;计算特征量1需要积累3个采样值1,计算特征量2需要积累4个采样值1以及4个采样值2;启动条件1、动作信号1、识别信号1的判断都需要积累特征量1、开关量1各2个,启动条件2、动作信号2、识别信号2的判断都需要积累特征量2、开关量2各2个;则发出分合闸信号1需要动作信号1有效,并且启动条件1满足以及识别信号1、2均不被检出,则发出分合闸信号2需要动作信号2有效,并且启动条件2满足以及识别信号2不被检出。表1中各单元所包含的各算法单元是互相独立和并行运行的。

[0073]

具体地,本实施例中的算法判断单元还可以包括但不局限于复压过流保护判断单元、反时限过流保护判断单元、差动保护判断单元、三段式过流保护判断单元、低周减载保护判断单元、零序过流保护判断单元和零序过压保护判断单元,均按照常规的逻辑判断规则来判断。

[0074]

优选地,如图2所示,所述fpga模块还包括goose报文接收子模块和goose报文发送子模块;

[0075]

所述goose报文接收子模块和所述goose报文发送子模块均与所述数据调度子模块电连接。

[0076]

通过goose报文接收子模块和goose报文发送子模块,便于整个保护控制电路与外部客户端之间的数据交互,在保护控制装置与客户端之间传输开入(包括客户端的常规开入等)和开出(包括分合闸、启动等)等数据信息。

[0077]

优选地,如图2所示,所述fpga模块还包括通信接口和存储器访问接口;

[0078]

所述数据调度子模块通过所述通信接口与外部的通信设备通信连接,所述数据调度子模块通过所述存储器访问接口与外部的存储器通信连接。

[0079]

通过通信接口实现整个保护控制电路与外部的通信设备之间的数据交互,通过存储器访问接口便于整个保护控制电路访问外部的存储器中的数据,进一步帮助提升保护控制设计中的运算能力和执行速度。

[0080]

具体地,本实施例中通信接口包括以太网通信接口和串行通讯接口,存储器访问接口包括sdram访问接口和flash访问接口。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1