集成电路和包括该集成电路的电子设备的制作方法

集成电路和包括该集成电路的电子设备

1.相关申请的交叉引用

2.本技术基于并要求于2021年4月15日提交韩国专利厅的韩国专利申请第10-2021-0049310号以及于2021年6月22日提交韩国专利厅的韩国专利申请第10-2021-0081043号的优先权,其公开内容通过引用方式整体并入本文。

背景技术:

3.本发明构思涉及一种被配置为执行特定操作的集成电路,并且更具体地,涉及一种包括电源电路的集成电路,该电源电路被配置为产生要提供给集成电路中的系统负载的电源电压,以及包括该集成电路的电子设备。

4.最近,因为电子设备执行多种操作,所以电子设备的电流消耗范围已经扩大。例如,对于显示设备,随着显示器的分辨率和扫描速率的增加,显示驱动器集成电路的电流消耗的最大值持续增加,从而导致电流消耗范围扩大。此外,显示驱动器集成电路的电流消耗可以根据多种原因实时变化,诸如要处理的图像数据的特性和显示设备的操作模式。

5.因此,对通过根据电流消耗的实时变化来调节电流供应同时覆盖扩大的电流消耗范围来减少或防止不必要的电流消耗的方法的需求已经增加。

技术实现要素:

6.本发明构思提供了一种集成电路以及包括该集成电路的电子设备,该集成电路被配置为通过根据由包括在该集成电路中的系统负载汲取的负载电流使用多个电源电压中的至少一个来产生电源电压,并将该电源电压提供给系统负载。

7.根据本发明构思的示例实施例,提供了一种集成电路,包括:电源电路,被配置为从第一电源电压和第二电源电压中的至少一个产生电源电压;以及系统负载,被配置为通过经过电源电路的输出节点来接收电源电压来操作,其中电源电路包括:第一低压降输出(ldo)调节器,被配置为从第一电源电压产生通过输出节点流向系统负载的第一负载电流;以及第二ldo调节器,被配置为基于第一ldo调节器的内部节点的电压之间的差,从第二电源电压选择性地产生通过输出节点流向系统负载的第二负载电流。

8.根据本发明构思的示例实施例,提供了一种集成电路,包括:电源电路,被配置为从第一电源电压和第二电源电压中的至少一个产生电源电压;以及系统负载,被配置为通过从电源电路接收电源电压并从电源电路汲取第一负载电流来操作,其中电源电路包括:第一低压降输出(ldo)调节器,被配置为从第一电源电压产生流向系统负载的第二负载电流;以及第二ldo调节器,被配置为根据第一负载电流的增加,响应于第二负载电流的饱和状态,从第二电源电压产生流向系统负载的第三负载电流。

9.根据本发明构思的示例实施例,提供了一种电子设备,包括:显示驱动器集成电路(以下称为ddi);以及功率管理集成电路(以下称为pmic),被配置为向ddi提供第一电源电压和第二电源电压,其中ddi包括:第一逻辑电路,被配置为通过接收第一电源电压来操作;第二逻辑电路,被配置为通过接收电源电压来操作;以及电源电路,被配置为从第一电源电

压和第二电源电压中的至少一个输出电源电压,其中电源电路包括:第一低压降输出(ldo)调节器,被配置为从第一电源电压向第二逻辑电路输出第一负载电流;以及第二ldo调节器,连接到第一ldo调节器的内部节点,并且被配置为当内部节点的电压之间的差是参考值或更大时,从第二电源电压向第二逻辑电路输出第二负载电流。

10.根据本发明构思的示例实施例,提供了一种集成电路,包括:第一低压降输出(ldo)调节器,被配置为从第一电源电压产生第一负载电流;第二ldo调节器,被配置为从第二电源电压选择性地产生第二负载电流;以及系统负载,被配置为从由第一ldo调节器和第二ldo调节器共享的输出节点汲取包括第一负载电流和第二负载电流中的至少一个的第三负载电流,其中第一ldo调节器包括:第一电流产生电路,被配置为通过向其施加第一电源电压来产生第一负载电流;以及第一比较电路,被配置为通过将参考电压与对应于输出节点的电压的反馈电压进行比较来产生第一使能控制信号,并将第一使能控制信号提供给第一电流产生电路,并且第二ldo调节器包括:第二电流产生电路,被配置为通过向其施加第二电源电压来产生第二负载电流;以及第二比较电路,连接到第一比较电路的内部节点,并被配置为通过比较内部节点的电压来产生第二使能控制信号,并将第二使能控制信号提供给第二电流产生电路。

附图说明

11.从以下结合附图的详细描述中,将更清楚地理解本发明构思的示例实施例,其中:

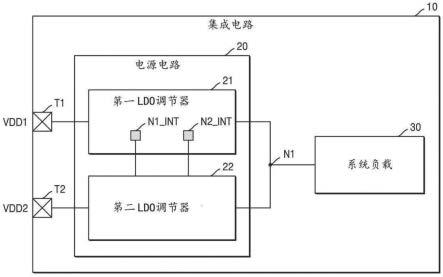

12.图1是根据本发明构思的示例实施例的集成电路的框图;

13.图2是根据本发明构思的示例实施例的集成电路的操作方法的流程图;

14.图3是根据本发明构思的示例实施例的电源电路的电路图;

15.图4a是根据本发明构思的示例实施例的指示电源电路的操作的时序图,以及图4b和图4c是根据本发明构思的示例实施例的用于描述电源电路的操作的电路图;

16.图5是根据本发明构思的示例实施例的电源电路的电路图,以及图6是指示图5的电源电路的操作的时序图;

17.图7是根据本发明构思的示例实施例的指示系统负载的负载电流趋势的曲线图;

18.图8a是根据本发明构思的示例实施例的第二低压降输出(ldo)调节器的框图,图8b是用于描述根据系统负载的操作区域的图8a的第二ldo调节器的操作的曲线图,以及图8c是用于描述根据图8a的第二ldo调节器的操作的电源电压的曲线图;

19.图9是图2的操作s120中的集成电路的示例操作方法的流程图;

20.图10a是根据本发明构思的示例实施例的电源电路的电路图,以及图10b是用于描述根据系统负载的操作区域的图10a的第二ldo调节器的操作的曲线图;

21.图11是根据本发明构思的示例实施例的第一ldo调节器的电路图;

22.图12是根据本发明构思的示例实施例的第二ldo调节器的电路图;

23.图13是根据本发明构思的示例实施例的显示驱动器集成电路的框图;以及

24.图14是根据本发明构思的示例实施例的电子设备的框图。

具体实施方式

25.图1是根据本发明构思的示例实施例的集成电路10的框图。在说明书中,集成电路

10可以包括在电子设备(未示出)中,以执行电子设备所需的特定操作。集成电路10可以由电子设备(未示出)中的单个独立芯片实现,或者由链接到电子设备(未示出)中的另一电路来实现。例如,电子设备(未示出)可以包括智能手机、平板个人计算机(pc)、移动电话、视频电话、电子书阅读器、台式pc、膝上型pc、上网本计算机、个人数字助理(pda)、便携式多媒体播放器(pmp)、mp3播放器、移动医疗器材、照相机和可穿戴设备(例如,诸如电子眼镜、电子服装、电子手镯、电子项链、电子配件、电子纹身或智能手表之类的头戴式设备(hmd))中的至少一种。

26.根据一些示例实施例,电子设备可以是具有图像显示功能的智能家用电器。智能家用电器可以包括例如电视(tv)、数字视盘(dvd)播放器、音频播放器、冰箱、空调、吸尘器、烤箱、微波炉、洗衣机、空气净化器、机顶盒、tv盒(例如三星homesync

tm

、苹果tv

tm

或谷歌tv

tm

)、游戏控制台、电子词典、电子钥匙、便携式摄像机和电子相框中的至少一种。

27.根据一些示例实施例,电子设备可以包括多种医疗设备(例如,磁共振血管造影机(mra)机器、磁共振成像(mri)机器、计算机断层摄影(ct)机器、成像机器、超声波机器等)、导航设备、全球定位系统(gps)接收器、事件数据记录器(edr)、飞行数据记录器(fdr)、车辆信息娱乐设备、海上电子装备(例如,海上导航设备、陀螺罗盘等)、航空电子设备、安全设备、车辆头部单元、工业或家用机器人、金融机构的自动柜员机(atm)和商店中的销售点(pos)中的至少一种。

28.根据一些示例实施例,电子设备可以包括家具或建筑物/结构的一部分中的至少一种,其包括图像显示功能、电子板、电子签名接收设备、投影仪和多种仪表(例如,水表、电表、煤气表、无线电波表等)。根据本发明构思的示例实施例的电子设备可以是上述多种设备中的一种或组合。替代地,电子设备可以是柔性显示设备。

29.参考图1,集成电路10可以包括第一端子t1、第二端子t2、电源电路20和/或系统负载30。第一电源电压vdd1可以施加到第一端子t1,并且第二电源电压vdd2可以施加到第二端子t2。

30.电源电路20可以通过第一端子t1和第二端子t2接收第一电源电压vdd1和第二电源电压vdd2中的至少一个,并产生驱动系统负载30所需的电源电压。电源电路20可以通过输出节点n1向系统负载30提供电源电压。在示例实施例中,第一电源电压vdd1和第二电源电压vdd2可以随着彼此不同的独立电源电压而具有相同或不同的幅度。在一些示例实施例中,第一电源电压vdd1可以从第二电源电压vdd2产生。在说明书中,可以理解,输出节点n1的电压与提供给系统负载30的电源电压相同。

31.系统负载30可以根据功耗的幅度在多个操作区域中操作。操作区域可以根据系统负载30的功耗来定义。例如,系统负载30可以在消耗相对低功率的第一操作区域或消耗相对高功率的第二操作区域中操作。在一些示例实施例中,可以通过另外考虑系统负载30的过程、电压和温度(pvt)条件来定义操作区域。当系统负载30在第一操作区域中操作时,从输出节点n1汲取的第一负载电流可能相对较小,并且当系统负载30在第二操作区域中操作时,从输出节点n1汲取的第一负载电流可能相对较大。系统负载30可以在特定的操作区域中消耗高功率,并且在一些示例实施例中,高电平的第一负载电流可以从输出节点n1瞬时汲取。当从电源电路20提供给输出节点n1的负载电流的幅度和由系统负载30汲取的第一负载电流的幅度之间的平衡丢失时,输出节点n1的电压(例如,系统负载30的电源电压)可能

改变,使得系统负载30不平滑地操作。为了解决这个问题,下面描述根据本发明构思的示例实施例的电源电路20。

32.电源电路20可以包括第一低压降输出(ldo)调节器21和至少一个第二ldo调节器22。在示例实施例中,第一ldo调节器21可以通过第一端子t1接收第一电源电压vdd1,并且从第一电源电压vdd1产生通过输出节点n1流向系统负载30的第二负载电流。第一ldo调节器21可以产生与系统负载30的功耗匹配的第二负载电流。例如,随着系统负载30的功耗增加,从输出节点n1汲取的第一负载电流可以增加,并且第一ldo调节器21可以响应于增加的第一负载电流从第一电源电压vdd1产生第二负载电流。当第一负载电流的幅度超过阈值时,由第一ldo调节器21产生的第二负载电流达到饱和状态,并且在饱和状态之后,第一负载电流的幅度可以大于第二负载电流的幅度。在一些示例实施例中,第二ldo调节器22可以产生第三负载电流,用于补偿连续增加的第一负载电流和饱和的第二负载电流之间的差。

33.在示例实施例中,第二ldo调节器22可以通过第二端子t2接收第二电源电压vdd2,并且从第二电源电压vdd2产生通过输出节点n1流向系统负载30的第三负载电流。在示例实施例中,当系统负载30的第一负载电流的幅度超过阈值时,例如,当系统负载30在特定操作区域中操作时,饱和的第二负载电流可以通过使用第一ldo调节器21来产生,第三负载电流可以通过使用第二ldo调节器22来产生,并且饱和的第二负载电流和第三负载电流可以输出到系统负载30。在示例实施例中,第一电源电压vdd1的幅度可以小于第二电源电压vdd2的幅度。在一些示例实施例中,第一电源电压vdd1的幅度可以与第二电源电压vdd2的幅度相同。

34.在示例实施例中,第二ldo调节器22可以连接到第一ldo调节器21的第一内部节点n1_int和第二内部节点n2_int,以基于第一内部节点n1_int和第二内部节点n2_int的电压之间的差选择性地产生第三负载电流。即,第二ldo调节器22可以通过基于第一内部节点n1_int和第二内部节点n2_int的电压确定第一ldo调节器21的第二负载电流的饱和状态来开始产生第三负载电流。

35.在示例实施例中,第一内部节点n1_int和第二内部节点n2_int的电压可以根据由系统负载30汲取的第一负载电流到阈值或更高的增加而响应于电源电压(或输出节点n1的电压)的下降而变化。此外,响应于电源电压的下降,第一内部节点n1_int的电压可以升高,并且第二内部节点n2_int的电压可以降低。在一些示例实施例中,响应于电源电压的下降,第一内部节点n1_int的电压可以降低,并且第二内部节点n2_int的电压可以升高。在示例实施例中,第一内部节点n1_int和第二内部节点n2_int中的每一个可以输出施加到第一ldo调节器21的参考电压和与电源电压匹配的反馈电压之间的差。

36.第二ldo调节器22可以直接从第一ldo调节器21接收指示电源电压是否已经下降的第一内部节点n1_int和第二内部节点n2_int的电压,从而减少或最小化检测电源电压下降所需的比较电路的结构。

37.在示例实施例中,第二ldo调节器22可以包括多个辅助电流产生电路(未示出),每个辅助电流产生电路被配置为产生包括在第三负载电流中的辅助电流。第二ldo调节器22可以根据系统负载30的操作区域或系统负载30的第一负载电流的幅度来确定要使能的辅助电流产生电路的数量,并且使能的辅助电流产生电路可以产生辅助电流。辅助电流产生电路可以被称为辅助电流路径,并且参考图8a等描述其具体示例实施例。

38.即使在系统负载30的多种操作区域中,根据本发明构思的示例实施例的集成电路10也可以通过使用第一ldo调节器21和第二ldo调节器22向系统负载30提供稳定的电源电压,并且第二ldo调节器22可以从第一ldo调节器21直接接收选择性地产生负载电流所需的信号,从而相对简化电路结构。

39.图2是根据本发明构思的示例实施例的集成电路的操作方法的流程图。

40.参考图2,在操作s100中,集成电路可以通过使用第一ldo调节器向系统负载供应第一负载电流。例如,第一ldo调节器可以通过输出节点向系统负载供应第一负载电流,并且输出节点的电压是电源电压,并且可以基于其来驱动系统负载。在操作s110中,集成电路可以检测输出节点的电压是否已经下降。换言之,在操作s110中,集成电路可以检测要提供给系统负载的电源电压是否已经下降。例如,集成电路的第二ldo调节器可以连接到第一ldo调节器的内部节点,以基于内部节点的电压之间的差来检查输出节点的电压是否已经下降。如上所述,由于由系统负载从输出节点汲取的第三负载电流中的连续或急剧增加,当从第一ldo调节器供应的第一负载电流达到饱和状态时,饱和的第一负载电流和正在增加的第三负载电流之间的不平衡,可能出现电源电压的下降。当操作s110指示“yes(是)”时,为了减少或防止电源电压的连续下降,在操作s120中,集成电路可以通过使用第二ldo调节器向系统负载另外供应第二负载电流。第二ldo调节器与第一ldo调节器共享输出节点,并且可以通过输出节点向系统负载供应第二负载电流。第二ldo调节器可以产生第二负载电流,其与由系统负载汲取的第三负载电流和饱和的第一负载电流之间的差成比例。通过这样做,第二ldo调节器可以响应于电源电压的下降而立即提供第二负载电流,从而减少或最小化电源电压的下降程度并保证系统负载的稳定操作。否则,当操作s110指示“no(否)”时,此后可以执行操作s100。

41.在一些示例实施例中,在操作s110中,集成电路可以检测输出节点的电压的下降程度是否是参考程度或更高。例如,集成电路的第二ldo调节器可以检测第一ldo调节器的内部节点的电压之间的差是否是参考值或更大。此后,在操作s120中,当内部节点的电压之间的差是参考值或更大时,第二ldo调节器可以产生第二负载电流。通过这样做,第二ldo调节器可以将第二负载电流的产生开始时间从第一负载电流达到饱和状态的时间点延迟特定时间,从而避免由于第一ldo调节器和第二ldo调节器的操作重叠而导致的波纹或噪声的增加。

42.图3是根据本发明构思的示例实施例的电源电路100的电路图。在图3中,负载电流源lcs可以指示由系统负载汲取的负载电流。图3中所示的电源电路100仅仅是用于描述本发明构思的技术思想的示例,因此,本发明构思不限于此,并且将充分理解,电源电路100的实现示例可以是多种示例。

43.参考图3,电源电路100可以包括第一ldo调节器110和至少一个第二ldo调节器120。此外,在非限制性示例中,为了稳定操作,电源电路100还可以包括输出节点n1和地之间连接的第一电容器c1。

44.在示例实施例中,第一ldo调节器110可以包括第一至第三电阻器r1、r2和r3、第一晶体管tr1、第一比较器111和/或第二比较器112。在本说明书中,第一比较器111和第二比较器112可以被定义为包括在第一ldo调节器110的第一比较电路中的元件。此外,第一电阻器r1和第一晶体管tr1可以被定义为包括在第一电流产生电路中的元件,该第一电流产生

电路被配置为通过使用第一电源电压vdd1产生第一负载电流。第一晶体管tr1可以是p沟道金属氧化物半导体场效应晶体管(mosfet)。在一些示例实施例中,第一晶体管tr1可以是功率晶体管。

45.第一电阻器r1的一端可以连接到接收第一电源电压vdd1的端子,并且其另一端可以连接到第一晶体管tr1的源极端子。第一晶体管tr1的漏极端子可以连接到输出节点n1。第二电阻器r2的一端可以连接到输出节点n1,并且其另一端可以连接到反馈节点n_fb。第三电阻器r3的一端可以连接到反馈节点n_fb,并且其另一端可以连接到地。反馈节点n_fb的电压是反馈电压,并且可以由输出节点n1的电压(或电源电压)以及第二电阻器r2与第三电阻器r3的电阻值比来确定。

46.第一比较器111的输入端子可以连接到通过其接收参考电压vref的端子以及反馈节点n_fb。第一比较器111的输出端子可以通过第一内部节点n1_int和第二内部节点n2_int连接到第二比较器112的输入端子。第二比较器112的输出端子可以连接到第一晶体管tr1的栅极端子。

47.第二ldo调节器120可以包括第四电阻器r4、第二晶体管tr2和/或第三比较器121。在本说明书中,第三比较器121可以被定义为包括在第二ldo调节器120的第二比较电路中的元件。此外,第四电阻器r4和第二晶体管tr2可以被定义为包括在第二电流产生电路中的元件,该第二电流产生电路被配置为通过使用第二电源电压vdd2来产生第二负载电流。第二晶体管tr2可以是p沟道mosfet。在一些示例实施例中,第二晶体管tr2可以是功率晶体管。

48.第四电阻器r4的一端可以连接到通过其接收第二电源电压vdd2的端子,并且其另一端可以连接到第二晶体管tr2的源极端子。第二晶体管tr2的漏极端子可以连接到输出节点n1。第三比较器121的输入端子可以连接到第一内部节点n1_int和第二内部节点n2_int。第三比较器121的输出端子可以连接到第二晶体管tr2的栅极端子。

49.在下文中,参照图4a至图4c描述图3的电源电路100的操作。

50.图4a是根据本发明构思的示例实施例的指示电源电路100的操作的时序图,以及图4b和4c是根据本发明构思的示例实施例的用于描述电源电路100的操作的电路图。

51.电源电路100可以在第一时间点t11和第二时间点t21之间的时段以及第三时间点t31之后的时段中执行图4b所示的操作,并且在第二时间点t21和第三时间点t31之间的时段中执行图4c所示的操作。

52.参考图4a,负载电流lc可以指示由负载电流源lcs(参见图4b和4c)从输出节点n1(参见图4b和4c)汲取的电流,第一负载电流i1可以指示由第一ldo调节器110产生的电流(参见图4b和4c),第二负载电流i2可以指示由第二ldo调节器120产生的电流(参见图4b和4c),并且电源电压sv可以指示输出节点n1的电压(参见图4b和4c)。第一参考电流i_rfe1和第二参考电流i_ref2可以是用于定义系统负载的第一操作区域opr1和第二操作区域opr2的参考。第一饱和电流i_sat1可以指示饱和的第一负载电流i1,并且第二饱和电流i_sat2可以指示饱和的第二负载电流i2。此外,目标电源电压t_vdd可以指示其具有目标电平的电源电压sv的电压,并且最小电源电压min_vdd可以指示系统负载通过其具有可操作的最小电压电平的电压。

53.在第一时间点t11和第二时间点t21之间的时段或者第三时间点t31之后的时段

中,系统负载可以在第一操作区域opr1中操作,并且系统负载的功耗的增加可以导致负载电流lc增加。响应于增加的负载电流lc,第一负载电流i1也可以增加。因为是在第一负载电流i1饱和之前,所以可能不会产生第二负载电流i2,并且电源电压sv可能不会下降。

54.进一步参考图4b,在第一时间点t11和第二时间点t21之间的时段或者第三时间点t31之后的时段中,第一比较器111可以接收参考电压vref和反馈电压vfb,并且分别输出指示比较结果的第一电压v1和第二电压v2。因为电源电压sv不下降,所以参考电压vref和反馈电压vfb可以具有相同的幅度,并且第二比较器112可以响应于第一电压v1和第二电压v2产生第一栅极电压vg_main,并且将第一栅极电压vg_main提供给第一晶体管tr1的栅极端子。第一晶体管tr1可以响应于第一栅极电压vg_main而导通,从第一电源电压vdd1产生第一负载电流i1,并且向输出节点n1供应第一负载电流i1。随着负载电流lc增加,第一栅极电压vg_main可以具有从第一电平降低的第二电平l2。在第一负载电流i1饱和之前,第一电压v1和第二电压v2之间不会出现差,并因此第二ldo调节器120可以被禁用。

55.返回参考图4a,在第二时间点t21和第三时间点t31之间的时段中,系统负载可以在第二操作区域opr2中操作,并且系统负载的功耗中的增加可以导致负载电流lc增加。因为第一负载电流i1在第二时间点t21饱和,所以可以产生与负载电流lc匹配的第二负载电流i2,并且可以减少或最小化电源电压sv的下降。

56.进一步参考图4c,在第二时间点t21和第三时间点t31之间的时段中,第二比较器112可以向第一晶体管tr1的栅极端子提供第二电平l2的第一栅极电压vg_main,并且第一晶体管tr1可以响应于第一栅极电压vg_main而完全导通。完全导通的第一晶体管tr1可以产生与第一饱和电流i_sat1匹配的第一负载电流i1,并将第一负载电流i1供应给输出节点n1。由于负载电流lc大于饱和的第一负载电流i1,电源电压sv可能瞬间下降,使得反馈电压vfb小于参考电压vref。第一比较器111可以接收参考电压vref和反馈电压vfb,并分别输出指示比较结果的第一电压v1和第二电压v2。例如,第一电压v1是第一内部节点n1_int的电压,并且可以随着反馈电压vfb小于参考电压vref而升高,以及第二电压v2是第二内部节点n2_int的电压,并且可以随着反馈电压vfb小于参考电压vref而降低。第三比较器121可以比较第一电压v1和第二电压v2,基于比较结果产生第二栅极电压vg_aux,并且将第二栅极电压vg_aux提供给第二晶体管tr2的栅极端子。第二晶体管tr2可以响应于第二栅极电压vg_aux而导通,从第二电源电压vdd2产生第二负载电流i2,并将第二负载电流i2供应给输出节点n1。如上所述,系统负载(未示出)可以通过输出节点n1接收第一负载电流i1和第二负载电流i2,并因此可以减少或防止电源电压sv的下降。

57.图5是根据本发明构思的示例实施例的电源电路100’的电路图,以及图6是指示图5的电源电路100’的操作的时序图。如图5所示,电源电路100’可以包括第一ldo调节器110和第二ldo调节器120’。在图5中,对图3的电源电路100的描述不再重复。

58.如上所述,如果一旦第一ldo调节器110的第一负载电流达到饱和状态,第二ldo调节器120’就产生第二负载电流,则由于第一ldo调节器110和第二ldo调节器120’的操作的瞬时重叠,波纹、噪声等可能重叠,从而引起不必要的功耗。

59.参考图5,第二ldo调节器120’可以进一步包括偏移电压源os,以减少或防止不必要的功耗。即,偏移电压源os可以延迟第二ldo调节器120’的第二负载电流的产生开始定时。然而,包括偏移电压源os的第二ldo调节器120’仅仅是示例实施例,并因此,本发明构思

不限于此,并且被配置为执行与偏移电压源os相同的操作的电路可以被包括在第二ldo调节器120’中。下面参考图11描述其具体示例实施例。

60.在示例实施例中,第三比较器121可以接收第一内部节点n1_int的第一电压,以及其中偏移电压源os的偏移电压被添加到第二内部节点n2_int的电压的第二电压。例如,当第一电压大于第二电压时,第三比较器121可以通过第二晶体管tr2产生第二负载电流。

61.进一步参考图6,在第一时间点t12和第二时间点t22之间的时段中,系统负载可以在第一操作区域opr1中操作,并且随着功耗增加,负载电流lc可以增加。第一负载电流i1可以响应于负载电流lc的增加而增加,并且在第二时间点t22饱和到第一饱和电流i_sat1。在第二时间点t22之后,系统负载可以在第二操作区域opr2中操作。第二ldo调节器120’可以在从第二时间点t22以与偏移电压源os的偏移电压匹配的延迟程度延迟的第三时间点t32开始产生第二负载电流i2。饱和的第一负载电流i1和另外的第二负载电流i2的总和可以与负载电流lc平衡,并因此电源电压sv可以在第三时间点t32和第四时间点t42之间的时段中保持一定的幅度。在第四时间点t42之后,第二ldo调节器120’可以被禁用,并且系统负载可以再次在第一操作区域opr1中操作,使得电源电压sv从第五时间点t52恢复到目标电源电压t_vdd。

62.图7是根据本发明构思的示例实施例的指示系统负载的负载电流趋势的曲线图。

63.参考图7,系统负载可以在第一操作区域opr1和第二操作区域opr2中的任何一个中操作。系统负载可能具有消耗功率的幅度,该幅度根据内部ip)当中同时操作的内部知识产权的数量而变化。例如,随着同时运行的内部ip的数量增加,系统负载的功耗可能增加,并因此,由系统负载汲取的负载电流可能增加。

64.大多数情况下,系统负载可以在第一操作区域opr1中操作,并且根据示例实施例的集成电路可以通过仅使用第一ldo调节器向系统负载供应第一负载电流。在有限的时间内,系统负载可以在第二操作区域opr2中操作,并且根据示例实施例的集成电路可以通过额外地将第二ldo调节器和第一ldo调节器一起使用来向系统负载供应第一负载电流和第二负载电流。

65.根据本发明构思的示例实施例的第一操作区域opr1和第二操作区域opr2可以通过考虑系统负载的操作频率来确定,使得功率管理电路的有效功耗成为可能。

66.图8a是根据本发明构思的示例实施例的第二ldo调节器220的框图,图8b是用于描述根据系统负载的操作区域的图8a的第二ldo调节器220的操作的曲线图,以及图8c是用于描述根据图8a的第二ldo调节器220的操作的电源电压的曲线图。

67.参考图8a,第二ldo调节器220可以包括比较电路221和/或第一辅助电流产生电路222_1到第n辅助电流产生电路222_n。第一辅助电流产生电路222_1到第n辅助电流产生电路222_n可以通过根据系统负载的负载电流lc(参见图3)的幅度被选择性地使能来分别产生第一辅助电流i2_aux1到第n辅助电流i2_auxn。

68.在示例实施例中,第一辅助电流产生电路222_1至第n辅助电流产生电路222_n当中使能的辅助电流产生电路的数量可以根据系统负载的负载电流lc(参见图3)的幅度来确定。例如,随着系统负载的负载电流lc(参见图3)增加,使能的辅助电流产生电路的数量可能增加。

69.在示例实施例中,比较电路221可以通过比较从第一内部节点n1_int接收的第一

电压v1(参见图3)和其中第一偏移电压vos1被添加到第二内部节点n2_int的第二电压v2的电压(参见图3)来产生第一使能控制信号e_cs1,并然后将第一使能控制信号e_cs1提供给第一辅助电流产生电路222_1。比较电路221可以通过将第一电压v1与其中第二偏移电压vos2被添加到第二电压v2的电压进行比较来产生第二使能控制信号e_cs2,并然后将第二使能控制信号e_cs2提供给第二辅助电流产生电路222_2。以这种方式,比较电路221可以通过将第一电压v1与其中第n偏移电压vosn被添加到第二电压v2的电压进行比较来产生第n使能控制信号e_csn,并然后将第n使能控制信号e_csn提供给第n辅助电流产生电路222_n。

70.为了响应于增加的负载电流lc(参见图3)顺序地使能第一辅助电流产生电路222_1到第n辅助电流产生电路222_n,第一偏移电压vos1到第n偏移电压vosn的幅度可以彼此不同。在示例实施例中,第一偏移电压vos1到第n偏移电压vosn中的相邻偏移电压之间的幅度差可以相同。在一些示例实施例中,第一偏移电压vos1到第n偏移电压vosn中的相邻偏移电压之间的幅度差可以变化。

71.第二ldo调节器220可以向输出节点n1(参见图3)输出包括由至少一个使能的辅助电流产生电路产生的辅助电流的第二负载电流i2。

72.进一步参考图8b,系统负载的第二操作区域opr2可以被再划分为第一子操作区域opr2_1到第n子操作区域opr2_n。第二参考电流i_ref2_1到第n参考电流iref2_n可以指示用于区分第一子操作区域opr2_1到第n子操作区域opr2_n的参考电流。

73.在示例实施例中,在第一时间点t13和第二时间点t23之间的时段中,其中系统负载在第一子操作区域opr2_1中操作,第一辅助电流产生电路222_1可以被使能。在第二时间点t23和第三时间点t33之间的时段中,其中系统负载在第二子操作区域opr2_2中操作,第二辅助电流产生电路222_2可以额外地被使能。以这种方式,在第四时间点t43和第五时间点t53之间的时段中,其中系统负载在第n子操作区域opr2_n中操作,第n辅助电流产生电路222_n可以额外地被使能,使得第一辅助电流产生电路222_1到第n辅助电流产生电路222_n全都被使能。此后,随着负载电流lc(参见图3)减小,第一辅助电流产生电路222_1至第n辅助电流产生电路222_n可以以相反的顺序被顺序禁用。

74.进一步参考图8c,电源电压可以当系统负载在第一操作区域opr1中操作时保持目标电源电压t_vdd的幅度,并且当系统负载在第二操作区域opr2中操作时开始下降。当电源电压进入第一范围r1时,第一辅助电流产生电路222_1可以使能以主要减少或防止电源电压下降。当电源电压连续下降并进入第二范围r2时,第二辅助电流产生电路222_2可以额外地被使能以二次减少或防止电源电压下降。此后,当电源电压连续下降并进入第n范围rn时,第n辅助电流产生电路222_n可以额外地被使能以减少或防止电源电压的第n次下降。

75.根据本发明构思的示例实施例的第二ldo调节器220可以根据情况选择性地使能第一辅助电流产生电路222_1到第n辅助电流产生电路222_n,使得第二ldo调节器220的有效功耗是可能的。

76.图9是图2的操作s120中的集成电路的具体操作方法的流程图。

77.参考图9,在操作s110(图2)之后,在操作s121中,集成电路可以基于电源电压的下降程度来使能多个辅助电流产生电路中的至少一个。例如,由集成电路使能的辅助电流产生电路的数量可以随着电源电压从目标电源电压的下降程度的增加而增加。在操作s122中,集成电路可以通过使能的至少一个辅助电流产生电路向系统负载供应辅助电流。

78.图10a是根据本发明构思的示例实施例的电源电路300的电路图,以及图10b是用于描述根据系统负载的操作区域的图10a的第二ldo调节器320的操作的曲线图。图10a中所示的电源电路300仅仅是用于描述本发明构思的技术思想的示例,并因此本发明构思不限于此,并且将充分理解,电源电路300的实现示例可以是多种示例。在图10a中,参考图3或4c进行的描述不再重复。

79.参考图10a,第二ldo调节器320可以包括比较电路321、第一辅助电流产生电路322_1、第二辅助电流产生电路322_2、第一偏移电压源os1和/或第二偏移电压源os2。尽管图10a示出了包括两个辅助电流产生电路的第二ldo调节器320,例如第一辅助电流产生电路322_1和第二辅助电流产生电路322_2,但是第二ldo调节器320可以包括更多数量的辅助电流产生电路,如图8a的第二ldo调节器220。

80.在示例实施例中,第一辅助电流产生电路322_1可以包括第四电阻器r4和/或第二晶体管tr21。第四电阻器r4的一端可以连接到通过其接收第二电源电压vdd2的端子,并且其另一端可以连接到第二晶体管tr21的源极端子。第二晶体管tr21的漏极端子可以连接到输出节点n1,并且其栅极端子可以从比较电路321接收第二栅极电压vg_aux1。第二栅极电压vg_aux1可以被称为第一辅助电流产生电路322_1的使能控制信号。

81.在示例实施例中,第二辅助电流产生电路322_2可以包括第五电阻器r5和/或第三晶体管tr22。第五电阻器r5的一端可以连接到通过其接收第二电源电压vdd2的端子,并且其另一端可以连接到第三晶体管tr22的源极端子。第三晶体管tr22的漏极端子可以连接到输出节点n1,并且其栅极端子可以从比较电路321接收第三栅极电压vg_aux2。第三栅极电压vg_aux2可以被称为第二辅助电流产生电路322_2的使能控制信号。

82.在示例实施例中,第二晶体管tr21和第三晶体管tr22的电流驱动能力可以彼此相同或不同。例如,第二晶体管tr21的长宽比可以与第三晶体管tr22的长宽比相同或不同。例如,当第一辅助电流产生电路322_1的使能频率大于第二辅助电流产生电路322_2的使能频率时,可以实现第二晶体管tr21的电流驱动能力优于第三晶体管tr22的电流驱动能力。然而,这仅仅是示例实施例,并因此本发明构思不限于此,并且辅助电流产生电路中的晶体管可以不同地实现。

83.在示例实施例中,比较电路321可以接收第一内部节点n1_int的第一电压v1、其中第一偏移电压源os1的偏移电压被添加到第二内部节点n2_int的电压的第二电压v2_aux1、以及其中第二偏移电压源os2的偏移电压被添加到第二电压v2_aux1的第三电压v2_aux2。

84.在示例实施例中,比较电路321可以将第一电压v1与第二电压v2_aux1进行比较,基于比较结果产生第二栅极电压vg_aux1,并然后将第二栅极电压vg_aux1提供给第二晶体管tr21的栅极端子。比较电路321可以将第一电压v1与第三电压v2_aux2进行比较,基于比较结果产生第三栅极电压vg_aux2,并然后将第三栅极电压vg_aux2提供给第三晶体管tr22的栅极端子。

85.例如,当第一电压v1大于第二电压v2_aux1时,比较电路321可以使能第一辅助电流产生电路322_1,并且被使能的第一辅助电流产生电路322_1可以从第二电源电压vdd2产生第一辅助电流i2_aux1,并且将第一辅助电流i2_aux1供应给输出节点n1。当第一电压v1大于第三电压v2_aux2时,比较电路321可以使能第二辅助电流产生电路322_2,并且被使能的第二辅助电流产生电路322_2可以从第二电源电压vdd2产生第二辅助电流i2_aux2,并且

将第二辅助电流i2_aux2供应给输出节点n1。

86.进一步参考图10b,系统负载的第二操作区域opr2可以被再划分为第一子操作区域opr2_1和第二子操作区域opr2_2。第二参考电流iref2_1和第三参考电流iref2_2可以指示用于区分第一子操作区域opr2_1和第二子操作区域opr2_2的参考电流。

87.在示例实施例中,在第一时间点t14和第二时间点t24之间的时段中,其中系统负载在第一子操作区域opr2_1中操作,第一辅助电流产生电路322_1可以被使能。在第二时间点t24和第三时间点t34之间的时段中,其中系统负载在第二子操作区域opr2_2中操作,第二辅助电流产生电路322_2可以额外地被使能。此后,在第四时间点t44和第五时间点t54之间的时段中,其中系统负载再次在第一子操作区域opr2_1中操作,第二辅助电流产生电路322_2可以被禁用。在其中系统负载再次在第一操作区域opr1中操作的第五时间点t54之后,第一辅助电流产生电路322_1可以被禁用。

88.图11是根据本发明构思的示例实施例的第一ldo调节器410的电路图。因为图11中所示的第一ldo调节器410仅仅是示例实施例,所以本发明构思不限于此,并且可以实现其中执行第一ldo调节器的前述操作的多种示例实施例。

89.参考图11,第一ldo调节器410可以包括第一晶体管tr11至第十四晶体管tr114、第一电阻器r11至第四电阻器r14、电容器c11和/或第一电流源cs1和第二电流源cs2。如上所述,第一电流源cs1是负载电流源,并且可以输出由连接到第一ldo调节器410的系统负载(未示出)汲取的负载电流lc。第一、第二、第四、第六、第七、第十、第十二和/或第十四晶体管tr11、tr12、tr14、tr16、tr17、tr110、tr112和/或tr114可以是p沟道晶体管,并且其他晶体管,例如第三、第五、第八、第九、第十一和/或第十三晶体管tr13、tr15、tr18、tr19、tr111和/或tr113,可以是n沟道晶体管。

90.第一晶体管tr11的源极端子可以连接到通过其接收第一电源电压vdd1的端子,其漏极端子可以连接到输出节点n1,并且其栅极端子可以连接到第十二晶体管tr112的栅极端子以接收第一栅极电压vg_main。第一晶体管tr11可以响应于第一栅极电压vg_main从第一电源电压vdd1产生第一负载电流i_main。输出节点n1的电压是电源电压sv,并且可以被供应给系统负载(未示出)。输出节点n1可以是参考图3等描述的输出节点n1。

91.第一电阻器r11的一端可以连接到输出节点n1,并且其另一端可以连接到第二电阻器r12的一端。第二电阻器r12的另一端可以连接到地。第一电阻器r11和第二电阻器r12可以从电源电压sv产生反馈电压vfb。电容器c11的一端可以连接到输出节点n1,并且其另一端可以连接到地。

92.第二晶体管t12和第四晶体管t14、第十晶体管t10和第十四晶体管t114以及第十一晶体管t111和第十三晶体管t113可以形成各自的电流镜。可以根据形成电流镜的两个晶体管的幅度比来调整要辐射的电流的幅度。例如,晶体管的尺寸可以由晶体管的长宽比来定义。

93.第十四晶体管tr114的源极端子可以连接到通过其接收第一电源电压vdd1的端子,其栅极端子可以接收偏置电压vb1,并且其漏极端子可以连接到第六晶体管tr16和第七晶体管tr17的源极端子。第十四晶体管tr114可以响应于偏置电压vb1从第一电源电压vdd1产生第二偏置电流ib2,并将第二偏置电流ib2输出到第六晶体管tr16和第七晶体管tr17的源极端子。

94.第六晶体管tr16的栅极端子可以接收参考电压vref,并且其漏极端子可以连接到第二内部节点n2_int。第二内部节点n2_int可以是参考图3等描述的第二内部节点n2_int。第七晶体管tr17的栅极端子可以接收反馈电压vfb,并且其漏极端子可以连接到第一内部节点n1_int。第一内部节点n1_int可以是参考图3等描述的第一内部节点n1_int。第一内部节点n1_int和第二内部节点n2_int可以连接到将参考图12描述的第二ldo调节器420(参见图12)。

95.第三电阻器r13的一端可以连接到第二内部节点n2_int,并且其另一端可以连接到第四电阻器r14的一端以及第八晶体管tr18和第九晶体管tr19的栅极端子。第四电阻器r14的另一端可以连接到第一内部节点n1_int。例如,第三电阻器r13的电阻值可以与第四电阻器r14的电阻值相同,并且第三电阻器r13和第四电阻器r14可以增加第一ldo调节器410的电阻值,从而提高第一ldo调节器410的增益。第八晶体管tr18的漏极端子可以连接到第二内部节点n2_int,并且其源极端子可以连接到地。第九晶体管tr19的漏极端子可以连接到第一内部节点n1_int,并且其源极端子可以连接到地。

96.例如,当参考电压vref的幅度与反馈电压vfb的幅度相同时,第一电压v1的幅度可以与第二电压v2的幅度相同。此后,当反馈电压vfb小于参考电压vref时,第一电压v1可以大于第二电压v2。下面将要描述的第二ldo调节器420可以基于第一电压v1和第二电压v2之间的差产生第二负载电流。

97.第三电阻器r13、第四电阻器r14、第八晶体管tr18和第九晶体管tr19可以包括在第一共模反馈(cmfb)电路1

st cmfb_ckt中。即,第八晶体管tr18和第九晶体管tr19可以具有二极管连接的n型金属氧化物半导体(nmos)结构。

98.随着负载电流lc增加,第一负载电流i_main可能增加,并因此第一栅极电压vg_main可能降低,从而导致第一晶体管tr11的电阻值降低。第一晶体管tr11的电阻值的降低可能导致第一ldo调节器410的放大增益的降低,因此,为了减少或防止这种情况,可以应用自适应偏置电路ab_ckt。

99.第十晶体管tr110、第十一晶体管tr111、第十二晶体管tr112、第十三晶体管tr113和第二电流源cs2可以包括在自适应偏置电路ab_ckt中。在示例实施例中,第十二晶体管tr112可以与第一晶体管tr11共享第一栅极电压vg_main。随着提供给第十二晶体管tr112的第一栅极电压vg_main降低,由第十一晶体管tr111和第十三晶体管tr113的电流镜产生的另外电流iex可能增加。第十晶体管tr110可以通过其漏极端子输出另外电流iex和第一偏置电流ib1的总和电流。因为第十四晶体管tr114通过共享第一偏置电压vb1与第十晶体管tr110形成电流镜,所以第十四晶体管tr114可以通过其漏极端子输出与总和电流ib1+iex成比例的第二偏置电流ib2。因为额外电流iex响应于降低的第一栅极电压vg_main而增加,因此第二偏置电流ib2可以增加,并且第一ldo调节器410的放大增益可以由增加的第二偏置电流ib2来保持。

100.在示例实施例中,自适应偏置电路ab_ckt可以通过调节第二偏置电流ib2来稳定第一ldo调节器410的放大增益。在一些示例实施例中,自适应偏置电路ab_ckt可以从第一ldo调节器410中省略。

101.图12是根据本发明构思的示例实施例的第二ldo调节器420的电路图。因为图12中所示的第二ldo调节器420仅仅是示例实施例,所以本发明构思不限于此,并且可以实现其

中执行第二ldo调节器的前述操作的多种示例实施例。

102.参考图12,第二ldo调节器420可以包括第一晶体管tr21至第十三晶体管tr213、第一电阻器r21和第二电阻器r22、和/或第一电容器c21和第二电容器c22。第一、第二、第三、第五、第七、第八、第十一和/或第十三晶体管tr21、tr22、tr23、tr25、tr27、tr28、tr211、tr213可以是p沟道晶体管,并且其他晶体管,例如第四、第六、第九、第十和/或第十二晶体管tr24、tr26、tr29、tr210、tr212可以是n沟道晶体管。

103.第一晶体管tr21的源极端子可以连接到通过其接收第二电源电压vdd2的端子,其栅极端子可以接收第二栅极电压vg_aux1,并且其漏极端子可以连接到输出节点n1。第一晶体管tr21可以响应于第二栅极电压vg_aux1产生第一辅助电流i2_aux1。第一晶体管tr21可以包括在上述第一辅助电流产生电路322_1中。

104.第二晶体管tr22的源极端子可以连接到通过其接收第二电源电压vdd2的端子,其栅极端子可以接收第三栅极电压vg_aux2,并且其漏极端子可以连接到输出节点n1。第二晶体管tr22可以响应于第三栅极电压vg_aux2产生第二辅助电流i2_aux2。第二晶体管tr22可以包括在上述第二辅助电流产生电路322_2中。第一电容器c21的一端和第二电容器c22的一端可以分别连接到第一晶体管tr21和第二晶体管tr22的栅极端子。

105.第三晶体管tr23和第五晶体管tr25中的每一个可以与第十一晶体管tr211形成电流镜。第三晶体管tr23和第五晶体管tr25的每个源极端子可以连接到通过其接收第二电源电压vdd2的端子。第三晶体管tr23和第四晶体管tr24可以共享输出第二栅极电压vg_aux1的节点,并且可以被实现为产生第二栅极电压vg_aux1,其中考虑了图10a的第一偏移电压源os1的第一偏移电压。第五晶体管tr25和第六晶体管tr26可以共享输出第三栅极电压vg_aux2的节点,并且可以被实现为产生第三栅极电压vg_aux2,其中考虑了图10a的第一偏移电压源os1的第一偏移电压和第二偏移电压源os2的第二偏移电压。例如,第十一晶体管tr211与第十二晶体管tr212的尺寸比可以不同于第三晶体管tr23与第四晶体管tr24的尺寸比以及第五晶体管tr25与第六晶体管tr26的尺寸比中的每一个。例如,当第十一晶体管tr211与第十二晶体管tr212的尺寸比为2:1时,第三晶体管tr23与第四晶体管tr24的尺寸比为4:1,以及第五晶体管tr25与第六晶体管tr26的尺寸比为8:1。通过这样做,可以不同地控制第二栅极电压vg_aux1的电平转换定时和第三栅极电压vg_aux2的电平转换定时,并且可以分别响应于第二栅极电压vg_aux1和第三栅极电压vg_aux2顺序地使能第一辅助电流产生电路和第二辅助电流产生电路。

106.在一些示例实施例中,可以省略单独的偏移电压源。在一些示例实施例中,第三晶体管tr23与第四晶体管tr24的尺寸比以及第五晶体管tr25与第六晶体管tr26的尺寸比可以根据操作所需的偏移电压而变化。

107.第三晶体管tr23至第六晶体管tr26可以包括在双输出电路do_ckt中,第三晶体管tr23和第四晶体管tr24可以被定义为第一输出电路,以及第五晶体管tr25和第六晶体管tr26可以被定义为第二输出电路。此外,第三晶体管tr23和第五晶体管tr25可以被称为上拉(pull-up)晶体管,以及第四晶体管tr24和第六晶体管tr26可以被称为下拉(pull-down)晶体管。

108.第十三晶体管tr213的源极端子可以连接到通过其接收第二电源电压vdd2的端子,其栅极端子可以接收第二偏置电压vb2,并且其漏极端子可以连接到第七晶体管tr27和

第八晶体管tr28的源极端子。第十三晶体管tr213可以响应于第二偏置电压vb2输出第三偏置电流ib3。

109.第七晶体管tr27的栅极端子可以接收第一电压v1,并且第八晶体管tr28的栅极端子可以接收第二电压v2。第一电压v1可以对应于图11的第一电压v1,并且第二电压v2可以对应于图11的第二电压v2。第七晶体管tr27的漏极端子可以连接到第一电阻器r21的一端、第九晶体管tr29的漏极端子和第十二晶体管tr212的栅极端子中的每一个。第八晶体管tr28的漏极端子可以连接到第二电阻器r22的一端、第十晶体管tr210的漏极端子、第四晶体管tr24的栅极端子和第六晶体管tr26的栅极端子中的每一个。第一电阻器r21的另一端可以连接到第二电阻器r22的另一端和第九晶体管tr29的栅极端子以及第十晶体管tr210的栅极端子中的每一个。例如,第一电阻器r21的电阻值可以与第二电阻器r22的电阻值相同,并且第一电阻器r21和第二电阻器r22可以增加第二ldo调节器420的电阻值,从而提高第二ldo调节器420的增益。在示例实施例中,第七晶体管tr27的长宽比可以不同于第八晶体管tr28的长宽比。

110.第一电阻器r21、第二电阻器r22、第九晶体管tr29和第十晶体管tr210可以包括在第二cmfb电路2

nd cmfb_ckt中。即,第九晶体管tr29和第十晶体管tr210可以具有二极管连接的nmos结构。

111.第二ldo调节器420可以基于第一电压v1和第二电压v2之间的差产生第一辅助电流i2_aux1和第二辅助电流i2_aux2中的至少一个。上文已经描述了第二ldo调节器420的特定操作,因此在此省略。

112.图13是根据本发明构思的示例实施例的显示驱动器集成电路(ddi)1000的框图。

113.参考图13,ddi 1000可以包括第一端子t1、第二端子t2、第三端子t3、第一逻辑电路1010、第一ldo调节器1030、第二ldo调节器1040和/或第二逻辑电路1020。第一端子t1可以通过第一外部电阻器rext1连接到电源管理集成电路(pmic)1100,以接收第一电源电压。第二端子t2可以通过第二外部电阻器rext2连接到pmic 1100,以接收第二电源电压。第三端子t3可以连接到外部电容器cext,以规划第一ldo调节器1030和第二ldo调节器1040的稳定操作。

114.通过第一端子t1接收的第一电源电压可以小于或等于通过第二端子t2接收的第二电源电压。ddi 1000可以通过独立的端子(例如第一端子t1和第二端子t2)从pmic 1100接收不同的电源电压。第一逻辑电路1010可以通过经由第一端子t1直接接收第一电源电压来执行特定操作。第二逻辑电路1020可以通过从第一ldo调节器1030和第二ldo调节器1040接收电源电压来执行特定操作。第一逻辑电路1010可以执行与第二逻辑电路1020不同的操作。

115.第一ldo调节器1030可以连接到第一端子t1,以接收第一电源电压,从第一电源电压产生第一负载电流,并将第一负载电流供应给第二逻辑电路1020。随着第二逻辑电路1020的功耗增加,由第二逻辑电路1020汲取的负载电流增加,因此,第一负载电流可能增加。当第一负载电流由于第一ldo调节器1030的限制而饱和时,根据本发明构思的示例实施例的第二ldo调节器1040可以产生第二负载电流,并且将第二负载电流另外供应给第二逻辑电路1020。

116.在示例实施例中,第二ldo调节器1040可以连接到第一ldo调节器1030的第一内部

节点n1_int和第二内部节点n2_int,并且当第一内部节点n1_int和第二内部节点n2_int的电压之间的差大于或等于参考值时,第二ldo调节器1040可以从通过第二端子t2接收的第二电源电压产生第二负载电流,并且将第二负载电流输出到第二逻辑电路1020。参考图1等描述的多种示例实施例可以应用于第二ldo调节器1040,并且上文已经对其进行了具体描述,因此在此省略。

117.第二逻辑电路1020可以通过接收从通过第一端子t1和第二端子t2接收的第一电源电压和第二电源电压中的至少一个产生的电源电压来操作,并因此第二逻辑电路1020的功耗范围可以被扩大,从而执行多种操作。

118.图14是根据本发明构思的示例实施例的电子设备2300的框图。

119.电子设备2300可以包括例如图1所示的集成电路10的全部或一部分。参考图14,电子设备2300可以包括至少一个应用处理器(ap)2310、通信模块2320、用户识别模块(sim)卡2324、存储器2330、传感器模块2340、输入设备2350、显示模块2360、接口2370、音频模块2380、相机模块2391、电源管理模块2395、电池2396、指示器2397和/或电机2398。

120.至少一个ap 2310可以通过运行操作系统或应用程序来控制连接到至少一个ap 2310的多个硬件或软件组件,并且处理和计算包括多媒体数据的多种数据。至少一个ap 2310可以由例如片上系统(soc)来实现。根据示例实施例,至少一个ap 2310可以进一步包括图形处理单元(gpu)(未示出)。

121.通信模块2320可以在电子设备2300和通过网络与其连接的其他电子设备之间的通信中执行数据发送和接收。根据示例实施例,通信模块2320可以包括蜂窝模块2321、wifi模块2323、蓝牙(bt)模块2325、全球定位系统(gps)模块2327、近场通信(nfc)模块2328和射频(rf)模块2329。

122.蜂窝模块2321可以通过通信网络(例如,长期演进(lte)网络、高级lte(lte-a)网络、码分多址(cdma)网络、宽带cdma(wcdma)网络、通用移动电信系统(umts)网络、wibro网络、全球移动通信系统(gsm)网络等)提供语音呼叫、视频呼叫、文本服务、互联网服务等。此外,蜂窝模块2321可以通过使用例如sim模块(例如,sim卡2324)来识别和认证通信网络中的电子设备。根据示例实施例,蜂窝模块2321可以执行至少一个ap2310提供的至少一些功能。例如,蜂窝模块2321可以执行多媒体控制功能的至少一部分。

123.蜂窝模块2321可以包括通信处理器(cp)。此外,蜂窝模块2321可以由例如soc实现。尽管图14示出了诸如蜂窝模块2321(例如,cp)、存储器2330和电源管理模块2395的组件是与至少一个ap 2310分离的组件,但是根据示例实施例,至少一个ap 2310可以被实现为包括至少一些(例如,蜂窝模块2321)上述组件。

124.至少一个ap 2310或蜂窝模块2321(例如,cp)可以在易失性存储器上加载从非易失性存储器和与其连接的其他组件中的至少一个所接收的命令或数据,并处理加载的命令或数据。此外,至少一个ap 2310或蜂窝模块2321可以在非易失性存储器中存储从至少一个其他组件接收或由至少一个其他组件产生的数据。

125.wifi模块2323、bt模块2325、gps模块2327和/或nfc模块2328中的每一个可以包括例如被配置为处理通过对应模块发送和接收的数据的处理器。尽管图14示出了蜂窝模块2321、wifi模块2323、bt模块2325、gps模块2327和nfc模块2328是单独的块,但是根据示例实施例,蜂窝模块2321、wifi模块2323、bt模块2325、gps模块2327和/或nfc模块2328中的至

少一些(例如,两个或更多个)可以被包括在集成芯片(ic)或ic封装中。例如,分别对应于蜂窝模块2321、wifi模块2323、bt模块2325、gps模块2327和/或nfc模块2328的处理器中的至少一些(例如,对应于蜂窝模块2321的cp和对应于wifi模块2323的wifi处理器)可以由一个soc实现。

126.rf模块2329可以发送和接收数据,例如rf信号。rf模块2329可以包括例如收发器、功率放大模块(pam)、频率滤波器、低噪声放大器(lna)等(尽管未示出)。此外,rf模块2329还可以包括被配置为在无线通信中的自由空间中发送和接收电磁波的组件(例如导体或导线)。尽管图14示出了蜂窝模块2321、wifi模块2323、bt模块2325、gps模块2327和/或nfc模块2328共享rf模块2329,但是根据示例实施例,蜂窝模块2321、wifi模块2323、bt模块2325、gps模块2327和/或nfc模块2328中的至少一个可以通过分离的rf模块发送和接收rf信号。

127.sim卡2324可以包括sim,并且可以插入在电子设备2300的特定位置形成的插槽(slot)中。sim卡2324可以包含唯一的标识信息(例如,集成电路卡标识符(iccid))或用户信息(例如,国际移动用户识别码(imsi))。

128.存储器2330可以包括内部存储器2332和外部存储器2334。内部存储器2332可以包括例如易失性存储器(例如,动态随机存取存储器(dram)、静态ram(sram)、同步动态ram(sdram)等)和非易失性存储器(例如,一次性可编程只读存储器(otprom)、可编程rom(prom)、可擦除可编程rom(eprom)、电可擦除可编程rom(eeprom)、掩膜rom、闪存rom、nand闪存、nor闪存等)中的至少一种。

129.内部存储器2332可以是固态驱动器(ssd)。外部存储器2334可以进一步包括闪存驱动器,例如紧凑型闪存(cf)卡、安全数字(sd)卡、微型安全数字(micro-sd)卡、微型安全数字(mini-sd)卡、极限数字(xd)卡、记忆棒等。外部存储器2334可以通过多种接口功能性地连接到电子设备2300。根据示例实施例,电子设备2300可以进一步包括诸如硬盘驱动器的存储设备(或存储介质)。

130.传感器模块2340可以测量电子设备2300的物理量或检测电子设备2300的操作状态,并将测量或检测的信息转换成电信号。传感器模块2340可以包括例如手势传感器2340a、陀螺仪传感器2340b、大气传感器2340c、磁传感器2340d、加速度传感器2340e、抓握传感器2340f、接近传感器2340g、颜色传感器(例如,红色、绿色和蓝色(rgb)传感器)2340h、生物传感器2340i、温度/湿度传感器2340j、照度传感器2340k中的至少一个。另外或替代地,传感器模块2340可以包括例如嗅觉(电子鼻)传感器(未示出)、肌电图(emg)传感器(未示出)、脑电图(eeg)传感器(未示出)、心电图(ecg)传感器(未示出)、红外(ir)传感器(未示出)、虹膜传感器(未示出)、指纹传感器(未示出)等。传感器模块2340可以进一步包括控制电路,被配置为控制包括在传感器模块2340中的至少一个传感器。

131.输入设备2350可以包括触摸面板2352、(数字)笔传感器2354、键2356或超声波输入设备2358。触摸面板2352可以以例如静电方式、压敏方式、ir方式和超声波方式中的至少一种方式识别触摸输入。此外,触摸面板2352可以进一步包括控制电路。以静电方式,可以识别物理接触或近距离接触。触摸面板2352可以进一步包括触觉层。在一些示例实施例中,触摸面板2352可以向用户提供触觉反应。

132.(数字)笔传感器2354可以通过使用例如与接收用户的触摸输入相同或相似的方法来实现,或者使用分离的片用于识别。键2356可以包括例如物理按钮、光学键或小键盘。

超声波输入设备2358是能够通过被配置为产生超声波信号的输入工具通过由电子设备2300中的麦克风(例如,麦克风2388)检测声波来确认数据的设备,并且可以执行无线识别。根据示例实施例,电子设备2300可以通过使用通信模块2320从与其连接的外部设备(例如,计算机或服务器)接收用户输入。

133.显示模块2360可以包括显示面板2362和ddi 2363。显示面板2362可以包括例如液晶显示器(lcd)、有源矩阵有机发光二极管(am-oled)显示器等。显示面板2362可以被实现为例如柔性的、透明的或可穿戴的。显示面板2362可以与触摸面板2352形成一个模块。显示面板2362可以包括多个区域。替代地,可以包括多个显示面板2362。

134.显示面板2362可以用全息设备或投影仪代替。全息设备可以通过使用光的干涉在空气中显示立体图像。投影仪可以通过在屏幕上投射光来显示图像。屏幕可以位于例如电子设备2300的内部或外部。

135.ddi 2363可以从至少一个ap 2310接收显示数据,并基于接收的显示数据驱动显示面板2362。根据本发明构思的示例实施例的ddi 2363可以包括被配置为覆盖系统负载的宽功耗范围的第一ldo调节器和第二ldo调节器(未示出),并且第二ldo调节器可以连接到第一ldo调节器的内部节点,以产生用于补充第一ldo调节器的第一负载电流的第二负载电流。参考图1等描述的示例实施例可以应用于ddi 2363,并且在此省略其具体描述。

136.接口2370可以包括例如高清多媒体接口(hdmi)2372、通用串行总线(usb)接口2374、光学接口2376或超小型(d-sub)接口2378。另外或替代地,接口2370可以包括例如移动高清链路(mhl)接口、sd卡/多媒体卡(mmc)接口或红外数据协会(irda)标准接口。

137.音频模块2380可以将声音转换成电信号,反之亦然。音频模块2380可以处理通过例如扬声器2382、接收器2384、耳机2386、麦克风2388等输入或输出的声音信息。

138.相机模块2391是能够捕捉静止图像或运动画面的设备,并且根据示例实施例,相机模块2391可以包括一个或多个图像传感器(例如,前传感器和后传感器)、镜头(未示出)、图像信号处理器(isp)(未示出)和/或闪光灯(例如,发光二极管(led)或氙灯)(未示出)。

139.电源管理模块2395可以管理电子设备2300的电源。尽管未示出,功率管理模块2395可以包括例如pmic、充电器ic和/或电池或燃料表(fuel gauge)。在一些示例实施例中,功率管理模块2395可以包括应用本发明构思的技术思想的第一ldo调节器和第二ldo调节器,而不是ddi 2363,并且当向ddi2363提供电源电压时,本发明构思的技术思想可以应用于功率管理模块2395。

140.例如,pmic可以安装在集成电路或soc半导体中。充电方案可以划分为有线充电方案和无线充电方案。充电器ic可以给电池2396充电,并减少或防止来自充电器的过电压或过电流的流入。根据示例实施例,充电器ic可以包括基于有线充电方案和无线充电方案中的至少一个的充电器ic。无线充电方案可以包括例如磁共振方案、磁感应方案、电磁波方案等,并且可以添加用于无线充电的另外的电路,例如线圈回路、谐振电路、整流器等。

141.电池量表(battery gauge)可以测量例如电池2396的剩余容量及其在充电期间的电压、电流或温度。电池2396可以存储或产生电(electricity),并通过使用存储或产生的电(electricity)向电子设备2300供电。电池2396可以包括例如可充电电池或太阳能电池。

142.指示器2397可以指示电子设备2300或其一部分(例如,至少一个ap2310)的某一状态,例如,启动(boot)状态、消息收发状态、充电状态等。电机2398可以将电信号转换成机械

振动。尽管未示出,电子设备2300可以包括被配置为支持移动tv的处理设备(例如,gpu)。被配置为支持移动tv的处理设备可以根据例如数字多媒体广播(dmb)标准、数字视频广播(dvb)标准、媒体流标准等来处理媒体数据。

143.上面公开的一个或多个元件可以包括或实现在一个或多个处理电路(诸如包括逻辑电路的硬件)中;硬件/软件组合(诸如运行软件的处理器);或其组合。例如,更具体地,处理电路可以包括但不限于中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

144.尽管已经参照本发明的示例实施例具体示出和描述了本发明构思,但是应当理解,在不脱离所附权利要求的精神和范围的情况下,可以在形式和细节上对其进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1