一种兼容源型和漏型的数字量输入装置的制作方法

1.本技术涉及电子电路技术领域,特别是一种兼容源型和漏型的数字量输入装置。

背景技术:

2.在plc应用领域,数字量输入模块外接设备一般是源型设备和漏型设备,一般市面上的数字量输入模块要么只能接源型设备,要么只能接漏型设备。

技术实现要素:

3.基于此,有必要针对上述技术问题,提供一种兼容源型和漏型的数字量输入装置,能够兼容源型和漏型,既可以接源型设备也可以接漏型设备。

4.一种兼容源型和漏型的数字量输入装置,包括:信号处理模块、处理器模块和断线检测模块;

5.所述信号处理模块的输入端与信号输入端相连,输出端与处理器模块的输入端相连;

6.所述处理器模块的输入端与信号处理模块的输出端以及所述断线检测模块的输出端相连,输出端与信号输出端相连;

7.所述断线检测模块的输入端与信号输入端相连;

8.所述信号处理模块和所述断线检测模块同时接收信号输入端输入的数字量信号,并分别经过运放和光耦判断所述数字量信号的电平类型,所述处理器模块根据所述电平类型判断所述数字量信号属于源型输入或漏型输入。

9.在一个实施例中,还包括:控制模块;

10.所述控制模块的输入端与所述处理器模块的输出端相连,输出端与所述信号处理模块的输入端相连;

11.所述控制模块根据所述处理器模块的信号控制内部光耦的状态,与信号处理模块和断线检测模块一起判断断线状态。

12.在一个实施例中,所述信号处理模块包括:第一比较器和第一光耦;

13.所述第一比较器的第一端与电源相连,第二端与信号输入端相连,第三端与第一光耦的第二端相连;

14.所述第一光耦的第一端与电源相连,第三端与处理器模块相连。

15.在一个实施例中,所述信号处理模块还包括:第一二极管;

16.所述第一二极管的第一端同时与信号输入端和第一比较器的第二端相连,第二端与地相连。

17.在一个实施例中,所述断线检测模块包括:第二比较器和第二光耦;

18.所述第二比较器的第一端与电源相连,第二端与信号输入端相连,第三端与第二光耦的第一端相连;

19.所述第二光耦的第二端与地相连,第三端与处理器模块相连。

20.在一个实施例中,所述断线检测模块还包括:第二二极管;

21.所述第二二极管的第一端同时与信号输入端和第二比较器的第二端相连,第二端与地相连。

22.在一个实施例中,所述控制模块包括:第三光耦;

23.所述第三光耦的第一端与处理器模块相连,第二端与电源相连,第三端输出输入信号给信号处理模块和断线检测模块。

24.在一个实施例中,所述第一比较器和所述第二比较器的型号为:lm2901xp。

25.在一个实施例中,所述第一光耦、所述第二光耦和所述第三光耦的型号为:or-3h7-4。

26.在一个实施例中,所述第一二极管和所述第二二极管的型号为:mmsz5245b。

27.上述兼容源型和漏型的数字量输入装置,设置了信号处理模块、处理器模块和断线检测模块,信号输入端输入的数字量信号同时被信号处理模块和断线检测模块接收,分别经过运放和光耦后输出高电平或低电平,并经处理器模块处理,识别数字量信号属于源型输入或漏型输入,从而实现了源型设备和漏型设备的兼容。

附图说明

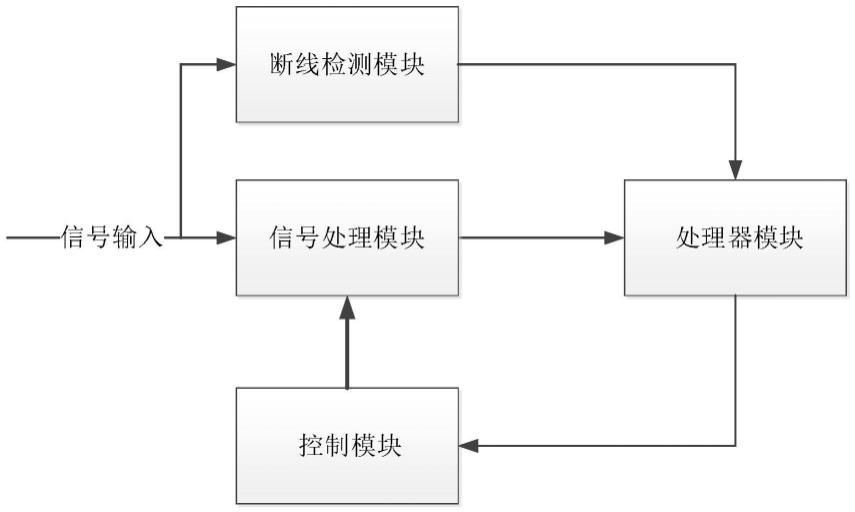

28.图1为一个实施例中兼容源型和漏型的数字量输入装置的结构示意图;

29.图2为一个实施例中兼容源型和漏型的数字量输入装置的电路示意图;

30.图3为一个实施例中信号处理模块的示意图;

31.图4为一个实施例中信号处理模块a1部分的放大示意图;

32.图5为一个实施例中信号处理模块a2部分的放大示意图;

33.图6为一个实施例中断线检测模块的示意图;

34.图7为一个实施例中断线检测模块b1部分的放大示意图;

35.图8为一个实施例中断线检测模块b2部分的放大示意图;

36.图9为一个实施例中控制模块的示意图;

37.图10为一个实施例中处理器模块的示意图;

38.图11为一个实施例中处理器模块d1部分的放大示意图;

39.图12为一个实施例中处理器模块d2部分的放大示意图;

40.图13为一个实施例中处理器模块d3部分的放大示意图;

41.图14为一个实施例中处理器模块d4部分的放大示意图。

具体实施方式

42.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

43.如图1所示,本技术提供的一种兼容源型和漏型的数字量输入装置,在一个实施例中,包括:信号处理模块、处理器模块和断线检测模块;

44.信号处理模块的输入端与信号输入端相连,输出端与处理器模块的输入端相连;

45.处理器模块的输入端与信号处理模块的输出端以及断线检测模块的输出端相连,

输出端与信号输出端相连;

46.断线检测模块的输入端与信号输入端相连;

47.信号处理模块和断线检测模块同时接收信号输入端输入的数字量信号,并分别经过运放和光耦判断数字量信号的电平类型,处理器模块根据电平类型判断数字量信号属于源型输入或漏型输入。

48.优选地,信号处理模块包括:第一比较器和第一光耦;

49.第一比较器的第一端与电源相连,第二端与信号输入端相连,第三端与第一光耦的第二端相连;第一光耦的第一端与电源相连,第三端与处理器模块相连。

50.断线检测模块包括:第二比较器和第二光耦;

51.第二比较器的第一端与电源相连,第二端与信号输入端相连,第三端与第二光耦的第一端相连;第二光耦的第二端与地相连,第三端与处理器模块相连。

52.如图2所示,为兼容源型和漏型的数字量输入装置的电路示意图,其中,a为信号处理模块的电路,具体如图3所示(图3中a1和a2部分的放大示意图如图4和图5所示),b为断线检测模块的电路,具体如图6所示(图6中b1和b2部分的放大示意图如图7和图8所示),c为控制模块的电路,具体如图9所示,d为处理器模块的电路,具体如图10所示(图10中d1、d2、d3和d4部分的放大示意图如图11、图12、图13和图14所示)。

53.在本实施例中,外接设备的输入信号不能直接进入处理器模块,只能先经过信号处理模块对信号进行处理;信号处理模块用于实现源型信号和漏型信号的处理,具体是由运放(即第一比较器)进行数字量信号的处理,输出一个确定的高电平或者低电平给到第一光耦,促使第一光耦的开启和关闭;第一光耦的主要作用是进行信号的隔离,同时把高低信号转化为处理器模块可以识别的高低电平信号(因为第一比较器输出的高低电平或者设备输入的高低电平不能直接输入到处理器模块被识别),经过第一光耦的导通和关闭来判断信号的输入,完成对输入信号的识别,给一个确定的信号给处理器模块进行信号的处理;处理器模块用于实现信号的处理,主要由mcu(现有技术)组成;断线检测模块用于与信号处理模块一起实现信号的识别和处理。

54.在plc应用中,数字量输入装置的信号输入接线中有源型输入接法和漏型输入接法。

55.源型输入接法是对于源型设备而言,源型设备输出的信号是低电平,此时输入到数字量输入装置的信号就是低电平,当有低电平接入后先经过信号处理模块进行信号的处理,然后再给到处理器模块进行相应的信号识别。

56.漏型输入接法是对于漏型设备而言,漏型设备输出的信号是高电平,此时输入到数字量输入装置的信号就是高电平,当有高电平接入后先经过信号处理模块进行信号的处理,然后再给到处理器模块进行相应的信号识别。

57.具体的工作过程是:数字量输入信号的额定值为24vdc,“0”信号为-30v至+5v即低电平,“1”信号为+13v至30v即高电平。

58.当接入源型设备时,输入信号din_ch0经过第一比较器进行比较处理,第一比较器的低电平门限电压为6.412v,从而实现低电平“0”信号:-30v至+5v的识别,判断信号输入为低电平,第一比较器的第一端的电压是6.412v,即图3中7脚(正向输入)的电压是6.412v,高于第二端的电压,即高于图3中的6脚(反向输入)的电压,第一比较器输出高电平,即图3中1

脚(输出端)输出高电平;第一光耦的第二端(即图3中4脚)输入高电平,第一光耦截止,第三端(即图3中13脚)输出默认的高电平。

59.同理,输入信号din_ch0经过第二比较器进行比较处理,第二比较器的门限电平为3.064v,从而实现低电平“0”信号:-30v至+5v的识别,通过电阻分压,判断信号输入为低电平,第二比较器的第二端的电压是3.064v,即图4中4脚的电压是3.064v,低于第一端的电压,即低于图4中的5脚的电压,第二比较器输出高电平,即图4中2脚输出高电平;第二光耦的第一端(即图4中1脚)输入高电平,第一光耦导通,第三端(即图4中15脚)输出高电平。

60.当接入漏型设备时,输入信号din_ch0经过第一比较器进行比较处理,第一比较器的高电平门限电压为9.097v,从而实现高电平“1”信号:+13v至30v的识别,判断信号输入是高电平,第一比较器的第一端的电压是9.097v,即图3中7脚(正向输入)的电压是9.097v,低于第二端的电压,即低于图3中的6脚(反向输入)的电压,第一比较器输出低电平,即图3中1脚(输出端)输出低电平;第一光耦的第二端(即图3中4脚)输入低电平,第一光耦导通,第三端(即图3中13脚)输出低电平。

61.同理,输入信号din_ch0经过第二比较器进行比较处理,第二比较器的门限电平为3.064v,当输入高电平“1”信号:+13v至30v时,通过电阻分压,判断信号输入为高电平,第二比较器的第二端的电压是3.064v,即图4中4脚的电压是3.064v,高于第一端的电压,即高于图4中的5脚的电压,第二比较器输出低电平,即图4中2脚输出低电平;第二光耦的第一端(即图4中1脚)输入低电平,第二光耦截止,第三端(即图4中15脚)输出默认的低电平。

62.也就是说,当处理器模块判断信号处理模块和断线检测模块同时输出高电平时,判断输入信号为源型,当判断信号处理模块和断线检测模块同时输出低电平时,判断输入信号为漏型。

63.进一步优选地,信号处理模块还包括:第一二极管;第一二极管的第一端同时与信号输入端和第一比较器的第二端相连,第二端与地相连。

64.断线检测模块还包括:第二二极管;第二二极管的第一端同时与信号输入端和第二比较器的第二端相连,第二端与地相连。

65.二极管(即:第一二极管和第二二极管)是稳压二极管,设置的主要作用是针对设备输入的高低电平保护比较器(即:第一比较器和第二比较器),保证比较器的第二端输入的电平范围为-0.7v-15v。

66.在一个实施例中,还包括:控制模块;

67.控制模块的输入端与处理器模块的输出端相连,输出端与信号处理模块的输入端相连;

68.控制模块根据处理器模块的信号控制内部光耦的状态,保证光耦一直处于打开状态,用来保证信号输入的电平门限值,从而与信号处理模块和断线检测模块一起判断断线状态。

69.优选地,控制模块包括:第三光耦;

70.第三光耦的第一端(即图5中2脚)与处理器模块相连,第二端(即图5中1脚)与电源相连,第三端(即图5中15脚)输出输入信号给信号处理模块和断线检测模块,第四端(即图5中16脚)与电源相连,需要说明,1脚和16脚共用一个电源。

71.在本实施例中,控制模块主要由第三光耦组成,通过处理器模块控制第三光耦的

开关,保证第三光耦一直处于打开状态。当断线时或外部未接设备时,控制模块给断线检测模块和信号处理模块的输入端一个固定的电平,促使断线检测模块输出高电平,信号处理模块输出低电平,也就是说,断线检测模块和信号处理模块的输出为一高一低。当有信号输入时,断线检测模块和信号处理模块输出的电平同时为高(源型设备)或者同时为低(漏型设备)。因此,控制模块与断线检测模块和信号处理模块一起判断是否断线,实现源型和漏型的断线检测功能。

72.断线检测功能在plc应用中是一个非常关键的技术,数字量输入装置带有断线检测功能可以更好地判断信号的检测。控制模块的设置使数字量输入装置不仅能实现源型和漏型接入的兼容,而且也实现了源型接入的断线检测功能和漏型接入的断线检测功能。

73.源型和漏型接入时,断线检测功能由断线检测模块、信号处理模块和控制模块同时监测判断,检测链路是否断线。

74.具体的工作过程是:

75.当接入源型或者漏型设备且断线时,由于控制模块的第三光耦是默认开启的,第三光耦输出就相当于给输入信号din_ch0(需要说明:不是控制模块的输入信号,而是输入信号,是指控制模块与断线检测模块之间的信号)加了一个39k的上拉,通过电阻的分压处理,保证信号输入有一个默认电平,这个默认电平高于第一比较器的门限电平,第一比较器输出为低电平,从而第一光耦处于开启状态,输出为低电平;同时这个默认电平低于第二比较器的门限电平,第二比较器输出高电平,从而第二光耦处于开启状态,输出为高电平。从上述分析可以看出,信号处理模块和断线检测模块输出的电平不一样,而当有设备接入时信号处理模块和断线检测模块输出的电平要么同时为高,要么同时为低,从而判断接入的源型或者漏型设备是否处于断线状态。

76.在一个具体的实施例中,第一比较器和第二比较器的型号为:lm2901xp,第一光耦、第二光耦和第三光耦的型号为:or-3h7-4,第一二极管和第二二极管的型号为:mmsz5245b。

77.需要说明,信号处理模块、断线检测模块和控制模块还包括电容电阻,相关电路为现有技术,在此不再赘述。

78.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

79.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1