一种基于电容充当浮动电压源的动态偏置低功耗积分器

1.本发明涉及模拟集成电路领域,具体涉及一种基于电容充当浮动电压源的动态偏置低功耗积分器。

背景技术:

2.近年来,物联网(iot)的发展推动了对低功耗、高分辨率模数转换器(adc)的需求。 iot应用中的大多数模数转换器由电池或能量采集器供电,因此超低功耗(ulp)的设计对于延长adc的使用寿命具有重要的意义。

3.例如delta-sigma adc在低功耗高精度音频信号数据转换、高精度窄带传感器信号数据转换、射频信号低通和带通数据转换器等领域得到了广泛应用,已成为目前最为主流的数据转换器构架之一。随着iot的发展对delta-sigma adc的功耗要求越来越高,在某些应用领域要求实现超低功耗。在delta-sigma电路中,积分器是其核心电路部分,同时也消耗了大部分的功耗,因此降低积分器的功耗对于降低整体delta-sigma adc的功耗具有重要意义。传统的运算放大器用作积分器是比较普遍的方案,然而由于其在非积分相位消耗了大量的静态功耗,不适用于超低功耗的应用场景。反相器作为积分器方案的提出,大大的降低了积分器的功耗,满足了当今对低功耗delta-sigma adc的需求。

4.现有的基于动态偏置的反相器的积分器,在积分相位和偏置相位消耗了几乎相同的平均功耗。

技术实现要素:

5.本发明的目的是提供一种基于电容充当浮动电压源的动态偏置低功耗积分器,使得积分器在偏置相位的平均功耗比起在积分相位大大降低。同时电容浮动电压源的使用,不需要额外的静态偏置电压,减少了两路静态偏置电路,从而减少了额外的偏置电路功耗。

6.为此,本发明的公开了一种基于电容充当浮动电压源的动态偏置低功耗积分器,包括:相互连接的两相非交叠时钟产生电路、反相器电路、动态偏置电路、静态偏置电路;

7.动态偏置电路包括pmos晶体管m5,nmos晶体管m6,浮动电压源ci;在clk1=1时, m5、m6的栅极和漏极短接形成二极管连接型,此时两个二极管与ci串联,m5漏极电流流过ci给其上极板充电,ci下极板电流流经m6放电;在浮动电压源ci充放电半个时钟周期后,ci上下极板形成稳定的电压差,从而给反相器电路的电容c1、c2提供偏置电压;在clk2=1时,电容ci上下极板短接,进行电荷的清零等待下一次的充放电工作;在clk2=1 时,m5、m6的栅极分别连接至avdd、vss,avdd为积分器的参考电源,vss为积分器的参考地,使得m5、m6截止,其中,输入时钟信号为clk,产生四路时钟信号,clk1和clk2 为两相非交叠信号。

8.优选地,两相非交叠时钟产生电路由与非门和非门等数字逻辑门电路构成;其中, clk1=1时clk2=0,clk1=0时clk2=1;clk1d、clk2d分别为其延时某一时间间隔的信号。

9.优选地,反相器电路包括pmos晶体管m1、m2,nmos晶体管m3、m4,偏置电容c1、 c2;其中m1作为反相器输入管其源极连接到avdd,栅极连接到c1的右极板,漏极连接到 m2的源

极;m2作为构成共源共栅结构的开关其栅极在clk1=1时连接到avdd从而截止,在clk2=1时连接到偏置电压vp,使得m2导通;m4作为反相器输入晶体管其源极连接到 vss,栅极连接到c2右极板,漏极连接到m3的源极;m3作为构成共源共栅结构开关其栅极在clk1=1时连接到vss截止,在clk2=1时连接到电压vn,使得m3导通;在clk1=1时, c1、c2的左极板连接在输入共模电压vcm,c1、c2的右极板分别连接在ci的上极板和下极板,c1、c2的右极板被动态偏置电路的浮动电压源ci偏置在某一个电压。

10.优选地,静态偏置电路包括pmos晶体管m7、m10、m11、m13、m15,nmos晶体管m8、 m9、m12、m14、m16,电阻r1;其中m13、m14、m15、m16,电阻r1构成一个对电源电压 avdd变化不敏感的电流源;m14为电流源的nmos电流镜晶体管,其栅极连接到m16的栅极,完成电流的按比例复制;m10、m11接成二极管连接型,在m16偏置的一定电流驱动下形成静态偏置电压vp;同理m7为电流源的pmos电流镜晶体管,其栅极连接到m15的栅极,完成电流的按比例复制;m8、m9接成二极管连接型,在m7偏置的一定电流驱动下形成静态偏置电压vn;电容c3、c4在clk1=1时,上下极板短接,分别连接至avdd和vss;在 clk2=1时,c3、c4上极板分别连接至vn和vp,vn和vp为静态偏置电路形成的偏置电压。

11.优选地,低功耗的积分器的工作状态在clk1=1时:积分器在clk1=1时,动态偏置电路的m5、m6连接成二极管连接型,与浮动电压源ci串联,此时电流流经m5给ci上极板充电,同时ci下极板通过m6放电;在充放电的过程中,m5的栅极电压上升,m6的栅极电压下降,一定时间后,ci形成一定的电压差,从而给反向器电路中的c1、c2提供偏置电压;此时反相器电路中的m2的栅极连接到avdd,m3的栅极连接到vss,此时,电容c3、 c4的上下极板短接,分别连接至avdd和vss,为下一次给反相器电路快速建立偏置电压提供条件。

12.优选地,所述低功耗的积分器的工作状态在clk2=1时:积分器在clk2=1时,动态偏置电路给反相器电路提供了偏置电压的条件下,反相器电路中的m1的栅极由c1的右极板电压所偏置,m4的栅极由c2的右极板电压所偏置;此时反相器的输入晶体管m1、m4具备了一定的静态工作点;此时m2的栅极由clk1=1时连接到avdd,切换到连接vp,从而m2 源漏导通,与m1晶体管构成共源共栅的放大器结构,m3的栅极由clk1=1时连接到vss,切换到连接vn,从而m3源漏导通,与m4晶体管构成共源共栅的放大器结构。

13.优选地,完整的积分器的工作过程中:在clk1=1时,采样电容cs的右极板连接到输入共模电压vcm,同时输入信号vin采样到cs的左极板,cs两端形成一定的电压差;此时动态偏置电路在clk1=1结束时,给积分器电路中的c1、c2提供偏置电压,为clk2=1 到来时积分器的积分提供静态偏置条件;此时,电容cf的左极板与c1、c2的左极板断开。 clk2=1时,采样电容cs的左极板连接到共模电压vcm,同时cs右极板断开与共模电压vcm 的连接,电容cf的左极板与c1、c2的左极板连接;此时由于cs电容两端电荷守恒,c1、 c2的右极板电压变化,反相器开始工作,从而开始对输出端vout积分,其中积分的增益为cs/cf;积分结束时,cs右端的电压回到vcm,从而完成一次积分过程。

14.本发明设计中相对于现有的动态偏置积分器,使得积分器在clk1=1时动态偏置电路的平均电流相比积分器在clk2=1时反相器电路的平均电流大大的减小;本发明设计中相对于现有的动态偏置积分器,将动态偏置电路中由pmos、nmos组成的浮动电流源替换为电容ci,由ci充当浮动电压源,这样可以减少额外的两个静态偏置电压,从而减少了两路静态偏置电路的功耗。同时,由于在ci的充放电的过程中,ci两端的压差上升,到一定程度

后m5、 m6进入亚阈值区,电流极具下降,ci的充放电开始变得缓慢,抑制了大量电流消耗,其动态偏置过程中的平均电流相对于pmos、nmos充当浮动电流源时较小。

附图说明

15.此处的附图被并入说明书中并构成本说明书的一部分,标示出了符合本发明的实施例,并与说明书一起用于解释本发明的原理。

16.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

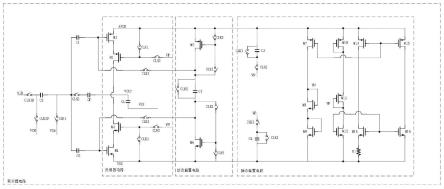

17.图1为现有积分器的电路结构示意图;

18.图2为本发明的低功耗积分器的电路结构示意图;

19.图3为本发明积分器在clk1=1时的电路连接图;

20.图4为本发明积分器在clk2=1时的电路连接图;

21.图5为本发明实例的测试电路图;

22.图6(a)为本发明积分器差分输出的电压波形图,图6(b)为现有积分器差分输出电压波形图;

23.图7(a)为本发明积分器在积分相位与动态偏置相位反相器支路与动态偏置支路电流输出波形图,图7(b)为现有积分器积分相位与动态偏置相位反相器支路与动态偏置支路电流输出波形图;

24.图8(a)为本发明积分器电路中积分相位反相器电路消耗的平均电流,图8(b)为现有积分器电路中积分相位反相器电路消耗的平均电流;

25.图9(a)为本发明积分器电路中动态偏置相位动态偏置电路的平均电流,图9(b)为现有积分器电路中动态偏置相位动态偏置电路的平均电流。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

27.需要说明,本发明实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

28.另外,在本发明中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

29.本发明的公开了一种基于电容充当浮动电压源的动态偏置低功耗积分器,主要用

于高精度低功耗delta-sigma a/d转换器等领域集成电路的数模转换部分;包括:相互连接的两相非交叠时钟产生电路、反相器电路、动态偏置电路、静态偏置电路;

30.动态偏置电路包括pmos晶体管m5,nmos晶体管m6,浮动电压源ci;在clk1=1时, m5、m6的栅极和漏极短接形成二极管连接型,此时两个二极管与ci串联,m5漏极电流流过ci给其上极板充电,ci下极板电流流经m6放电;在浮动电压源ci充放电半个时钟周期后,ci上下极板形成稳定的电压差,从而给反相器电路的电容c1、c2提供偏置电压;在clk2=1时,电容ci上下极板短接,进行电荷的清零等待下一次的充放电工作;在clk2=1 时,m5、m6的栅极分别连接至avdd、vss,avdd为积分器的参考电源,vss为积分器的参考地,这样使得m5、m6截止,其中,输入时钟信号为clk,产生四路时钟信号,clk1和clk2为两相非交叠信号。

31.本发明设计中相对于现有的动态偏置积分器,使得积分器在clk1=1时动态偏置电路的平均电流相比积分器在clk2=1时反相器电路的平均电流大大的减小;本发明设计中相对于现有的动态偏置积分器,将动态偏置电路中由pmos、nmos组成的浮动电流源替换为电容ci,由ci充当浮动电压源,这样可以减少额外的两个静态偏置电压,从而减少了两路静态偏置电路的功耗。同时,由于在ci的充放电的过程中,ci两端的压差上升,到一定程度后m5、 m6进入亚阈值区,电流极具下降,ci的充放电开始变得缓慢,抑制了大量电流消耗,其动态偏置过程中的平均电流相对于pmos、nmos充当浮动电流源时较小。

32.具体的,两相非交叠时钟产生电路由与非门和非门等数字逻辑门电路构成;其中,输入时钟信号为clk,产生四路时钟信号,clk1和clk2为两相非交叠信号,clk1=1时clk2=0, clk1=0时clk2=1。clk1d、clk2d分别为其延时某一时间间隔的信号。

33.反相器电路包括pmos晶体管m1、m2,nmos晶体管m3、m4,偏置电容c1、c2。其中m1 作为反相器输入管其源极连接到avdd,栅极连接到c1的右极板,漏极连接到m2的源极。m2 作为构成共源共栅结构的开关其栅极在clk1=1时连接到avdd从而截止,在clk2=1时连接到偏置电压vp,使得m2导通。m4作为反相器输入晶体管其源极连接到vss,栅极连接到c2右极板,漏极连接到m3的源极。m3作为构成共源共栅结构开关其栅极在clk1=1时连接到vss 截止,在clk2=1时连接到电压vn,使得m3导通。在clk1=1时,c1、c2的左极板连接在输入共模电压vcm,c1、c2的右极板分别连接在ci的上极板和下极板,c1、c2的右极板被动态偏置电路的浮动电压源ci偏置在某一个电压。

34.静态偏置电路包括pmos晶体管m7、m10、m11、m13、m15,nmos晶体管m8、m9、m12、 m14、m16,电阻r1。其中m13、m14、m15、m16,电阻r1构成一个对电源电压avdd变化不敏感的电流源。m14为电流源的nmos电流镜晶体管,其栅极连接到m16的栅极,完成电流的按比例复制。m10、m11接成二极管连接型,在m16偏置的一定电流驱动下形成静态偏置电压 vp。同理m7为电流源的pmos电流镜晶体管,其栅极连接到m15的栅极,完成电流的按比例复制。m8、m9接成二极管连接型,在m7偏置的一定电流驱动下形成静态偏置电压vn。电容 c3、c4在clk1=1时,上下极板短接,分别连接至avdd和vss。在clk2=1时,c3、c4上极板分别连接至vn和vp;vn和vp为静态偏置电路形成的偏置电压。

35.具体地,低功耗的积分器的工作状态在clk1=1时:

36.积分器在clk1=1时,其电路连接如图3所示。动态偏置电路的m5、m6连接成二极管连接型,与浮动电压源ci串联,此时电流流经m5给ci上极板充电,同时ci下极板通过m6放电。在充放电的过程中,m5的栅极电压上升,m6的栅极电压下降,一定时间后,ci形成一定的

电压差,从而给反向器电路中的c1、c2提供偏置电压。此时反相器电路中的m2的栅极连接到avdd,m3的栅极连接到vss,从而使得该支路断开,减少了静态电流的消耗。此时,电容c3、c4的上下极板短接,分别连接至avdd和vss,为下一次给反相器电路快速建立偏置电压提供条件。

37.进一步地,所述低功耗的积分器的工作状态在clk2=1时:

38.积分器在clk2=1时,其电路连接如图4所示。在clk2=1时动态偏置电路给反相器电路提供了偏置电压的条件下,反相器电路中的m1的栅极由c1的右极板电压所偏置,m4的栅极由c2的右极板电压所偏置。此时反相器的输入晶体管m1、m4具备了一定的静态工作点。此时m2的栅极由clk1=1时连接到avdd,切换到连接vp,从而m2源漏导通,与m1晶体管构成共源共栅的放大器结构,从而提高了其增益,提升了积分的精度。同样的,m3的栅极由clk1=1 时连接到vss,切换到连接vn,从而m3源漏导通,与m4晶体管构成共源共栅的放大器结构。

39.进一步地,完整的积分器的工作过程中:

40.在clk1=1时,如图3所示,采样电容cs的右极板连接到输入共模电压vcm,同时输入信号vin采样到cs的左极板,cs两端形成一定的电压差。此时动态偏置电路在clk1=1结束时,给积分器电路中的c1、c2提供偏置电压,为clk2=1到来时积分器的积分提供静态偏置条件。此时,电容cf的左极板与c1、c2的左极板断开。clk2=1时,如图4所示,采样电容cs的左极板连接到共模电压vcm,同时cs右极板断开与共模电压vcm的连接,电容cf的左极板与c1、 c2的左极板连接。此时由于cs电容两端电荷守恒,c1、c2的右极板电压变化,反相器开始工作,从而开始对输出端vout积分,其中积分的增益为cs/cf。积分结束时,cs右端的电压回到vcm,从而完成一次积分过程。

41.与现有技术相比,本发明具有以下技术特点:

42.本发明设计中相对于现有的动态偏置积分器如图1所示,使得积分器在clk1=1时动态偏置电路的平均电流相比积分器在clk2=1时反相器电路的平均电流大大的减小。

43.本发明设计中相对于现有的动态偏置积分器如图1所示,将动态偏置电路中由pmos、 nmos组成的浮动电流源替换为电容ci,由ci充当浮动电压源,这样可以减少额外的两个静态偏置电压,从而减少了两路静态偏置电路的功耗。同时,由于在ci的充放电的过程中, ci两端的压差上升,到一定程度后m5、m6进入亚阈值区,电流极具下降,ci的充放电开始变得缓慢,抑制了大量电流消耗,其动态偏置过程中的平均电流相对于pmos、nmos充当浮动电流源时较小。

44.本发明积分器在1m的采样频率,差分输入900mv,积分增益为0.4下,积分器在clk1=1 时反相器电路的平均电流为14.88ua,而动态偏置电路在clk2=1时平均电流为4.521ua,具有更低的功耗。

45.本发明使用cadence软件进行了电路设计和仿真,采用tsmc 65nm cmos工艺,积分器电路中反相器电路采用的基本mos管尺寸与现有的积分器的反相器尺寸一致,并且动态偏置电路都将反相器输入晶体管的栅极偏置电压偏置在相同的电压值。设计测试电路原理图如图5所示,电路包括两个差分输入的积分器电路和共模反馈电路。

46.本发明的主要参数设置如下:

47.电源电压avdd=3.3v,参考地vss为0v输入时钟频率(信号采样频率)为1mhz,vip

为2.1v,vin为1.2v,即差分输入900mv。采样电容cs为4pf,反馈电容cf为10pf,从而积分器的积分增益为0.4,负载电容cl为1pf,浮动电压源电容ci为1pf,共模反馈电容cm为200ff,电阻r1=25kω。

48.(1)积分器差分输出的功能仿真

49.仿真结果如图6所示,在差分输入900mv,积分增益为0.4的条件下,理论差分输出为 360mv。如图6(a)测得本发明的积分器的差分输出电压为359.615mv,如图6(b)测得现有的积分器的差分输出为359.055mv,积分器都工作正常。

50.反相器电路和动态偏置电路电流对比

51.仿真结果如图7(a)所示,本发明积分器,在clk2=1期间,反相器电路的电流在积分稳定后,有很大的静态电流(图m1878/d)。而动态偏置电路的电流(图m1879/d)在clk1=1 期间,随着时间逐渐减小至很小的电流后趋于稳定,这样使得clk1=1期间,动态偏置电路的平均电流较小。如图7(b)中所示,现有积分器,在clk2=1期间,反相器电路的电流在积分稳定后,有很大的静态电流(图m683/d)。而动态偏置电路的电流在偏置稳定后,动态偏置电路的电流趋于稳定(图m684/d),且与反相器电路支路具有接近相同的很大的静态稳定电流,这样使得clk1=1期间,动态偏置电路的平均电流较大。

52.反相器电路积分相位的平均电流

53.仿真结果如图8(a)所示,本发明积分器,由于时钟频率为1m,时钟周期为1us,如图通过cadence仿真软件计算器中的clip函数截取时钟信号clk2的某一高电平区间,本测试截取1.5us~2us的电流,通过average函数算得平均电流为14.88ua。如图8(b)所示,现有积分器同样截取钟信号clk2的某一高电平区间,截取1.5us~2us的电流,通过average函数算得平均电流为14.96ua。可见在相同的偏置条件下,本发明积分器和现有积分器的积分相位所消耗的平均电流几乎一样。

54.动态偏置电路偏置相位的平均电流

55.仿真结果如图9(a)所示,本发明积分器,由于时钟频率为1m,时钟周期为1us,如图通过cadence仿真软件计算器中的clip函数截取时钟信号clk1的某一高电平区间,本测试截取2us~2.5us的电流,通过average函数算得平均电流为4.521ua,对比本发明积分器的积分相位的平均电流14.88ua减少了大约70%的电流。如图9(b)所示,现有积分器同样截取钟信号clk1的某一高电平区间,截取2us~2.5us的电流,通过average函数算得平均电流为 12.99ua,相对于积分相位的14.96ua,几乎拥有相同的平均电流。可见在相同的偏置条件下,本发明积分器在动态偏置相位所消耗的平均电流具有大幅度的降低,同时电容浮动电压源的使用,也减少了两路静态偏置电路的功耗。

56.以上所述仅是本发明的具体实施方式,使本领域技术人员能够理解或实现本发明。对这些实施例的多种修改对本领域的技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所申请的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1