一种多路心肺音数据采集电路

1.本实用新型涉及信号采集电路技术领域,尤其涉及一种多路心肺音数据采集电路。

背景技术:

2.听诊器是呼吸系统疾病常用的辅助诊断设备,操作简单且安全,传统听诊设备为入耳式耳塞听诊器,需患者找专业医师进行听诊,患者行动不便或因政策无法出行时将无法进行听诊,听诊时主观和客观因素都会影响听诊的诊断结果。现有电子听诊器可以实现患者自主操作进行听诊,后由算法给出诊断结果。电子听诊器,听诊结果受操作和环境影响较大,实际听诊时,患者需要在身体不同部位进行听诊,多次测量才能得出结果,操作难度大,患者常无法正确使用,导致分辨率低无法得出正确的诊断结果。且现有电子听诊器多为单通道听诊器,无法做到多部位同时听诊或多人同时听诊,使用时局限性较大。因此亟需一种具有多路心肺音数据采集的电路。

技术实现要素:

3.本实用新型要解决的技术问题在于针对现有技术中的缺陷,提供一种多路心肺音数据采集电路,该多路心肺音采集电路基础为8通道数据采集,每8通道为一组,组成扩展模块电路,最多可扩展至32通道。采集的数据存储于sd卡中,可通过以太网接口或wifi连接网络实现sd卡中心肺音数据的上传。

4.本实用新型解决其技术问题所采用的技术方案是:

5.本实用新型提供一种多路心肺音数据采集电路,心肺音数据采集电路一端与待采集的心肺音信号相连,另一端与pc上位机相连;心肺音数据采集电路包括:前端采集电路、adc模数转换电路、主控电路、sd卡存储电路、以太网接口电路、wifi接口电路、oled显示电路、电源管理电力;其中:

6.前端采集电路的输入端连接待采集的心肺音信号,输出端与adc模数转换电路的输入端相连,adc模数转换电路的输出端与主控电路的输入端相连;主控电路的一路输出端与oled显示电路相连,另一路输出端依次与sd卡存储电路、以太网接口电路、wifi接口电路串联;电源管理电力分别与adc模数转换电路、主控电路、sd卡存储电路、以太网接口电路、wifi接口电路、oled显示电路均相连,并为它们供电;心肺音数据采集电路通过wifi接口电路与pc上位机无线连接。

7.进一步地,本实用新型的主控电路包括:主控芯片u3,电阻r1、电阻r2、电阻r12、电阻r13、电阻r4、电阻r7,电容c1、电容c2、电容c3、电容c4、电容c6、电容c7、电容c8、电容c9、电容c10、电容c11、电容c12、电容c13,晶振x1、晶振x3,按钮sw1;其中:

8.电阻r4、电容c6、按钮sw1组成复位电路与主控芯片u3的14脚相连,晶振x3、电容c3、电容c4组成晶体振荡电路与主控芯片u3的12、13脚相连,晶振x1、电容c1、电容c2组成晶体振荡电路与主控芯片u3的8、9脚相连;主控芯片u3的6、11、19、21、22、28、50、75、100引脚

接3.3v电源,且电阻r7、电容c7、电容c8组成滤波电路接入主控芯片u3的21脚,主控芯片u3的10、20、27、49、74、99引脚接地;电阻r1、电阻r2通过跳线帽与主控芯片u3的boot0模式选择引脚相连,电阻r12、电阻r13通过跳线帽与主控芯片u3的boot1模式选择引脚相连,电阻r1为boot0模式选择的上拉电阻,电阻r2为boot0模式选择的下拉电阻,电阻r12为boot1模式选择的上拉电阻,电阻r13为boot1模式选择的下拉电阻;电容c9、电容c10、电容c11、电容c12、电容c13连接主控芯片u3的vdd引脚,为滤波电容。

9.进一步地,本实用新型的adc模数转换电路包括adc芯片u5,电阻r18、电阻r19、电阻r20,电容c29、电容c30、电容c31,输入端口h6;其中:

10.adc芯片u5的1、37、38、48引脚接+5v电源供电,3、4、5引脚分别为os0、os1、os2,分别与主控芯片u3的43、44、45引脚相连接,6脚通过电阻r20接地,7脚通过电阻r19接3.3v电源,8脚和主控芯片u3的46脚相连,9、10引脚短接后与主控芯片u3的36脚相连接;11脚为u5复位引脚,与主控芯片u3的77脚相连,12、13、14引脚分别与主控芯片u3的18、70、71引脚相连,16~22和24~33引脚为adc芯片u5的数据输出引脚,转换后的量化数据从这些端口输出,按顺序与主控芯片u3的81~88和55~62引脚相连,adc芯片u5的49、51、53、55、57、59、61、63为8路采样输入端口与输入端口h6依次连接,42脚接电源管理vref_2.5v,36、39、44和45引脚通过电容c30、电容c31、电容c29接地。

11.进一步地,本实用新型的以太网接口电路包括:phy芯片u10,以太网口j1,晶振x4,电阻r5、电阻r6、电阻r8、电阻r9、电阻r10、电阻r11、电阻r22、电阻r23、电阻r24、电阻r25、电阻r26、电阻r27、电阻r28,电容c5、电容c14、电容c15、电容c16、电容c17、电容c18、电容c19、电容c20、电容c35、电容c36、电容c37、电容c42、电容c43、电容c44、电容c45、电容c46;其中:

12.晶振x4、电容c19、电容c20、电阻r27组成晶体振荡电路,晶振x4两端接phy芯片u10的30、31引脚,并为phy芯片u10提供工作所需外部时钟;phy芯片u10的1、2、5、6引脚为u10数据输入输出总线,分别通过电阻r8至电阻r11与以太网口j1的2、1引脚、电容c18、电容c35的一端连接,电容c18和电容c35的另一端接以太网口j1的6、3引脚,以太网口j1的5引脚接电容c36一端,电容c36另一端接地,6引脚通过电容c18、电阻r22、电容c36接地,3引脚通过电容c35、电阻r23、电容c36接地,1、2、4引脚通过电阻r24、电阻r25、电阻r28接3.3v电源,其中4引脚还通过电容c37接地,9、12引脚通过电阻r5、电阻r6接3.3v供电,10、11引脚与phy芯片u10的25、27引脚相连;phy芯片u10的vadd引脚接3.3v供电,agnd引脚接gnd,28、29引脚接3.3v、gnd,电容c16、电容c17,为28引脚供电滤波电容,phy芯片u10的32、33、34、35、36、37、43、44、45引脚分别接主控芯片u3的35、52、53、54、34、35、32、31、30引脚连接,10引脚通过电阻r26接地,20、22引脚通过电容c14、电容c15接地。

13.进一步地,本实用新型的sd卡存储电路包括:sd卡卡座tf-01a,电阻r14;其中:

14.sd卡卡座tf-01a的6、10、11、12、13引脚接地,4引脚接3.3v供电,2、3、5、7引脚分别接主控芯片u3的97、90、89、91引脚,2引脚接电阻r14后接3.3v上拉。

15.进一步地,本实用新型的wifi接口电路包括:wifi模块u7,晶振x2,电阻r29、电阻r30、电阻r31、电容c39、电容c40、电容c41、按钮sw2、按钮sw3、程序烧写端口esp_usart0;其中:

16.电阻r30、电容c41、按钮sw2组成wifi复位电路,与wifi模块u7的3引脚连接,晶振

x2、电阻r29、电容c39、电容c40组成晶体振荡电路连接wifi模块u7的9、10引脚,电阻r31、按钮sw3组成工作模式设置电路连接wifi模块u7的25引脚;wifi模块u7的1、15、38、39引脚接地,2引脚接wifi供电端3.3v,27、28引脚接主控芯片u3的68、69引脚;程序烧写端口esp_usart0接口的1、2引脚接wifi模块u7的35、34引脚,3引脚接地。

17.进一步地,本实用新型的oled显示电路包括:oled显示屏接口h7;其中:h7的1、2引脚接主控芯片u3的3、4引脚,3脚接3.3v供电,4脚接地。

18.进一步地,本实用新型的电源管理电路包括:dc-dc芯片u2,电源输入端口dc1、3.3v稳压芯片u1、3.3v稳压芯片u4、2.5v稳压芯片u6、电阻r15、电阻r16、电阻r17、电阻r21、电容c21、电容c22、电容c23、电容c24、电容c25、电容c26、电容c27、电容c28、电容c33、电容c34、电感u6-10uh、二极管d1;其中:

19.dc-dc芯片u2的1、3引脚通过电容c27相互连接,2引脚接电源输入端口dc1的1引脚,4引脚接地,5引脚接电阻r16和电阻r17,电阻r17另一端输出+5v,6引脚接电容c25、电阻r15然后接地,7引脚通过电阻r21接电源输入端口dc1的1引脚,8引脚接电容c26后接地;二极管d1正向端接地,反向端接dc-dc芯片u2的3引脚,电感u6-10uh一端接dc-dc芯片u2的3引脚另一端接+5v输出;电源输入端口dc1的2、3引脚接地,1引脚为总的电源输入,电容c28接电源输入端口dc1的1引脚;3.3v稳压芯片u1的3引脚接+5v电源,2、4相连引脚输出3.3v电源,1引脚接地,电容c24、电容c23接3.3v稳压芯片u1的2引脚消除纹波稳定3.3v输出电压;2.5v稳压芯片u6的1引脚接地,2、4引脚相连输出2.5v电源,3引脚接+5v电源,电容c33、电容c34接vref_2.5v;3.3v稳压芯片u4的1引脚接地,电容c32、电容c38接u4的2引脚稳定输出3.3v单独为wifi供电;2.5v稳压芯片u6的1引脚接地,2、4引脚相连输出2.5v电源,3引脚接+5v电源,电容c33、电容c34为输出滤波电容接vref_2.5v稳定输出电压。

20.进一步地,本实用新型的前端采集电路(其中一路)包括:驻极体mic1接口,功放芯片u8,电阻r32、电阻r33、电阻r34、滑动变阻器rp1、电容c47,电容c48、电容c49;其中:

21.r32一端接3.3v,另外一端接mic1的2引脚,r33一端接mic1的1引脚另外一端接地;电容c47一端接mic1的2引脚另外一端接功放芯片u8的3引脚;滑动变阻器和c49相连,接入u8的1引脚和8引脚之间,通过调整滑动变阻器可以调节u8的增益倍数,u8的2、4、7引脚接地,6引脚接+5v供电,5引脚接电容c48,c48为耦合输出电容,r34一端接+5v,另一端接c48,为输出信号提供相应的静态工作电压,信号输出端口为dataout1。

22.本实用新型产生的有益效果是:本实用新型的多路心肺音数据采集电路,电路结构可扩展,至多可扩展32通道的数据采集,采集器自动采集输入数据,并存储于本地sd卡中,方便后续数据的进一步处理,通过连接网络可实现远程多通道数据采集,极大的简化了心肺音信号采集过程中数据存储和上传工作,灵活度高,使用方便,实时性好,给心肺音数据采集的研究提供了一种高效的数据收集方案。

附图说明

23.下面将结合附图及实施例对本实用新型作进一步说明,附图中:

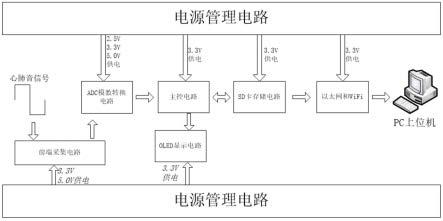

24.图1是本实用新型实施例的整体电路示意图;

25.图2是本实用新型实前端采集电路的其中一路;

26.图3是本实用新型实施例的主控电路图;

27.图4是本实用新型实施例的adc模数转换电路;

28.图5是本实用新型实施例的phy芯片电路图;

29.图6是本实用新型实施例的以太网接口电路图;

30.图7是本实用新型实施例的sd卡接口电路图;

31.图8是本实用新型实施例的wifi接口电路图;

32.图9是本实用新型实施例的oled接口电路图;

33.图10是本实用新型实施例的电源管理电路;

具体实施方式

34.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本实用新型,并不用于限定本实用新型。

35.如图1所示,本实用新型实施例的多路心肺音数据采集电路,采集电路一端为信号输入端口,连接由模拟采集电路调整后输出的心肺音信号,数据存储于sd卡中,待采集结束,通过网络接口上传至pc机或手机端便于做进一步数据处理。该采集电路方案包括:前端采集电路、adc模数转换电路、mcu主控电路、电源管理电路、oled显示电路、以太网接口电路、wifi接口电路、sd卡存储电路;前端采集电路采集原始心肺音信号转换为

±

10v范围的模拟信号,adc模数转换输入端口输入信号为

±

10v范围的模拟信号,前端采集电路输出与adc模数转换电路相连,adc模数转换电路输出接口与主控电路相连,量化后的数据经主控制器处理通过与之相连接的sd卡存储电路存储于sd卡中,采集完成后,由主控制器将sd卡中的音频数据通过与主控电路连接的以太网接口电路或wifi接口模块发送至pc端或手机端,oled显示电路与主控电路相连,用以显示当前采集器工作状态,电源管理电路与主控电路,oled显示电路、sd卡存储电路、以太网接口电路、wifi接口电路,adc模数转换电路相连接,为其提供稳定工作电源。

36.如图2所示,前端采集电路由相同电路组成每8路为一组,至多扩展32路,其中一路电路包括:驻极体mic1接口,功放芯片u8,电阻r32、电阻r33、电阻r34、滑动变阻器rp1、电容c47,电容c48、电容c49;其中:

37.r32一端接3.3v,另外一端接mic1的2引脚,r33一端接mic1的1引脚另外一端接地;电容c47一端接mic1的2引脚另外一端接功放芯片u8的3引脚;滑动变阻器和c49相连,接入u8的1引脚和8引脚之间,通过调整滑动变阻器可以调节u8的增益倍数,u8的2、4、7引脚接地,6引脚接+5v供电,5引脚接电容c48,c48为耦合输出电容,r34一端接+5v,另一端接c48,为输出信号提供相应的静态工作电压,信号输出端口为dataout1。

38.在本施例中,采用lm386功放芯片作为主要的声音信号采集电路,通过驻极体拾音传感器采集声音心肺音信号,经过lm386功放芯片输出放大后的心肺音模拟信号,电容c48为输出耦合电容,通过r34上拉电阻上拉至5v静态电位,这是因为后续adc输入为

±

10v,但为了方便数据整理,将静态点设置为+5v,让心肺音信号在0~+10v范围变化。在lm386的1和8引脚间接入滑阻rp1,用来调整lm386的增益倍数(20-200倍)。

39.如图3所示,主控电路包括:主控芯片u3,电阻r1、电阻r2、电阻r12、电阻r13、电阻r4、电阻r7,电容c1、电容c2、电容c3、电容c4、电容c6、电容c7、电容c8、电容c9、电容c10、电

容c11、电容c12、电容c13,晶振x1、晶振x3,按钮sw1;其中:

40.电阻r4、电容c6、按钮sw1组成复位电路与主控芯片u3的14脚相连,晶振x3、电容c3、电容c4组成晶体振荡电路与主控芯片u3的12、13脚相连,晶振x1、电容c1、电容c2组成晶体振荡电路与主控芯片u3的8、9脚相连;主控芯片u3的6、11、19、21、22、28、50、75、100引脚接3.3v电源,且电阻r7、电容c7、电容c8组成滤波电路接入主控芯片u3的21脚,主控芯片u3的10、20、27、49、74、99引脚接地。电阻r1、电阻r2通过跳线帽与主控芯片u3的boot0模式选择引脚相连,电阻r12、电阻r13通过跳线帽与主控芯片u3的boot1模式选择引脚相连,电阻r1为boot0模式选择的上拉电阻,电阻r2为boot0模式选择的下拉电阻,电阻r12为boot1模式选择的上拉电阻,电阻r13为boot1模式选择的下拉电阻;电容c9、电容c10、电容c11、电容c12、电容c13连接主控芯片u3的vdd引脚,为滤波电容。

41.在本施例中,主控芯片采用stm32f107vc,最小系统电路采用用25m的外部晶振作为芯片的工作时钟输入,使用pd组的io口作为与ad芯片数据传输总线,boot引脚引出,通过跳线帽选择芯片的启动模式。采集的数据由主控保存至sd卡中,后续通过网络进行上传。

42.如图4所示,adc模数转换电路包括adc芯片u5,电阻r18、r19、r20,电容c29、c30、c31,输入端口h6,其中u5的1、37、38、48引脚接+5v电源供电,3、4、5引脚分别为os0、os1、os2、其与主控芯片u3的43,44,45引脚相连接,通过调整三个引脚的电平状态控制模数转换芯片u5的过采样倍数,6脚通过r20接地,7脚通过r19接3.3v电源,8脚和u3的46脚相连,通过控制该引脚电平设置u5的采样输入电压范围,9、10引脚短接后与u3的36脚相连接,u5通过9,10引脚输入一定频率的方波来启动转换模拟电信号,11脚为u5复位引脚,与u3的77脚相连,12,13,14引脚分别与u3的18,70,71引脚相连,16~22和24~33引脚为u5的数据输出引脚,转换后的量化数据从这些端口输出,按顺序与u3的81~88和55~62引脚相连,u5的49、51、53、55、57、59、61、63为8路采样输入端口与h6依次连接,42脚接电源管理vref_2.5v,36、39、44和45引脚通过c30、c31、c29接地。

43.在本施例中,选择adc芯片型号为ad7606,通过主控设置其range引脚的电平来设置其输入电压的范围,基准电压为2.5v,由2.5v稳压电路提供,ad7606的供电电压为+5v,需要在vdrive引脚提供一个+3.3v电压,来匹配主控的信号逻辑,os0~os2为ad7606过采样倍数配置引脚,与主控芯片连接,可通过软件配置其过采样倍数。

44.如图5、6所示,以太网接口电路包括:phy芯片u10,以太网口j1,晶振x4,电阻r5,电阻r6,电阻r8,电阻r9,电阻r10,电阻r11,电阻r22,电阻r23,电阻r24,电阻r25,电阻r26,电阻r27,电阻r28,电容c5、电容c14,电容c15,电容c16,电容c17,电容c18,电容c19,电容c20,电容c35,电容c36,电容c37,电容c42,电容c43,电容c44,电容c45,电容c46;其中:

45.晶振x4,电容c19,电容c20,电阻r27组成晶体振荡电路,晶振x4两端接u10的30,31引脚为u10提供工作所需外部时钟,u10的1、2、5、6引脚为u10数据输入输出总线,分别通过电阻r8至电阻r11与j1的2、1引脚,电容c18、电容c35的一端连接,电容c18和c35的另一端接j1的6、3引脚。j1的5引脚接c36一端,c36另一端接地,6引脚通过c18、r22、c36接地,3引脚通过c35、r23、c36接地,1、2、4引脚通过r24、r25、r28接3.3v电源,其中4引脚还通过c37接地,9、12引脚通过r5、r6接3.3v供电,10、11引脚与u10的25、27引脚相连;u10的vadd引脚接3.3v供电,agnd引脚接gnd,28、29引脚接3.3v、gnd,电容c16、电容c17,为28引脚供电滤波电容,u10的32、33、34、35、36、37、43、44、45引脚分别接主控制器u3的35、52、53、54、34、35、32、31、

30引脚连接,10引脚通过r26接地,20、22引脚通过电容c14、电容c15接地。

46.在本施例中,phy芯片的型号为w5500,其内布集成了32kb的缓存用以处理以太网数据包,通过spi(串行外围接口)便于与外部单片机集成。w5500的spi支持80mhz的速度和新的高效spi协议,用于高速网络通信。采用外部25mhz晶振为其提供稳定的外部时钟输入,保证传输的稳定性,mode0~mode2为w5500传输模式设置引脚,这些引脚与主控芯片相连,通过软件可以设置w5500的传输模式。以太网接口采用hy911105ae自带变压器的便准网络接口,变压器抽头通过电容c36、c37接地,这样可以稳定抽头的点位,纹波通过电容接地直接消除,减小抽头电位波动造成的传输失败的可能。

47.如图7所示,sd卡存储电路包括:sd卡卡座tf-01a,电阻r14;其中:

48.tf-01a的6、10、11、12、13引脚接地,4引脚接3.3v供电,2、3、5、7引脚分别接u3的97、90、89、91引脚,2引脚接上拉电阻r14接3.3v上拉。

49.在本施例中,主控通过spi总线与sd卡进行数据交互,stm32f107vc的spi一共有三组,最高的传输速度为18mb/s,采集的心肺音数据以wav格式保存在sd卡中,以便后续处理。

50.如图8所示,wifi接口电路包括:wifi模块u7,晶振x2电阻r29、电阻r30、电阻r31、电容c39、电容c40、电容c41、按钮sw2、按钮sw3、程序烧写端口esp_usart0;其中:

51.电阻r30、电容c41、按钮sw2组成wifi复位电路,与u7的3引脚连接,晶振x2、电阻r29、电容c39、电容c40组成晶体振荡电路连接u7的9、10引脚,电阻r31、按钮sw3组成工作模式设置电路连接u7的25引脚。u7的1、15、38、39引脚接地,2引脚接wifi准用供电端3.3v_wifi,27、28引脚接u3的68、69引脚。程序烧写端口esp_usart0接口的1、2引脚接u7的35、34引脚,3引脚接地。

52.在本施例中,wifi选用乐鑫公司芯片模组esp32-wroom-32e 16m flash版,通过编程可以设置esp32工作为wifi的ap&station模式,采用串口进行esp32的程序,在烧写程序时需要拉低io0让其进入烧写模式,在本施例中,通过1k下拉电阻r31和按钮开关sw3来实现这一功能。进入烧写模式后通过esp32的uart0进行程序的烧写。主控芯片通过串口将存储于sd卡中的音频数据发送给esp32,esp32接收数据后通过网络转发至上位机方便后续的数据处理,实现无线网络传输功能。

53.如图9所示,oled显示电路包括:oled显示屏接口h7;其中:h7的1、2引脚接u3的3、4引脚,3脚接3.3v供电,4脚接地。

54.本施例中采用iic总线驱动的oled显示屏,用来显示系统的工作状态。因主控stm32f107vc的io自带上拉电阻,采用模拟iic控制oled,所以无需在iic总线上接额外的上拉电阻。

55.如图10所示,电源管理电路包括:dc-dc芯片u2,电源输入端口dc1、3.3v稳压芯片u1、3.3v稳压芯片u4、2.5v稳压芯片u6、电阻r15、电阻r16、电阻r17、电阻r21、电容c21、电容c22、电容c23、电容c24、电容c25、电容c26、电容c27、电容c28、电容c33、电容c34、电感u6-10uh、二极管d1;其中:

56.u2的1、3引脚通过电容c27相互连接,2引脚接dc1的1引脚,4引脚接地,5引脚接电阻r16和r17,r17另一端输出+5v,6引脚接电容c25、电阻r15然后接地,7引脚通过电阻r21接dc1的1引脚,8引脚接c26后接地。二极管d1正向端接地反向端接u2的3引脚,电感u6-10uh一端接u2的3引脚另一端接+5v输出。dc1的2、3引脚接地,1引脚为总的电源输入,电容c28接

dc1的1引脚。u1的3引脚接+5v电源,2、4相连引脚输出3.3v电源,1引脚接地,电容c24、电容c23接u1的2引脚消除纹波稳定3.3v输出电压。u6的1引脚接地,2、4引脚相连输出2.5v电源,3引脚接+5v电源,电容c33、电容c34接vref_2.5v。

57.本施例中,采用同步整流buck调节芯片mp1484en作为主要的供电电路,将输入8~24v的电压转换为+5v供电,输出电压计算公式为24v的电压转换为+5v供电,输出电压计算公式为电阻r17阻值为46k,电阻r16阻值为10k,计算得出v

out

=5.04v。其余各部分供电由ams1117-3.3v和ams1117-2.5v芯片通过+5v转3.3v、2.5v提供。

58.应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本实用新型所附权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1