多通道无人机侦控系统的制作方法

1.本实用新型涉及通讯侦控技术领域,尤其涉及一种多通道无人机侦控系统。

背景技术:

2.目前,在电磁干扰设备中,采用现有的侦控设备无法实现多通道实时同步采集侦控,无法实现多通道实时同步效果,无法满足实时接收统一频点,无法达到多时钟同步及全向接收发射,因此给实际应用中带来了极大的困难。

技术实现要素:

3.针对上述的缺陷,本实用新型的目的在于提供一种多通道无人机侦控系统,由多路时钟同步电路使用相位延迟及低抖动技术,产生的相位同步时钟触发数据采集系统和控制系统,通过高速传输通道及接口系统互联,实现多通道的实时同步侦控系统。控制系统通过fmc连接器与接口系统互联,结构层次化,各个系统互相紧密结合;投入使用后已经解决多通道实时同步问题,满足了广大的市场应用需求。

4.为了实现上述目的,本实用新型提供一种多通道无人机侦控系统,包括数据采集系统、控制系统、接口系统和多路时钟同步电路;

5.数据采集系统通过fmc连接器与控制系统电连接,接口系统也通过fmc连接器与控制系统电连接;

6.数据采集系统设置有两个,数据采集系统用于对射频信号进行采集并进行模数转换;

7.多路时钟同步电路采用相位延迟和低抖动技术,产生多通道相位同步时钟信号,多通道相位同步时钟信号触发数据采集系统和控制系统,实现数据在高速通道中实时同步传输至控制系统;

8.接口系统用于对控制系统下发控制指令,实现控制系统对高速通道中的采集数据进行分析和计算,以及对所接收的射频信号进行检测侦察。

9.作为优选的技术方案,包括3个时钟模块,分别为时钟模块a、时钟模块b和时钟模块c,时钟模块a通过sma接口接收射频信号,其中,sma接口与时钟模块a之间连接有两个晶振模块。

10.作为优选的技术方案,时钟模块a发出两个参考时钟信号和两个同步时钟信号,一个参考时钟信号和一个同步时钟信号为一组,连接一个数据采集系统的数据干扰子系统,用于数据干扰子系统进行数据采集并对采集的数据进行模数转换;另一组参考时钟信号和同步时钟信号连接同一个数据采集系统的另一数据干扰子系统。

11.作为优选的技术方案,时钟模块a还通过gth参考时钟信号分别触发控制系统3的收发器gth228模块和收发器gth229模块;

12.时钟模块a还通过fpga同步时钟信号a触发hp66模块;

13.时钟模块a还通过fpga同步时钟信号b触发hp67模块。

14.作为优选的技术方案,时钟模块c通过另一sma接口接收射频信号,其中,另一sma接口与时钟模块c之间连接有两个晶振模块。

15.作为优选的技术方案,时钟模块c发出两个参考时钟信号和两个同步时钟信号,一个参考时钟信号和一个同步时钟信号为一组,连接另一个数据采集系统的数据干扰子系统,用于数据干扰子系统进行数据采集并对采集的数据进行模数转换;另一组参考时钟信号和同步时钟信号连接同一个数据采集系统的另一数据干扰子系统。

16.作为优选的技术方案,时钟模块c还通过gth参考时钟信号分别触发控制系统3的收发器gth128模块和收发器gth129模块;

17.时钟模块c还通过fpga同步时钟信号c触发hd48模块;

18.时钟模块c还通过fpga同步时钟信号d触发hd44模块。

19.作为优选的技术方案,时钟模块b通过又一sma接口接收射频信号,其中,另一sma接口与时钟模块c之间连接有两个晶振模块,时钟模块b分别连接时钟模块a和时钟模块c。

20.作为优选的技术方案,所述多通道无人机侦测系统能够实时同步测控干扰和数据采集传输信号的频率范围为27mhz~6ghz。

21.作为优选的技术方案,所述多通道无人机侦测系统最多能够支持八通道实现同步收发功能。

22.本实用新型提供一种多通道无人机侦控系统,由多路时钟同步电路结合设计而成,使用相位延迟及低抖动技术,产生的相位同步时钟触发数据采集系统和控制系统,通过高速传输通道及接口系统互联,实现多通道的实时同步侦控系统。控制系统通过fmc连接器与接口系统互联,结构层次化,各个系统互相紧密结合;投入使用后已经解决多通道实时同步问题,满足了广大的市场应用需求。

附图说明

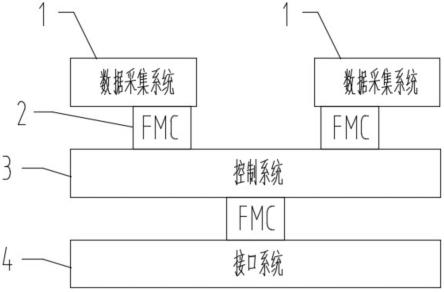

23.图1是本实用新型多通道无人机侦控系统的物理结构图;

24.图2是本实用新型多通道无人机侦控系统的结构框图;

25.图3是多路时钟同步电路框图;

26.图4是时钟模块a的部分电路图;

27.图5是时钟模块a的另一部分电路图;

28.图6为时钟模块a的又一部分电路图;

29.图7是时钟模块b的部分电路图;

30.图8是时钟模块b的另一部分电路图;

31.图9为时钟模块b的又一部分电路图;

32.图10是时钟模块c的部分电路图;

33.图11是时钟模块c的另一部分电路图;

34.图12为时钟模块c的又一部分电路图;

35.图13是fpga主控模块中芯片u17的电路连接图;

36.图14是fpga主控模块中芯片u87的部分电路连接图;

37.图15是fpga主控模块中芯片u86的部分电路连接图;

38.图16是fpga主控模块中芯片u86的另一部分电路连接图;

39.图17是fpga主控模块中芯片u87的另一部分电路连接图;

40.图18是fmc2e座子的电路连接图;

41.图19是fmc3e座子的电路连接图。

42.图中:

43.1-数据采集系统,2-fmc连接器,3-控制系统,4-接口系统。

具体实施方式

44.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

45.如图1、图2所示,本实用新型提供一种多通道无人机侦控系统,包括数据采集系统1、控制系统3、接口系统4和多路时钟同步电路。

46.数据采集系统1通过fmc连接器2与控制系统3电连接,接口系统也通过fmc连接器2与控制系统电连接。

47.数据采集系统1设置有两个。数据采集系统1用于对射频信号进行采集并进行模数转换。

48.多路时钟同步电路采用相位延迟和低抖动技术,产生多通道相位同步时钟信号,多通道相位同步时钟信号触发数据采集系统1和控制系统3,实现数据在高速通道中实时同步传输至控制系统3。

49.接口系统4用于对控制系统3下发控制指令,实现控制系统3对高速通道中的采集数据进行分析和计算,以及对所接收的射频信号进行检测侦察。

50.所述多通道无人机侦测系统能够实时同步测控干扰和数据采集传输信号的频率范围为27mhz~6ghz。

51.所述多通道无人机侦测系统最多能够支持八通道实现同步收发功能。

52.具体的,如图3所示,包括3个时钟模块,分别为时钟模块a、时钟模块b和时钟模块c,时钟模块a通过sma接口接收射频信号,其中,sma接口与时钟模块a之间连接有两个晶振模块。

53.时钟模块a发出两个参考时钟信号和两个同步时钟信号,一个参考时钟信号和一个同步时钟信号为一组,连接一个数据采集系统1的数据干扰子系统,用于数据干扰子系统进行数据采集并对采集的数据进行模数转换;另一组参考时钟信号和同步时钟信号连接同一个数据采集系统1的另一数据干扰子系统。

54.时钟模块a还通过gth参考时钟信号分别触发控制系统3的收发器gth228模块和收发器gth229模块;

55.时钟模块a还通过fpga同步时钟信号a触发hp66模块,hp66模块是fpga内部的第66个集合了多个可编程输入输出单元的bank,具有高性能,支持高速率信号和时钟;

56.时钟模块a还通过fpga同步时钟信号b触发hp67模块,hp66模块是fpga内部的第67个集合了多个可编程输入输出单元的bank,具有高性能,支持高速率信号和时钟。

57.时钟模块c通过另一sma接口接收射频信号,其中,另一sma接口与时钟模块c之间连接有两个晶振模块。

58.时钟模块c发出两个参考时钟信号和两个同步时钟信号,一个参考时钟信号和一个同步时钟信号为一组,连接另一个数据采集系统1的数据干扰子系统,用于数据干扰子系统进行数据采集并对采集的数据进行模数转换;另一组参考时钟信号和同步时钟信号连接同一个数据采集系统1的另一数据干扰子系统。

59.时钟模块c还通过gth参考时钟信号分别触发控制系统3的收发器gth128模块和收发器gth129模块;

60.时钟模块c还通过fpga同步时钟信号c触发hd48模块,hd48模块是fpga内部的第48个集合了多个可编程输入输出单元的bank,具有高密度的输入输出单元,支持偏低速率信号和时钟;

61.时钟模块c还通过fpga同步时钟信号d触发hd44模块,hd48模块是fpga内部的第48个集合了多个可编程输入输出单元的bank,具有高密度的输入输出单元,支持偏低速率信号和时钟。

62.时钟模块b通过又一sma接口接收射频信号,其中,又一sma接口与时钟模块b之间连接有两个晶振模块。时钟模块b分别连接时钟模块a和时钟模块c。

63.fpga同步时钟信号a、fpga同步时钟信号b、fpga同步时钟信号c由fpga主控模块控制,fpga主控模块包括芯片u17、u87、u86,参见图13至图17。

64.图4中,时钟电路b由两个晶振提供参考时钟和本振时钟触发时钟芯片,产生两个同步时钟同时去触发时钟电路a和时钟电路c,时钟电路b和时钟电路c产生的同步时钟触发fpga的gtx和相应bank,从而实现了时钟同源,时钟相位同步,从而达到多通道侦控。

65.时钟模块a包括芯片u13、芯片u7、芯片u9和芯片u74,参见图4至图6;时钟模块b包括芯片u76、芯片u77、芯片u78、芯片u79、芯片u80,参见图7至图9;时钟模块c包括芯片u81、芯片u82、芯片u83、芯片u84、芯片u85,参见图10至图12。

66.芯片u13的36脚经电容c112连接芯片u7的1脚,芯片u13的37脚经电容c113连接芯片u7的3脚,芯片u7的4脚经电阻r22接地,芯片u7的5脚经电容c111连接芯片u8的1脚,芯片u8的2脚至5脚均接地。

67.芯片u13的33脚经电阻r24连接芯片u9的3脚,芯片u9的2脚分别连接电容c134的一端、电感l33的一端、电容c130的一端、电容c129的一端,电容c134的另一端连接芯片u13的34脚,电感l33的另一端接地,电容c130的另一端分别连接芯片u9的4脚、电阻r257的另一端、电容c129的另一端、电感l32的一端,电阻r257的另一端连接芯片u9的1脚,电感l32的另一端连接电源。

68.芯片u13的47脚分别连接电阻r741的一端、电容c757的一端,电阻r741的另一端经电阻r743接地,电阻r741的另一端经电阻r742连接芯片u13的48脚,芯片13的48脚还经电容c153连接芯片u74的4脚,电容c757的另一端连接芯片u74的5脚;芯片u74的1脚经电阻r749连接芯片u17,芯片u74的3脚经并联的电容c158、电容c159、电容c142、电容c143、电容c141连接电源,芯片u74的3脚还接地;芯片u74的2脚经电阻r740连接电源,芯片u74的6脚连接电源。

69.芯片u13的7脚经电容c168接地;芯片u13的8脚经电容c169接地;芯片u13的9脚经电容c170接地;芯片u13的10脚连接电源d-vcc1-vco;芯片u13的11脚分别连接电容c171的一端、电容c166的一端,电容c171的另一端接地,电容c166的另一端连接芯片u13的12脚;芯

片u13的15脚经电容c146连接连接芯片u76的36脚,芯片u13的15脚经电容c151连接芯片u76的37脚;芯片u13的17脚连接电源d-vcc2-out;芯片u13的18脚分别连接电阻r34的一端、电阻r40的一端,电阻r34的另一端接1.8v电源;电阻r40的另一端连接芯片u17的b16脚;芯片u13的19脚经电阻r39连接芯片u76的19脚;芯片u13的20脚经电阻r36连接芯片u76的20脚;芯片u13的46脚经电容c172接地;芯片u13的49脚经电容c173接地;芯片u13的31脚经电阻r41连接芯片u17的a12脚;芯片u13的52脚经电阻r43连接芯片u17的e14脚;芯片u13的62脚经电阻r45连接芯片u17的f15脚,芯片u13的62脚还经电阻r35连接1.8v电源;芯片u13的63脚经电阻r47连接芯片u17的f16脚,芯片u13的5脚分别连接电阻r56的一端、芯片u17的a15脚,电阻r56的另一端接地;芯片u13的6脚分别连接电阻r53的一端、电阻r50的一端,电阻r53的另一端接地,电阻r50的另一端连接芯片u17的d15脚;芯片u13的35脚接地;芯片u13的21脚连接电源d-vcc3-sys;芯片u13的26脚连接电源d-vcc4-out;芯片u13的38脚连接电源d-vcc5-pll1;芯片u13的41脚连接电源d-vcc6-oscout;芯片u13的51脚连接电源d-vcc7-pll2;芯片u13的57脚连接电源d-vcc8-out;芯片u13的68脚连接电源d-vcc9-out;芯片u13的32脚分别连接电容c135的一端、电容c136的一端、电容c137的一端、电阻r651的一端,电容c135的另一端接地,电容c136的另一端分别连接电容c137的另一端、电阻r652的一端,电阻r651的另一端经电容c744接地,电阻r652的另一端接地;芯片u13的50脚经电容c745接地;芯片u13的1脚、2脚、15脚、16脚连接时钟电路a,具体的,芯片u13的1脚经电容c145连接芯片u76的39脚,芯片u13的2脚经电容c160连接芯片u76的40脚,芯片u13的15脚经电容c146连接芯片u76的36脚,芯片u13的16脚经电容c151连接芯片u76的37脚;芯片u13的22脚经电阻r32连接fmc连接器2,芯片u13的27脚经电阻r33连接另一fmc连接器2;芯片u13的55脚、56脚、53脚、54脚连接时钟电路c,具体的,芯片u13的55脚经电容c183连接u81的39脚,芯片u13的56脚经电容c192连接芯片u81的40脚,芯片u13的53脚经电容c190连接芯片u81的36脚,芯片u13的54脚经电容c195连接芯片u81的37脚。

70.芯片u76的33脚经电阻r796连接芯片u78的3脚,芯片u78的2脚经电容c788连接芯片u76的34脚,芯片u78的2脚还分别连接电感l39的一端、电容c785的一端、电容c784的一端,电容c785的另一端分别连接电容c784的另一点、电感l38的另一端、电阻r800的一端、芯片u78的4脚,电感l38的另一端接地,电阻r800的另一点连接芯片u78的1脚。

71.芯片u76的42脚连经电容c798连接芯片u80的1脚,芯片u76的43脚经电容c799连接芯片u80的3脚,芯片u80的4脚经电阻r804接地,芯片u80的5脚经电容c789连接芯片u79的1脚,芯片u79的2脚至5脚均接地。

72.芯片u76的47脚分别连接电阻r811的一端、电容c801的一端,电阻r811的另一端分别连接电阻r812的一端、电阻r810的一端,电阻r810的另一端经电容c775连接芯片u77的4脚;电阻r810的另一端还连接芯片u76的48脚;电容c801的另一端连接芯片u77的5脚,芯片u77的1脚经电阻r763连接芯片u17,芯片u77的3脚经并联的电容c764、电容c761、电容c760、电容c759、电容c773连接电源;芯片u77的3脚还接地;芯片u77的2脚经电容r793连接电源,芯片u77的6脚连接电源。

73.芯片u76的7脚经电容c781接地;芯片u76的8脚经电容c778接地;芯片u76的9脚经电容c776接地;芯片u76的11脚经电容c777接地;芯片u76的11脚还经电容c782连接芯片u76的12脚;芯片u76的46脚经电容c779接地,芯片u76的49脚经电容c80接地;芯片u76的20脚经

电阻r776连接芯片u17的e12脚,芯片u76的19脚经点入r778连接芯片u17的d16脚,芯片u76的18脚经电阻r779连接芯片u17的b12脚,芯片u76的18脚经电阻r775连接1.8v电源;芯片u76的31脚经电阻r780连接芯片u17的c12脚,芯片u76的52脚经电阻r781连接芯片u17的c12脚,芯片u76的62脚经电阻r782连接芯片u17的d12脚,芯片u13的62脚经电阻r777连接1.8v电源;芯片u13的63脚经电阻r783连接芯片u17的c14脚,芯片u76的5脚分别连接电阻r792的一端、芯片u17的a16脚;电阻r792的另一端接地;芯片u76的6脚分别连接电阻r784的一端、电阻r788的一端,电阻r788的另一端接地,电阻r784的另一端连接芯片u17的d15脚;芯片u76的35脚接地;芯片u76的10脚连接电源a-vcc1-vco;芯片u76的17脚连接电源a-vcc2-out;芯片u76的21脚连接电源a-vcc3-sys;芯片u76的26脚连接电源a-vcc4-out;芯片u76的38脚连接电源a-vcc5-pll1;芯片u76的41脚连接电源a-vcc6-oscout;芯片u76的51脚连接电源a-vcc7-pll2;芯片u76的57脚连接电源a-vcc8-out;芯片u76的68脚连接电源a-vcc9-out;芯片u76的32脚分别连接电容c135的一端、电容c136的一端、电容c744的一端,芯片u76的32脚还接地,电容c135的另一端接地,电容c136的另一端接地,电容c744的另一端接地。

74.芯片u76的50脚经电容c745接地;芯片u76还连接两个fmc连接器2,两个fmc连接器2分别为:fmc2e座子和fmc3e座子,参见图18、图19。具体的,芯片u76的1脚经电容c41连接fmc2e座子的e27脚,芯片u76的2脚经电容c52连接fmc2e座子的e28脚;芯片u76的3脚经电容c42连接fmc2e座子的e36脚,芯片u76的4脚经电容c50连接fmc2e座子的e37脚;芯片u76的15脚经电容c51连接fmc2e座子的e9脚,芯片u76的16脚经电容c54连接fmc2e座子的e10脚;芯片u76的37脚经电容c51连接fmc2e座子的e18脚,芯片u76的16脚经电容c48连接fmc2e座子的e19脚;芯片u76的24脚经电容c706连接芯片u86的aa7脚,芯片u76的25脚经电容c707连接芯片u86的aa6脚;芯片u76的22脚经电容c55连接芯片u86的n9脚,芯片u76的23脚经电容c65连接芯片u86的n8脚;芯片u76的27脚经电容c56连接芯片u86的y4脚,芯片u76的28脚经电容c67连接芯片u86的y3脚;芯片u76的29脚经电容c57连接芯片u86的p11脚,芯片u76的30脚经电容c69连接芯片u86的n11脚;芯片u76的55脚和56脚均连接在电阻r796的一端,电阻r796的另一端连接芯片u78的3脚,芯片u73的2脚分别连接电容c788的一端、电容c785的一端、电容c784的一端、电感l39的一端,电感l39的另一端接地,电容c788的另一端分别连接芯片u76的55脚和56脚,电容c785的另一端分别连接电阻r800的一端、芯片u78的4脚、电容c784的另一端和电感l38的一端,电感l38的另一端连接电源,电阻r800的另一端连接芯片u78的1脚;芯片u76的55脚和56脚还经电容c798连接芯片u80的1脚,芯片u80的3脚连接芯片u76的55脚和56脚;芯片u80的4脚经电阻r804接地;芯片u80的5脚经电容c789连接芯片u79的1脚,芯片u79的2、3、4、5脚均接地。

75.芯片u81的33脚经电阻r852连接芯片u82的3脚,芯片u82的2脚分别连接电容c845的一端、电感l41的一端、电容c844的一端、电容c843的一端,电容c845的另一端连接芯片u81的34脚。电感l41的另一端接地,电容c844的另一端分别连接电容c843的另一端、电感l40的一端和芯片u82的4脚,电感l40的另一端连接电源,电阻r872的另一端连接芯片u82的1脚。

76.芯片u81的47脚经电容c841连接芯片u85的4脚,芯片u85的5脚经电容c817分别连接芯片u81的48脚、电阻r833的一端,电阻r833的另一端分别连接电阻r834的一端、电阻r832的一端,电阻r832的另一端连接电容c841的一端,电阻r834的另一端接地,芯片u85的1

脚经电阻r854连接fpga主控模块;芯片u85的3脚经并联的电阻r842、电阻r838、电阻r837、电阻r840、电阻r839连接电源;芯片u85的3脚还接地,芯片u85的2脚经电阻r831连接电源,芯片u85的6脚连接电源。

77.芯片u81的42脚经电容c848连接芯片u84的1脚,芯片u84的3脚经电容c847连接芯片u81的43脚。

78.芯片u84的4脚经电阻r853接地,芯片u84经电容c846连接芯片u83的1脚,芯片u83的2、3、4、5、脚均接地。

79.芯片u81的7脚经电容c821接地;芯片u81的8脚经电容c819接地;芯片u81的9脚经电容c818接地;芯片u81的10脚连接电源d-vcc1-vco;芯片u81的11脚分别连接电容c820的一端、电容c812的一端,电容c820的另一端接地,电容c824的另一端连接芯片u81的12脚;芯片u81的46脚经电容c822接地;芯片u81的49脚经电容c823接地;芯片u81的18脚分别连接电阻r819的一端、电阻r815的一端,电阻r815的另一端接1.8v电源;电阻r819的另一端连接fpga主控模块;芯片u81的19脚经电阻r818连接fpga主控模块;芯片u81的20脚经电阻r817连接fpga主控模块;芯片u81的31脚经电阻r820连接芯片u17的b14脚;芯片u81的52脚经电阻r821连接芯片u17的c13脚;芯片u81的62脚经电阻r822连接芯片u17的b13脚;芯片u81的62脚还经电阻r816连接1.8v电源;芯片u81的63脚经电阻r823连接芯片u17的a13脚;芯片u81的6脚经电阻r824连接fpga主控模块;芯片u81的6脚还经电阻r825接地;芯片u81的5脚经电阻r826接地,芯片u81的5脚还连接fpga主控模块;芯片u81的35脚接地;芯片u81的17脚连接电源d-vcc2-out;芯片u81的21脚连接电源d-vcc3-sys;芯片u81的26脚连接电源d-vcc4-out;芯片u81的38脚连接电源d-vcc5-pll1;芯片u81的41脚连接电源d-vcc6-oscout;芯片u81的51脚连接电源d-vcc7-pll2;芯片u81的57脚连接电源d-vcc8-out;芯片u81的68脚连接电源d-vcc9-out;芯片u81的32脚分别连接电容c827的一端和fpga主控模块,电容c827的另一端接地。

80.芯片u81的50脚经电容c849接地;芯片u81的1脚、2脚、3脚、4脚、15脚、16脚连接时钟电路c,具体的,芯片u81的1脚经电容c148连接fmc3e座子的e27;芯片u81的2脚经电容c161连接fmc3e座子的e28;芯片u81的3脚经电容c149连接fmc3e座子的e36;芯片u81的4脚经电容c156连接fmc3e座子的e37。

81.芯片u81的15脚经电容c157连接fmc3e座子的e9,芯片u81的16脚经电容c163连接fmc3e座子的e10,芯片u81的13脚经电容c147连接fmc3e座子的e18,芯片u81的14脚经电容c152连接fmc3e座子的e19。

82.芯片u81的54脚、53脚、56脚、55脚、30脚、29脚、28脚、27脚、23脚、22脚、25脚、24脚均连接fpga主控模块。芯片u81的39脚、40脚、35脚、36脚均连接fpga主控模块。

83.本实用新型提供的多通道无人机侦控系统是一款能在27mhz~6ghz频率范围内进行实时同步测控干扰和数据采集传输信号的便携式电磁管控与干扰系统。最多可以达到支持八通道同步收发功能,可针对27mhz~54mhz固定翼无人机和75mhz~6ghz小型旋翼无人机的测控数据传输进行干扰,并对无人机导航信号进行干扰,具备无人机测向、定位功能。此系统包含3种子系统,它们分别是控制系统、接口系统和数据采集系统三部分。实现多通道同步采集侦测,各系统之间通过fmc高速连接器互联。控制系统通过fmc连接器与接口系统互联,结构层次化,各个系统互相紧密结合;控制系统内的多时钟相位同步电路设计,解

决了多通道侦控系统中需要实时同步的难题,投入使用后已经解决多通道实时同步问题,满足了广大的市场应用需求。

84.总体系统由多路时钟同步电路结合设计而成,使用相位延迟及低抖动技术,产生的相位同步时钟触发数据采集系统和控制系统,通过高速传输通道及接口系统互联,实现多通道的实时同步侦控系统。

85.当然,本实用新型还可有其它多种实施例,在不背离本实用新型精神及其实质的情况下,熟悉本领域的技术人员当可根据本实用新型作出各种相应的改变和变形,但这些相应的改变和变形都应属于本实用新型所附的权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1