一种基于折线补偿的带隙基准电路

本发明属于模拟集成电路,具体地说,是涉及一种基于折线补偿的带隙基准电路。

背景技术:

1、带隙基准(bandgap reference,bgr)的作用是产生基准电压。因为其基准电压与硅的带隙电压差不多,因而被称为带隙基准。带隙基准技术主要用于产生芯片中的电压基准,可以为系统提供稳定的工作点,在电子系统中有着不可替代的地位。

2、带隙基准的工作原理是:先产生正温度系数的电压以及负温度系数的电压,然后把两者相加,从而实现零温度系数的电压。在bulk cmos工艺中,bjt(bipolar junctiontransistor)经常被用于bgr电路的设计,只要保证两个bjt管的电流密度固定成比例,其中任意一个bjt的基极-发射极电压就拥有负温度系数,两个bjt管的基极-发射极压降之差就拥有正温度系数,将两者电压相加,就能实现零温度系数的电压。

3、在设计高精度bgr电路时,bjt管本身的基极-发射极电压特性会影响bgr电路的精确性,需要将高阶非线性项的影响减少到最小。通常采用补偿电流的方法,尽可能逼近非线性项,从而获得线性的基极-发射级电压差。

4、bjt的基极-发射极电压之差为:

5、

6、可以看到,公式含有一个线性项以及一个高阶非线性项vt当要求低温度漂移系数时,高阶项不能忽略。

7、现有技术对此的解决方案如图1、2所示,在图2中,通过mos电流镜的钳位保证结点c和d上的电压近似相等,从而使r8上的电压等于q0和q1上的基极-发射极电压差之差。由于bjt管q0和q1的发射极面积之比为2:1,因此q0和q1上的基极-发射极电压差之差为正温度系数电压,通过r8产生正温度系数电流i1为:

8、

9、其中vt是热电压。

10、而r9上的压降对应bjt管q2上的电压,为负温度系数电压,产生负温度系数电流i2为

11、

12、在图1中,由kvl定理可知,δvgs=δvbe,其中δvgs代表m1,m2的栅极-源极电压差之差,δvbe代表q5,q3的基极-发射极电压差之差。因为q5,q3发射极面积相等,所以

13、

14、其中,icomp为图1电路输出的电流,用来补偿输出基准电压的高阶非线性项。

15、由kcl定理可得

16、

17、由于q5,q4,q3都工作在恒流区,且m1,m2有相同的开启电压,所以

18、

19、其中μ(t)为载流子迁移率随温度变化的函数,一般来说β(t)为共发射极电流增益随温度变化的函数,一般有其中β∞是bjt的最大共发射极电流增益,δeg为发射极禁带宽度。

20、由于q5的基极电流远小于故将其忽略。代入i1,i2可以解得补偿电流:

21、

22、通过调整相关系数,icomp可以用以拟合曲线vt从而减少高阶项的影响。icomp的仿真结果如图3所示。

23、通过图3可以得知现有技术的方案的缺点是当温度较小时,补偿电流与非线性项之间拟合效果较差,最终产生的vbg的精确性下降。

技术实现思路

1、本发明的目的在于提供一种基于折线补偿的带隙基准电路,主要解决现有带隙基准电路在温度较小时输出电压温度系数较大的问题。

2、为实现上述目的,本发明采用的技术方案如下:

3、一种基于折线补偿的带隙基准电路,包括产生与温度成正比的ptat电流的iptat产生器,利用ptat电流生成与温度成反比的ctat电流的ictat产生器,利用ptat电流生成用于补偿的base基电流的ibase产生器,利用ptat电流和ctat电流产生用于折线补偿的fold电流的ifold产生器,以及利用ptat电流、ctat电流和base基电流生成基准电压vbg并利用fold电流进行折线补偿的vbg产生器。

4、进一步地,在本发明中,所述iptat产生器包括18个mos管m1~m18、5个晶体管q1~q5和电阻r1、电阻r2;其中,mos管m1的栅极和源极与mos管m2栅极、源极对应相连,mos管m3的源极与mos管m1的漏极相连,mos管m4的源极与mos管m2的漏极相连,mos管m3的栅极与mos管m4的栅极相连,mos管m4的漏极与mos管m2的栅极相连,mos管m5的栅极与mos管m6的栅极相连,mos管m5的漏极与mos管m3的漏极相连,mos管m5的栅极与mos管m5的漏极相连,mos管m6的漏极与mos管m4的漏极相连,晶体管q1的基极与集电极相连后与mos管m5的源极相连,晶体管q2的集电极与mos管m6的源极相连,晶体管q5的基极与集电极相连后与晶体管q1的发射极相连,电阻r1连接于晶体管q1的发射极与晶体管q5的发射极之间,电阻r2连接于晶体管q2的发射极与晶体管q5的集电极之间,mos管m7的栅极和源极与mos管m8栅极、源极对应相连,mos管m9的源极与mos管m7的漏极相连,mos管m10的源极与mos管m8的漏极相连,mos管m9的栅极与mos管m10的栅极相连,mos管m11的栅极与mos管m12的栅极相连,mos管m11的漏极与mos管m9的漏极相连,mos管m12的漏极与mos管m10的漏极相连,晶体管q3的集电极与mos管m11的源极相连,晶体管q4的集电极与mos管m12的源极相连,mos管m13的栅极与mos管m9的漏极相连,mos管m13的源极与晶体管q3的基极相连后与晶体管q2的基极相连,晶体管q3的发射极与晶体管q4的发射极相连后与晶体管q5的集电极相连,mos管m15的栅极和源极与mos管m16栅极、源极对应相连,mos管m15的栅极与mos管m15的漏极相连,mos管m14的漏极与mos管m15的漏极相连,mos管m14的源极与晶体管q4的基极相连,mos管m14的栅极与mos管m12的漏极相连,mos管m17的栅极、漏极相连后与mos管m16的漏极相连,mos管m18的栅极和源极与mos管m17栅极、源极对应相连,mos管m18的漏极与晶体管q2的发射极相连,mos管m18的源极与晶体管q5的发射极相连后接地;其中,mos管m1的源极、mos管m2的源极、mos管m7的源极、mos管m8的源极、mos管m15的源极、mos管m16的源极和mos管m13的漏极均接电源vdd。

5、进一步地,在本发明中,所述ictat产生器包括14个mos管m19~m31、m200、3个晶体管q6~q8和电阻r3、电阻r4;mos管m19的栅极与mos管m1的栅极相连,mos管m20的栅极与mos管m3的栅极相连;mos管m19的漏极与mos管m20的源极相连,mos管m22的栅极和源极与mos管m23的栅极、源极对应相连,mos管m20的漏极与mos管m21的栅极相连,mos管m21的漏极与mos管m22的漏极相连,晶体管q6的集电极与mos管m21的栅极相连,晶体管q6的基极与mos管m21的源极相连,mos管m24的栅极与mos管m22的栅极和漏极均相连,电阻r3连接于mos管m23的漏极和晶体管q6的发射极之间,电阻r4连接于mos管m24的漏极和晶体管q6的发射极之间,mos管m27的栅极和源极与mos管m28的栅极、源极对应相连,mos管m29的栅极与mos管m30的栅极相连后与mos管m19的栅极相连,mos管m29的源极与mos管m27的漏极相连,mos管m30的源极与mos管m28的漏极相连,晶体管q7的集电极与mos管m25的栅极相连后与mos管m29的漏极相连,mos管m200的漏极与栅极相连后与mos管m25的漏极相连,晶体管q7的基极与mos管m25的源极相连后与mos管m24的漏极相连,晶体管q8的集电极与mos管m26的栅极相连后与mos管m30的漏极相连,晶体管q8的基极与mos管m26的源极相连后与mos管m23的漏极相连,晶体管q7的发射极和晶体管q8的发射极相连后与和晶体管q6的发射极相连并接地,mos管m31的漏极、栅极相连后与mos管m26的漏极相连;其中,mos管m19的源极、mos管m22的源极、mos管m23的源极、mos管m24的源极、mos管m27的源极、mos管m28的源极、mos管m31和mos管m200的源极均接电源vdd;mos管m31的漏极与栅极相连后与ifold产生器相连。

6、进一步地,在本发明中,所述ibase产生器包括由6个mos管m32~m37和一个晶体管q9组成,mos管m32的栅极与mos管m1的栅极相连,mos管m33的栅极与mos管m3的栅极相连,mos管m32的漏极与mos管m33的源极相连,mos管m37的栅极与mos管m33的漏极相连后与晶体管q9的集电极相连,mos管m37的源极与晶体管q9的基极相连,mos管m36的源极与晶体管q9的发射极相连后接地,mos管m36的栅极与漏极相连后与mos管m35的漏极相连,mos管m35的栅极与mos管m34的栅极相连后与ifold产生器相连,mos管m34的栅极与漏极相连后与mos管m37的漏极相连;其中,mos管m32的源极、mos管m34的源极和mos管m35的源极均接电源vdd。

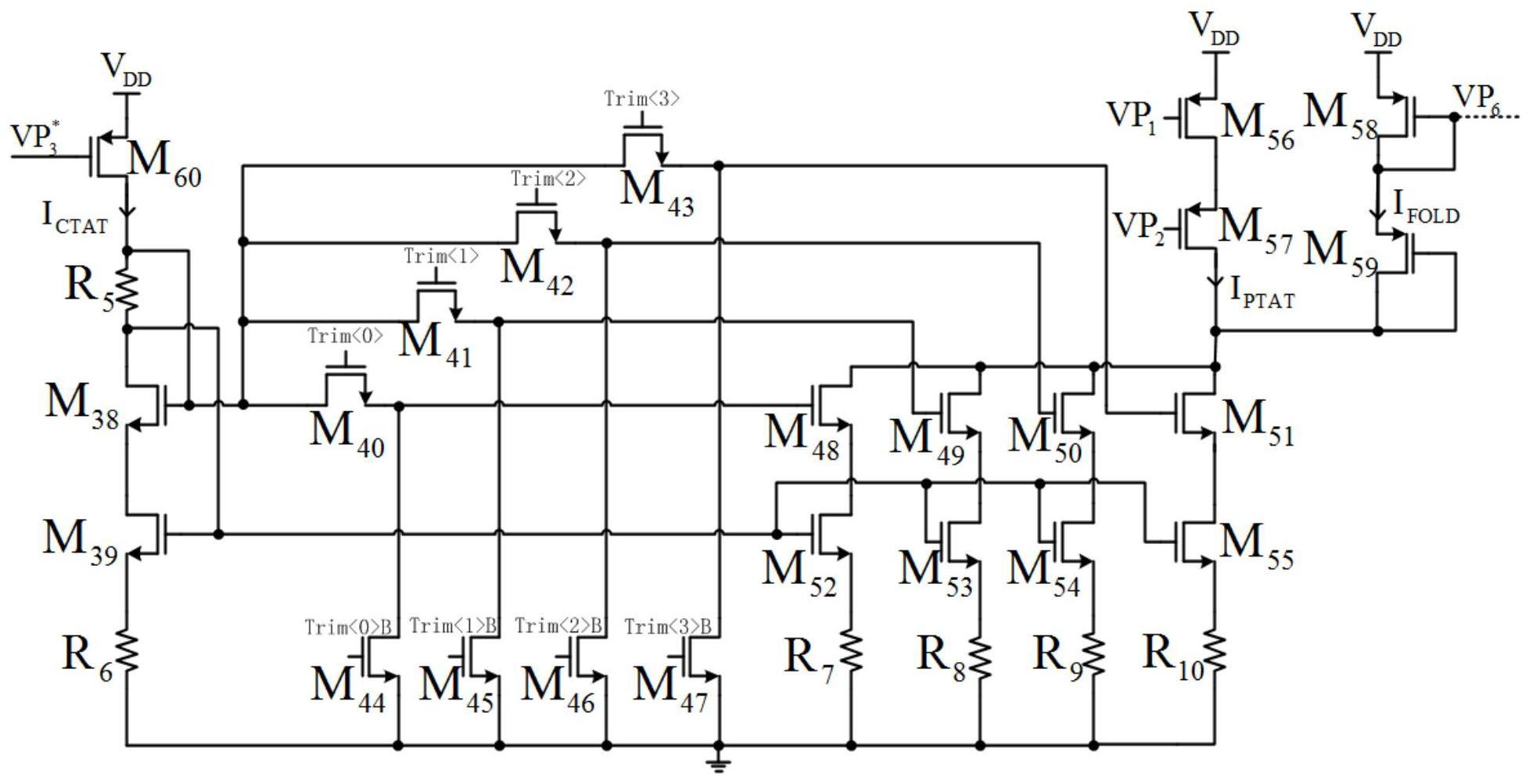

7、进一步地,在本发明中,所述ifold产生器由23个mos管m38~m60和6个电阻r5~r10组成,所述mos管m60的栅极与mos管m32的栅极相连,mos管m60的漏极与电阻r5的一端相连,mos管m38的漏极与电阻r5的另一端相连,mos管m38的栅极与mos管m60的漏极相连,mos管m38的源极与mos管m39的漏极相连,mos管m39的栅极与mos管m38的漏极相连,mos管m40、mos管m41、mos管m42和mos管m43的漏极均与mos管m38的栅极相连,mos管m44的漏极与mos管m40的源极相连,mos管m45的漏极与mos管m41的源极相连,mos管m46的漏极与mos管m42的源极相连,mos管m47的漏极与mos管m43的源极相连,mos管m48的栅极与mos管m40的源极相连,mos管m49的栅极与mos管m41的源极相连,mos管m50的栅极与mos管m42的源极相连,mos管m51的栅极与mos管m43的源极相连,mos管m52、mos管m53、mos管m54和mos管m55的栅极均与mos管m39的栅极相连,mos管m48、mos管m49、mos管m50和mos管m51的源极与mos管m52、mos管m53、mos管m54和mos管m55的漏极对应相连,mos管m39、mos管m52、mos管m53、mos管m54和mos管m55的源极与电阻r6~r10的一端对应相连,电阻r6~r10的另一端及mos管m44、mos管m45、mos管m46和mos管m47的源极相连后接地,mos管m57的漏极与mos管m51的漏极相连,mos管m56的漏极与mos管m57的源极相连,mos管m59的漏极和栅极相连后与mos管m51的漏极相连,mos管m58的漏极和栅极相连后与mos管m59的源极相连,mos管m56的栅极与mos管m1的栅极相连,mos管m57的栅极与mos管m2的栅极相连,mos管m60的源极、mos管m56的源极和mos管m58的源极均接电源vdd,mos管m58的漏极与栅极相连后与vbg产生器相连。

8、进一步地,在本发明中,所述vbg产生器包括3个电路结构相同并串联连接的曲率补偿模块和一个与最后一级曲率补偿模块相连的折线补偿模块。

9、进一步地,在本发明中,所述曲率补偿模块由9个mos管m61~m69和2个晶体管q10、q11组成;所述mos管m61的栅极与mos管m62的栅极相连,mos管m61的栅极与漏极相连后与mos管m63的漏极相连,mos管m63的栅极与mos管m65的漏极相连后与晶体管q10的集电极相连,mos管m65的源极与mos管m64的漏极相连,mos管m62的漏极与晶体管q10的基极相连后与晶体管q11的基极相连,mos管m67的漏极与mos管m69的漏极相连后与晶体管q11的集电极相连,mos管m66的漏极与mos管m67的源极相连,mos管m68的漏极与晶体管q11的发射极相连后连接到下一级的与该级mos管m63位置相同的mos管的源极,mos管m68的栅极与晶体管q11的集电极相连,mos管m63的源极、晶体管q11的发射极和mos管m68的源极相连后接地,mos管m61的源极、mos管m62的源极、mos管m66的源极和mos管m69的源极均接电源vdd,mos管m64的栅极和mos管m66的栅极相连后与mos管m1的栅极相连,mos管m65的栅极和mos管m67的栅极相连后与mos管m2的栅极相连。

10、进一步地,在本发明中,所述折线补偿模块由14个mos管m88~m101、2个晶体管q16、q17和3个电阻r11~r13组成;mos管m88的漏极与mos管m89的源极相连,mos管m89的漏极与最后一级的曲率补偿模块中的同第一级曲率补偿模块中mos管m68位置相同的mos管的漏极相连,电阻r11的一端与mos管m89的漏极相连,电阻r11的另一端与晶体管q16的发射极相连,mos管m93的漏极和mos管m94的栅极相连后与晶体管q16的集电极相连,mos管m93的源极和mos管m92的漏极相连,mos管m90栅极和漏极相连后与mos管m94的漏极相连,mos管m90的栅极和mos管m91的栅极相连,mos管m91的漏极和晶体管q16的基极相连后与晶体管q17的基极相连,mos管m99的漏极与mos管m100的漏极相连后与晶体管q17的集电极相连,mos管m98的漏极与mos管m99的源极相连,mos管m99的漏极与mos管m100的源极相连,mos管m95的源极与mos管m96的源极相连后与晶体管q16的发射极相连,mos管m97的漏极与晶体管q17的集电极相连,电阻r13的一端与mos管m97的漏极相连,电阻r13的另一端与电阻r12的一端相连,电阻r12的另一端与晶体管q17的基极相连,mos管m94的源极、mos管m95的漏极、mos管m96的漏极、mos管m101的漏极和mos管m97的源极均接地,mos管m90的源极、mos管m91的源极、mos管m98的源极和mos管m100的源极均接电源vdd,mos管m92的栅极和mos管m98的栅极相连后与mos管m1的栅极相连,mos管m93的栅极和mos管m99的栅极相连后与mos管m2的栅极相连,mos管m100的栅极与mos管m31的栅极相连,mos管m101的栅极与mos管m58的栅极相连,电阻r13与电阻r12相连的公共端产生带隙基准电压vbg。

11、进一步地,在本发明中,还包括利用ptat电流和ctat电流产生用于弥补生产过程中不可避免误差的trim电流的itrim产生器。

12、与现有技术相比,本发明具有以下有益效果:

13、本发明的带隙电压基准电路通过ifold产生器产生一个仅在小于设定温度时电流值不为0的折叠电流ifold,去对原输出电压在温度小于设定温度的部分进行补偿,从而得到了一个较为理想的温度系数。这种设计解决了现有技术在温度较小时输出电压温度系数较大的问题,获得了随温度变化更加稳定的带隙基准电压。同时,这种补偿是对特定温度区间的精准补偿,也就是说只需要对ifold进行调节,就可以满足不同客户对于输出基准电压的温度系数的需求,因此具有较广的适用范围。

- 还没有人留言评论。精彩留言会获得点赞!