LDO电路、LDO以及SOC系统的制作方法

本公开涉及集成电路,尤其涉及线性稳压器电路,具体涉及一种ldo电路、ldo以及soc系统。

背景技术:

1、随着系统级芯片(system on chip,soc)的持续发展,对低压差线性稳压器(lowdropout regulator,ldo)的要求也是越来越苛刻。例如,锁相环中多核压控振荡器(multicore voltage-controlled oscillator,multi core vco)的应用,需要ldo支持较大的负载电流的同时保证环路相位裕度大于45°,且拥有较高的从电源到输出的增益,即电源抑制比(power supply rejection,psr),来防止从ldo输入端噪声耦合到multi core vco内部。

2、ldo对目标负载电流范围内的环路相位裕度和psr是有严格要求的,但由于片外电容的发展,很多片外电容的等效串联电阻(equivalent series resistance,esr)在0-1m范围内只有几十毫欧,以至于无法达到在ldo环路建立零点的作用,使得当前ldo电路在目标负载电流范围内保证相位裕度大于45°基本无法实现,最终导致ldo输出电压振荡。

3、导致ldo无法正常工作的三个原因:(1)ldo的psr指标过高,导致ldo输入端噪声耦合到ldo输出端;(2)ldo的esr零点无法在环路内建立,导致环路相位裕度低于45°,导致ldo输出电压振荡;(3)ldo负载电流过大,导致ldo输出不正常。

4、基于上述导致ldo无法正常工作的原因,可见当前ldo电路主要存在以下问题:(1)需要牺牲功耗,增加误差放大器增益来降低psr。(2)需要外挂电容esr电阻建立零点补偿环路,当esr电阻过小时,环路会产生振荡。(3)无法满足较大的负载电流需求,过大的负载电流会使传统的ldo无法正常工作。

技术实现思路

1、本公开提供了一种ldo电路、ldo以及soc系统。

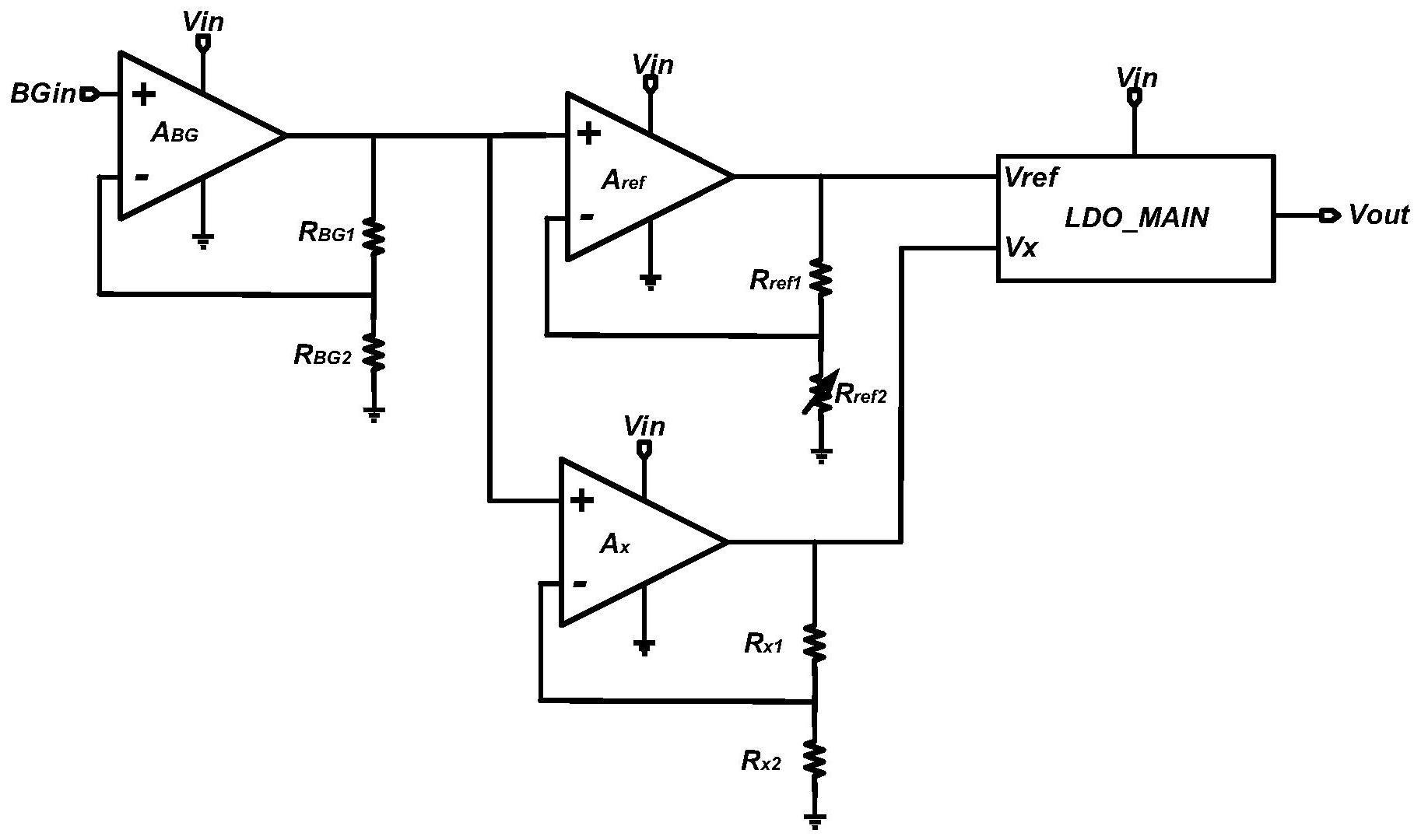

2、根据本公开的第一方面,提供了一种ldo电路。该ldo电路包括:放大器abg、放大器aref、放大器ax以及ldo主体结构;

3、所述放大器abg用于根据基准电流产生电压vbg提供给所述放大器aref和所述放大器ax;

4、所述放大器aref用于产生电压vref提供给所述ldo主体结构;

5、所述放大器ax用于产生电压vx提供给所述ldo主体结构;

6、所述ldo主体结构用于根据电压vref和vx产生输出电压;

7、所述放大器abg的同相输入端与基准电流连接,反相输入端通过电阻rbg2接地并通过电阻rbg1与输出端连接;

8、所述放大器aref的同相输入端与所述放大器abg的输出端连接,反相输入端通过电阻rref2接地并通过电阻rref1与输出端连接;

9、所述放大器ax的同相输入端与所述放大器abg的输出端连接,反相输入端通过电阻rx2接地并通过电阻rx1与输出端连接;

10、所述ldo主体结构的vref端口与所述放大器aref的输出端连接;vx端口与所述放大器ax的输出端连接;输出端与电路输出端连接。

11、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述ldo主体结构包括误差放大器aea、晶体管ml、晶体管my、晶体管mq、晶体管mx、晶体管mp、反馈电阻rs、片外电容c1、等效电阻resr以及负载电阻rload;

12、所述误差放大器aea的同相输入端与所述放大器aref的输出端连接,反相输入端通过所述反馈电阻rs与电路输出端连接,正电源端与所述放大器ax的输出端连接,负电源端接地;

13、所述晶体管ml的栅极与所述误差放大器aea的输出端连接,源级接地,漏极与所述晶体管my的源级连接;所述晶体管my的漏极通过电阻r5与电源电压连接,栅极通过所述负载电阻rload接地;所述晶体管mq的源级通过电阻r4与电源电压连接,漏极通过电阻r3接地,栅极接地;所述晶体管mx的栅极通过电阻r3接地,源级与电源电压连接,漏极与电路输出端连接,衬底与所述晶体管mp的栅极连接;所述晶体管mp的源级与电源电压连接,漏极与电路输出端连接并通过所述负载电阻rload接地;所述片外电容c1的一端接地,另一端通过所述等效电阻resr与电路输出端连接。

14、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述ldo主体结构还包括零点补偿结构;

15、所述零点补偿结构用于产生反馈电压vfeedback提供给所述误差放大器aea;

16、所述零点补偿结构的电源输入端口接与电源电压连接,vfeedback端口与所述误差放大器aea连接并通过所述反馈电阻rs接电路输出端。

17、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述零点补偿结构包括晶体管m1、晶体管m2、晶体管m3、晶体管m4、放大器aesr、快速启动电阻ron以及rc滤波结构;

18、所述晶体管m3的源级与电源电压连接,栅极通过电阻r3接地、衬底与所述晶体管m4的栅极连接、漏极分别与所述放大器aesr的同相输入端和所述晶体管m1的漏极连接;所述晶体管m4的源级与电源电压连接,衬底与所述晶体管mx的栅极连接,漏极与所述晶体管m2的漏极连接并通过所述快速启动电阻ron与所述放大器aesr的反相输入端连接;所述放大器aesr的输出端与所述晶体管m1的栅极连接并通过所述rc滤波结构与所述晶体管m2的栅极连接;所述晶体管m1的源级通过电阻r1接地,所述晶体管m2的源级通过电阻r2接地。

19、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述ldo主体结构还包括过流保护结构;

20、所述过流保护结构用于产生过流保护电压vctrl提供给所述晶体管my;

21、所述过流保护结构的输入端口分别与所述晶体管mx和所述晶体管mp的漏极连接,电压输出端口与电路输出端连接,vctrl端口与所述晶体管my的栅极连接。

22、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述过流保护结构包括晶体管p1、晶体管p2、晶体管n1、晶体管n2、晶体管n3以及片外电容c2;

23、所述晶体管p1的源级通过电阻rb1与所述mx晶体管的漏极连接,栅极与所述晶体管p2的栅极连接,漏级与所述晶体管n1的漏极连接;所述晶体管p2的源级通过电阻rb2与所述晶体管mp的漏极连接,漏级与所述晶体管n2的漏极连接,栅极和漏极互接;所述晶体管n1的源级接地,栅极与所述晶体管n2的栅极连接,漏极和栅极互接;所述晶体管n2的源级接地,栅极与所述晶体管n3的栅极连接;所述晶体管n3的源级接地、漏极与所述晶体管m2的栅极连接;所述片外电容c1的一端分别与所述晶体管mp的漏极和电路输出端连接,另一端接地。

24、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述放大器abg、所述放大器aref以及所述放大器ax为非反相放大器。

25、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述电阻rref2为可调电阻。

26、根据本公开的第二方面,提供了一种ldo。该ldo包括如以上所述的ldo电路。

27、根据本公开的第三方面,提供了一种soc系统。该soc系统包括如以上所述的ldo电路。

28、本技术实施例提供的一种ldo电路、ldo以及soc系统,ldo电路包括放大器abg、放大器aref、放大器ax以及ldo主体结构,放大器abg的同相输入端与基准电流连接,反相输入端通过电阻rbg2接地并通过电阻rbg1与输出端连接;放大器aref的同相输入端与放大器abg的输出端连接,反相输入端通过电阻rref2接地并通过电阻rref1与输出端连接;放大器ax的同相输入端与放大器abg的输出端连接,反相输入端通过电阻rx2接地并通过电阻rx1与输出端连接;ldo主体结构的vref端口与放大器aref的输出端连接;vx端口与放大器ax的输出端连接;输出端与电路输出端连接;基于此,放大器abg根据基准电流产生电压vbg提供给放大器aref和放大器ax,放大器aref产生参考电压vref提供给ldo主体结构,放大器ax产生一个稳定的电压vx提供给ldo主体结构,为ldo主体结构中的误差放大器提供电源电压,增加误差放大器的增益来减小psr指标,从而使ldo主体结构根据电压vref和vx产生输出电压,进一步减小psr参数,进而减小外部噪声对频率合成器中multi core vco模块的影响。

29、应当理解,

技术实现要素:

部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!