一种基于FPGA的逻辑分析仪的触发方法及装置与流程

本发明涉及fpga比较触发,具体涉及一种基于fpga的逻辑分析仪的触发方法及装置。

背景技术:

1、随着技术发展的需要,调试工具的使用也更加频繁,调试工具往往需要对信号进行监测,如利用基于fpga(field programmable gate array,现场可编程门阵列)的逻辑分析仪实现比较触发,即将监测信号与触发条件进行比较得到对应的触发结果。目前基于fpga逻辑分析仪的单比特触发和多比特触发往往单独进行,比较触发的方式不够灵活,难以根据多种触发条件实现单比特触发和多比特触发的组合,限制了应用场景。因此,现有技术中存在基于fpga的逻辑分析仪的触发方法不灵活的问题。

技术实现思路

1、有鉴于此,本发明提供了一种基于fpga的逻辑分析仪的触发方法及装置,以解决基于fpga的逻辑分析仪的触发方法不灵活的问题。

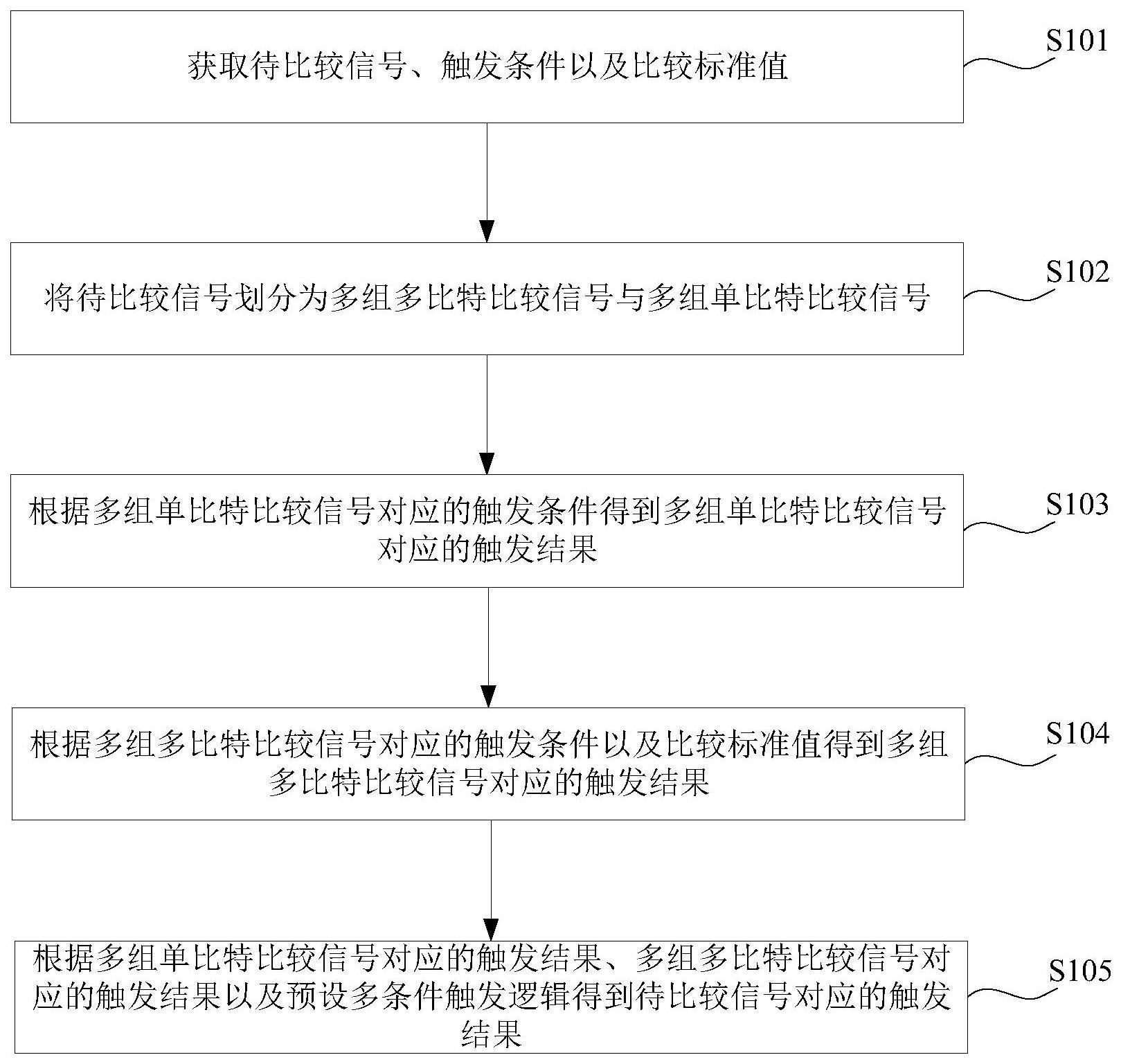

2、第一方面,本发明提供了一种基于fpga的逻辑分析仪的触发方法,包括:获取待比较信号、触发条件以及比较标准值;将待比较信号划分为多组多比特比较信号与多组单比特比较信号;根据多组单比特比较信号对应的触发条件得到多组单比特比较信号对应的触发结果;根据多组多比特比较信号对应的触发条件以及比较标准值得到多组多比特比较信号对应的触发结果;根据多组单比特比较信号对应的触发结果、多组多比特比较信号对应的触发结果以及预设多条件触发逻辑得到待比较信号对应的触发结果。

3、在本发明实施例中,通过将待比较信号进行灵活划分,得到多组多比特比较信号以及多组单比特比较信号,将各组比较信号与对应的触发条件进行比较,然后将对应的触发结果以预设多条件触发逻辑进行运算,得到待比较信号最终的触发结果。实现了将单比特触发和多比特触发进行灵活组合的目的,达到了根据多种触发条件生成包含多个分组的待比较信号触发结果的目的,能够适应多种比较方式,提升了逻辑分析仪的灵活度及性能,进而解决了相关技术中存在的基于fpga的逻辑分析仪的触发方法不灵活的问题。

4、在一种可选的实施方式中,多组单比特比较信号对应的触发结果以及多组多比特比较信号对应的触发结果由每1比特的比较信号产生的4比特的触发中值通过逻辑运算确定。

5、在本发明实施例中,对每1比特的比较信号产生的4比特的触发中值进行逻辑运算,从而确定比较信号对应的触发结果,实现了将单比特触发和多比特触发进行统一处理的目的,为待比较信号进行灵活分组提供了实现基础,达到了增加逻辑分析仪触发应用场景的目的。

6、在一种可选的实施方式中,在将待比较信号划分为多组多比特比较信号与多组单比特比较信号之后,方法还包括:利用2比特的指示信号区分单比特比较信号、多比特比较信号的头部、多比特比较信号的中部以及多比特比较信号的尾部。

7、在本发明实施例中,由于单比特触发和多比特触发不同位的触发中值计算方式不同,因此使用2比特对其进行区分表示,从而实现了同时处理单比特比较触发和多比特比较触发的目的。

8、在一种可选的实施方式中,根据多组多比特比较信号对应的触发条件以及比较标准值得到多组多比特比较信号对应的触发结果,包括:以单比特为单位采取并行方式将任意一组多比特比较信号与对应的比较标准值比较,得到多个单比特的比较信号对应的比较结果,单比特的比较信号对应的比较结果为4比特的触发中值包含的2比特的比较结果;将多个单比特的比较信号对应的比较结果拆分为两组多比特的数据;对两组多比特的数据求和得到两组多比特数据的和;将两组多比特数据的和与4比特的触发中值包含的另外2比特进行逻辑运算,得到任意一组多比特比较信号对应的触发结果;根据任意一组多比特比较信号对应的触发结果确定多组多比特比较信号对应的触发结果。

9、在本发明实施例中,给出了多组多比特比较信号任意一组比较触发的具体实现方式,实现了得到多比特比较信号对应的触发结果的目的。

10、在一种可选的实施方式中,对两组多比特的数据求和得到两组多比特数据的和,包括:对两组多比特的数据进行分段,得到多个分段;利用carry进位链计算多个分段对应的有进位计算结果和无进位计算结果;根据多个分段对应的有进位计算结果和无进位计算结果得到两组多比特数据的和。

11、在本发明实施例中,当多比特比较信号的位宽较大时,利用carry进位链对时序和逻辑资源进行优化,即当信号位宽过大时,进行分组处理。从而达到了降低功耗、节省资源,提升逻辑分析仪性能的目的。

12、在一种可选的实施方式中,逻辑运算包括:d|(c&(a+b)),其中,a、b、c、d为每1比特的比较信号产生的4比特的触发中值,多比特比较时,a+b为两组多比特数据的和,(c,d)根据2比特的指示信号确定,单比特比较时,(a,b)固定为(1,0),(c,d)根据是否满足单比特比较信号对应的触发条件等于(0,0)或(1,1)。

13、在本发明实施例中,给出了逻辑运算以及触发中值计算策略的一种具体实现方式,从而实现了将单比特触发和多比特触发进行灵活组合的目的,能够适应多种比较方式,提升了逻辑分析仪的灵活度及性能,解决了相关技术中存在的基于fpga的逻辑分析仪的触发方法不灵活的问题。

14、在一种可选的实施方式中,多比特比较信号的头部对应的(a,b)为(0,0),(c,d)为多比特比较信号的头部与对应的比较标准值的比较结果,多比特比较信号的中部和尾部对应的(a,b)为多比特比较信号的头部和尾部与对应的比较标准值的比较结果,多比特比较信号的中部和尾部对应的(c,d)为(0,0)。

15、在本发明实施例中,根据指示信号的不同为各比特触发中值的计算配置不同的策略,达到了提高逻辑分析仪比较触发通用性的目的。

16、第二方面,本发明提供了一种基于fpga的逻辑分析仪的触发装置,包括:获取模块,用于获取待比较信号、触发条件以及比较标准值;信号划分模块,用于将待比较信号划分为多组多比特比较信号与多组单比特比较信号;单比特比较触发模块,用于根据多组单比特比较信号对应的触发条件得到多组单比特比较信号对应的触发结果;多比特比较触发模块,用于根据多组多比特比较信号对应的触发条件以及比较标准值得到多组多比特比较信号对应的触发结果;比较触发组合模块,用于根据多组单比特比较信号对应的触发结果、多组多比特比较信号对应的触发结果以及预设多条件触发逻辑得到待比较信号对应的触发结果。

17、在一种可选的实施方式中,多组单比特比较信号对应的触发结果以及多组多比特比较信号对应的触发结果由每1比特的比较信号产生的4比特的触发中值通过逻辑运算确定。

18、在一种可选的实施方式中,装置还包括:指示信号区分模块,用于利用2比特的指示信号区分单比特比较信号、多比特比较信号的头部、多比特比较信号的中部以及多比特比较信号的尾部。

19、在一种可选的实施方式中,多比特比较触发模块包括:单比特并行比较单元,用于以单比特为单位采取并行方式将任意一组多比特比较信号与对应的比较标准值比较,得到多个单比特的比较信号对应的比较结果,单比特的比较信号对应的比较结果为4比特的触发中值包含的2比特的比较结果;拆分单元,用于将多个单比特的比较信号对应的比较结果拆分为两组多比特的数据;求和单元,用于对两组多比特的数据求和得到两组多比特数据的和;逻辑运算单元,用于将两组多比特数据的和与4比特的触发中值包含的另外2比特进行逻辑运算,得到任意一组多比特比较信号对应的触发结果;触发结果确定单元,用于根据任意一组多比特比较信号对应的触发结果确定多组多比特比较信号对应的触发结果。

20、在一种可选的实施方式中,求和单元包括:分段子单元,用于对两组多比特的数据进行分段,得到多个分段;优化计算子单元,用于利用carry进位链计算多个分段对应的有进位计算结果和无进位计算结果;优化求和子单元,用于根据多个分段对应的有进位计算结果和无进位计算结果得到两组多比特数据的和。

21、在一种可选的实施方式中,逻辑运算包括:d|(c&(a+b)),其中,a、b、c、d为每1比特的比较信号产生的4比特的触发中值,多比特比较时,a+b为两组多比特数据的和,(c,d)根据2比特的指示信号确定,单比特比较时,(a,b)固定为(1,0),(c,d)根据是否满足单比特比较信号对应的触发条件等于(0,0)或(1,1)。

22、在一种可选的实施方式中,多比特比较信号的头部对应的(a,b)为(0,0),(c,d)为多比特比较信号的头部与对应的比较标准值的比较结果,多比特比较信号的中部和尾部对应的(a,b)为多比特比较信号的头部和尾部与对应的比较标准值的比较结果,多比特比较信号的中部和尾部对应的(c,d)为(0,0)。

23、第三方面,本发明提供了一种计算机设备,包括:存储器和处理器,存储器和处理器之间互相通信连接,存储器中存储有计算机指令,处理器通过执行计算机指令,从而执行上述第一方面或其对应的任一实施方式的基于fpga的逻辑分析仪的触发方法。

24、第四方面,本发明提供了一种计算机可读存储介质,该计算机可读存储介质上存储有计算机指令,计算机指令用于使计算机执行上述第一方面或其对应的任一实施方式的基于fpga的逻辑分析仪的触发方法。

- 还没有人留言评论。精彩留言会获得点赞!