一种高速双通道跟踪保持电路

本发明涉及集成电路,尤其涉及一种高速双通道跟踪保持电路。

背景技术:

1、随着集成电路技术的飞速发展,模数转换器所处理的模拟信号频率越来越高,需要adc中跟踪保持模块具有很高的输入带宽和较高的线性度,为了解决这一问题,现有技术中采用了双通道开环跟踪保持模块,整体电路的采样率为单通道的两倍,有效的提高了采样速率。

2、但随着模拟信号频率的增加,模拟输入信号对采样电容上的保持电压的影响越来越明显,导致失调补偿电路的精度与线性度明显降低,电路中还存在时钟馈通、电荷注入效应。

技术实现思路

1、本发明通过提供一种高速双通道跟踪保持电路,解决了现有技术中采样电路的精度和线性度,与电路中存在时钟馈通和电荷注入效应的问题,实现了对电路进行失调误差校准,且消除了电路的时钟馈通效应,使电路的线性度得到提高。

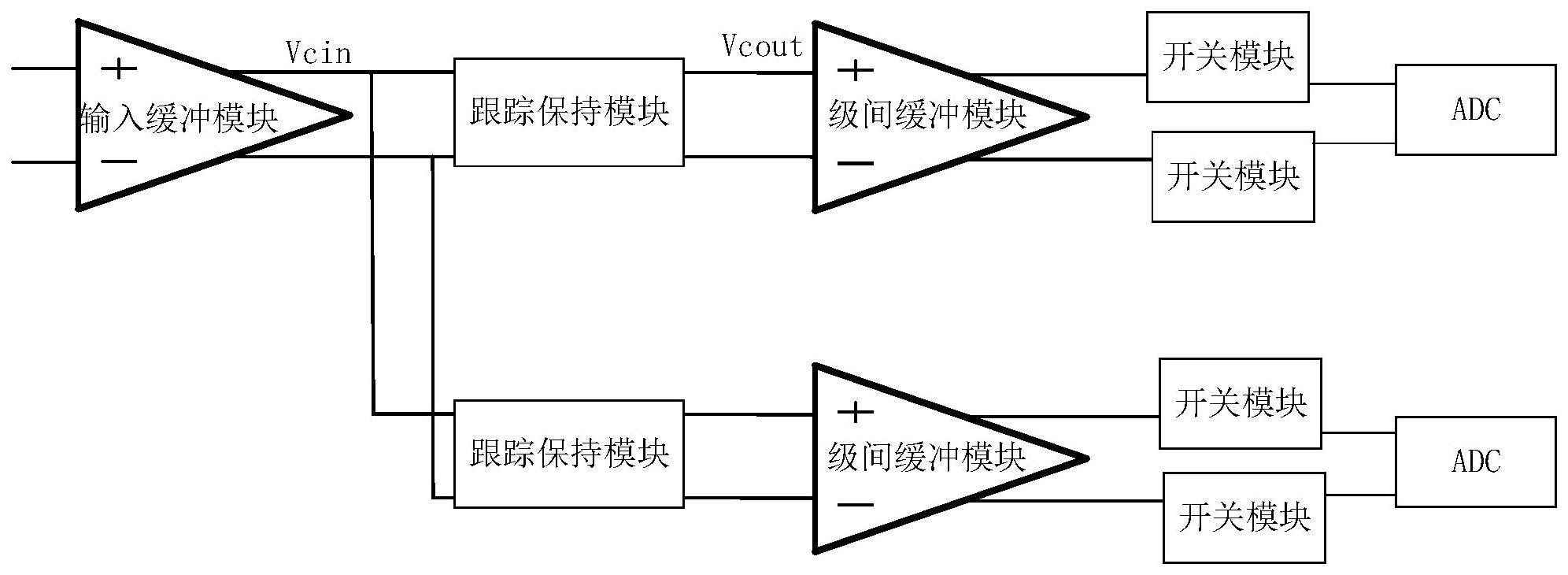

2、本发明提供了一种高速双通道跟踪保持电路,该电路包括:依次串联的输入缓冲模块、跟踪保持模块、级间缓冲模块和开关模块;

3、所述输入缓冲模块用于将前级电路与所述跟踪保持模块隔离,得到稳定输入电压;

4、所述跟踪保持模块用于根据失调补偿后的失调补偿电路以及采样保持电路对所述稳定输入电压进行采样,得到采样电压;

5、所述级间缓冲器利用源极负反馈,得到与所述稳定输入电压电位相反的级间缓冲输出电压;

6、所述开关模块用于对所述级间缓冲输出电压保持至下级电路中。

7、在一种可能的实现方式中,所述失调补偿电路对所述跟踪保持模块中的稳定输入电压与所述采样电压之间的电压差进行补偿。

8、在一种可能的实现方式中,所述根据失调补偿后的失调补偿电路以及采样保持电路对所述稳定输入电压进行采样,得到采样电压,具体包括:

9、实时判断当前采样时钟是否为高电平;

10、若是,则将所述跟踪保持模块与所述输入缓冲模块导通,且与所述级间缓冲模块断开,将所述稳定输入电压保持至所述采样保持电路上,得到所述采样电压;

11、若否,则将所述跟踪保持模块与所述输入缓冲模块断开,且与所述级间缓冲模块导通,将所述稳定输入电压保持至所述采样保持电路与所述失调补偿电路上,得到所述采样电压;

12、将所述采样电压传递至所述开关模块上。

13、在一种可能的实现方式中,所述失调补偿电路,具体包括:第一补偿电容cc1、第二补偿电容cc2、开关e1、开关e2、开关e3、开关e4和补偿电源vc;

14、所述补偿电源vc与所述开关e2、所述开关e3的一端并联;

15、所述开关e2的另一端与所述开关e1的一端、所述第一补偿电容cc1的一段并联;

16、所述开关e1的另一端与所述开关e4的一端并联接地;

17、所述开关e4的另一端与所述开关e3的另一端、所述第二补偿电容cc2的一端并联;

18、所述第一补偿电容cc1另一端与所述采样保持电路并联;

19、所述第二补偿电容cc2的另一端与所述采样保持电路并联。

20、在一种可能的实现方式中,所述采样保持电路,具体包括:第一级采样开关t1、第一级采样开关t11、第一级采样电容cs1以及第一级采样电容cs2;

21、所述第一级采样开关t1的一端与所述输入缓冲模块连接,另一端与所述第一级采样电容cs1的一端、所述失调补偿电路并联;

22、所述第一级采样电容cs1的另一端接地;

23、所述第一级采样开关t11的一端与所述输入缓冲模块连接,另一端与所述第一级采样电容cs2的一端、所述失调补偿电路并联;

24、所述第一级采样电容cs2的另一端接地。

25、在一种可能的实现方式中,所述输入缓冲模块,具体包括:nmos管m1、nmos管m2、nmos管m3、nmos管m4、nmos管m5、nmos管m6、nmos管m7以及、nmos管m8;

26、所述nmos管m1的漏极与vdd连接,栅极与输入信号的负相端连接,源极与正向输出端连接,衬底与所述nmos管m5的衬底连接;

27、所述nmos管m2的漏极与vdd连接,栅极与输入信号的负相端连接,源极与负向输出端连接,衬底与所述nmos管m8的漏极连接;

28、所述nmos管m3的漏极与正向输出端连接,栅极与偏置电压vbias连接,源极接地;

29、所述nmos管m4的漏极与负向输出端连接,栅极与偏置电压vbias连接,源极接地;

30、所述nmos管m5的漏极与vdd连接,栅极与输入信号的负相端连接,源极与所述nmos管m5的衬底连接;

31、所述nmos管m6的漏极与vdd连接,栅极与输入信号的负相端连接,源极与所述nmos管m6的衬底连接,衬底与所述nmos管m6的源极连接;

32、所述nmos管m7的漏极与所述nmos管m5的衬底连接,栅极与偏置电压vbias连接,源极接地;

33、所述nmos管m8的漏极与所述nmos管m2的衬底连接,栅极与偏置电压vbias连接,源极接地。

34、在一种可能的实现方式中,所述级间缓冲模块,具体包括:nmos管m9、nmos管m10、nmos管m11和nmos管m12、电阻r1、电阻r2、电阻r3、电阻r4以及尾电流源id;

35、所述nmos管m9的栅极与所述跟踪保持模块连接,源极与所述电阻r1的一端连接,漏极和所述电阻r3的一端与输出端并联;

36、所述nmos管m10的栅极与所述跟踪保持模块连接,源极与所述电阻r2的一端连接,漏极所述电阻r4的一端与输出端并联;

37、所述nmos管m11的漏极与vdd连接,栅极与偏置电压vbias连接,源极和所述电阻r3的另一端与输出端并联;

38、所述nmos管m12的漏极与vdd连接,栅极与偏置电压vbias连接,源极和所述电阻r4的另一端与输出端并联;

39、所述电阻r1的另一端和所述电阻r2的另一端与所述尾电流源id的一端并联;

40、所述尾电流源id的另一端与负电源ve连接。

41、在一种可能的实现方式中,所述级间缓冲模块中信号的增益具体表示为:

42、

43、其中,gm1表示所述nmos管m9的跨导;gm3表示所述nmos管m11的跨导。

44、在一种可能的实现方式中,所述开关模块,具体包括:nmos管m13、nmos管m14、nmos管m15、nmos管m16以及nmos管m17;

45、所述nmos管m17的栅极与第一时钟连接,漏极与所述级间缓冲模块连接,源极与输出端连接;

46、所述nmos管m13的栅极与所述级间缓冲模块连接,源极、漏极与输出端连接;

47、所述nmos管m14的源极、漏极与所述级间缓冲模块连接,栅极与输出端连接;

48、所述nmos管m15的源极、漏极与输出端连接,栅极与与第二时钟连接;

49、所述nmos管m16的栅极与输出端连接,源极、漏极与第二时钟连接。

50、在一种可能的实现方式中,所述第一时钟连接与所述第二时钟相位相反。

51、本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

52、本发明通过采用了一种高速双通道跟踪保持电路,该电路包括:依次串联的输入缓冲模块、跟踪保持模块、级间缓冲模块和开关模块;输入缓冲模块用于将前级电路与跟踪保持模块隔离,得到稳定输入电压;输入缓冲模块在输入对管的旁边并联一个差分的输入对管,跟踪输入信号,同时去驱动输入管的衬底,这样输入管的源级电压与衬底电压相差很小,基本消除了体效应,使差分输入管的电压不随输入信号的变化而变化,缓冲器电路的线性度得到提高;跟踪保持模块用于根据失调补偿后的失调补偿电路以及采样保持电路对稳定输入电压进行采样,得到采样电压,对时钟抖动、时钟馈通、电荷注入、电荷泄露、电路的寄生效应等原因所引起的所有误差,通过控制偏置电流的大小来实现了精确控制补偿电压值,达到对双通道采样保持电路失调误差的校准;级间缓冲器利用源极负反馈,得到与稳定输入电压电位相反的级间缓冲输出电压;采用负电荷泵技术,引入负电源,利用输入源极负反馈原理,提高电路的线性度;开关模块用于对级间缓冲输出电压保持至下级电路中,补偿由自举时钟引起的时钟馈通影响;有效解决了现有技术中采样电路的精度和线性度,与电路中存在时钟馈通和电荷注入效应的问题,实现了对电路进行失调误差校准,且消除了电路的时钟馈通效应,使电路的线性度得到提高。

- 还没有人留言评论。精彩留言会获得点赞!