一种全CMOS结构的低功耗亚阈值带隙基准电路

本发明属于集成电路芯片技术,特别涉及低静态功耗的全cmos结构带隙基准电路。

背景技术:

1、带隙基准是各种类型集成电路中的基本单元电路之一,它为其他电路模块提供一个不随温度和电源电压变化的基准电压,可广泛应用于模/数转换器、数/模转换器、动态存储器以及低压差线性稳压器等集成电路系统之中。作为系统参考电压基准,带隙基准电路的性能直接决定整体电路的稳定性,因而它是高性能集成电路中最重要的基本电路单元。随着科技进步,移动设备和可穿戴设备越来越多地融入到人们生活中,这些设备通常都对芯片的功耗方面有很高的要求,因而如何降低芯片功耗显得越来越重要。

2、基准电路的原理是通过正温度系数的电压和负温度系数的电压以一定的比例相加,得到一个与温度无关的基准电压。传统结构通过三极管的基-射电压提供负温度系数电压vbe,两个电流不同的三极管的基-射电压差δvbe提供正温度系数电压。本设计采用工作在亚阈值区的mos管的栅-源电压提供负温度系数电压,采用不同尺寸mos管的δvgs来提供正温度系数电压。

3、本文设计的带隙基准电路的设计思路是在保证较小的输出电压温漂系数的同时,最大程度减小电路功耗,最终使得该设计能适用于移动设备和可穿戴设备等低功耗应用领域。

技术实现思路

1、为了实现带隙基准电路的低功耗要求,本文提出了一种全cmos结构低功耗亚阈值带隙基准电路。

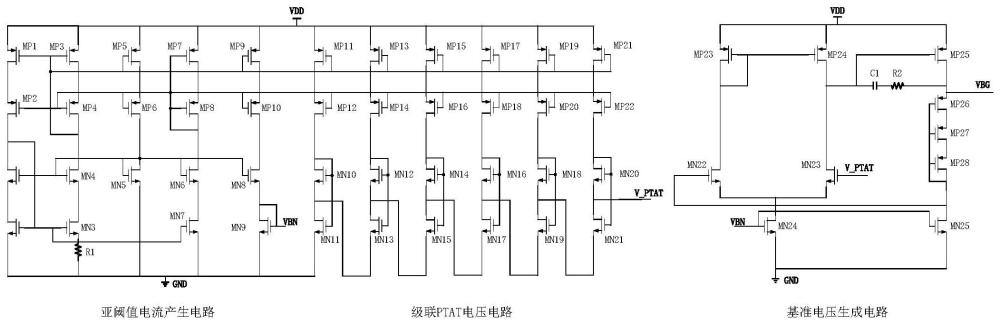

2、本发明的电路结构如图1所示。电路主要包括亚阈值电流产生电路部分、级联ptat电压电路部分和基准电压生成电路部分

3、亚阈值电流产生电路部分包括第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10、第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5、第六nmos管mn6、第七nmos管mn7、第八nmos管mn8、第九nmos管mn9、电阻r1。其中,第一pmos管mp1、第二pmos管mp2与第三pmos管mp3、第四pmos管mp4组成共源共栅电流镜,使流过第一nmos管mn1的电流与流过第三nmos管mn3的电流相等;电阻r1接在第三nmos管mn3的源极与地gnd之间,第一nmos管mn1与第三nmos管mn3的宽长比之比为1:n,在电阻r1上流过电流大小等于vgs差值电压除以电阻r1的亚阈值偏置电流;第一pmos管mp1、第二pmos管mp2与第五pmos管mp5、第六pmos管mp6、第九pmos管mp9、第十pmos管mp10组成共源共栅电流镜,第一nmos管mn1、第二nmos管mn2与第六nmos管mn6、第七nmos管mn7组成共源共栅电流镜,将生成的亚阈值电流复制到各个偏置支路;第五nmos管mn5、第七nmos管mn7、第八nmos管mn8分别为nmos共栅极和nmos共栅极提供偏置电压;第一pmos管mp1、第二pmos管mp2、第八nmos管mn8、第九nmos管mn9分别通过共源共栅电流镜用亚阈值偏置电流为级联ptat电压电路和基准电压生成电路提供电流偏置。

4、级联ptat电压电路包括第十一pmos管mp11、第十二pmos管mp12、第十三pmos管mp13、第十四pmos管mp14、第十五pmos管mp15、第十六pmos管mp16、第十七pmos管mp17、第十八pmos管mp18、第十九pmos管mp19、第二十pmos管mp20、第二十一pmos管mp21、第二十二pmos管mp22、第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15、第十六nmos管mn16、第十七nmos管mn17、第十八nmos管mn18、第十九nmos管mn19、第二十nmos管mn20、第二十一nmos管mn21。其中,第十一pmos管mp11、第十二pmos管mp12、第十三pmos管mp13、第十四pmos管mp14、第十五pmos管mp15、第十六pmos管mp16、第十七pmos管mp17、第十八pmos管mp18、第十九pmos管mp19、第二十pmos管mp20、第二十一pmos管mp21、第二十二pmos管mp22通过构成共源共栅电流源将亚阈值电流复制到各自支路,为各支路的nmos管提供偏置;第十nmos管mn10与第十一nmos管mn11串联,第十nmos管mn10的源极与第十一nmos管mn11的漏极相连接,第十nmos管mn10栅极与漏极短接并与第十一nmos管mn11的栅极相连,第十一nmos管mn11的源极接地,第十一nmos管mn11的漏极电压为ptat电压,mn11漏极接下一级的nmos管的源极进行级联,以累加得到所希望的ptat电压;第十二nmos管mn12与第十三nmos管mn13串联,第十二nmos管mn12的源极与第十三nmos管mn13的漏极相连接,第十二nmos管mn12栅极与漏极短接并与第十三nmos管mn13的栅极相连,第十三nmos管mn13的源极接前一级输出即第十一nmos管mn11的漏极,第十三nmos管mn13的漏极接下一级的nmos管的源极进行级联,以累加得到所希望的ptat电压;第十四nmos管mn14与第十五nmos管mn15串联,第十四nmos管mn14的源极与第十五nmos管mn15的漏极相连接,第十四nmos管mn14栅极与漏极短接并与第十五nmos管mn15的栅极相连,第十五nmos管mn15的源极接前一级输出即第十三nmos管mn13的漏极,第十五nmos管mn15的漏极接下一级的nmos管的源极进行级联,以累加得到所希望的ptat电压;第十六nmos管mn16与第十七nmos管mn17串联,第十六nmos管mn16的源极与第十七nmos管mn17的漏极相连接,第十六nmos管mn16栅极与漏极短接并与第十七nmos管mn17的栅极相连,第十七nmos管mn17的源极接前一级输出即第十五nmos管mn15的漏极,第十七nmos管mn17的漏极接下一级的nmos管的源极进行级联,以累加得到所希望的ptat电压;第十八nmos管mn18与第十九nmos管mn19串联,第十八nmos管mn18的源极与第十九nmos管mn19的漏极相连接,第十八nmos管mn18栅极与漏极短接并与第十九nmos管mn19的栅极相连,第十九nmos管mn19的源极接前一级输出即第十七nmos管mn17的漏极,第十九nmos管mn19的漏极接下一级的nmos管的源极进行级联,以累加得到所希望的ptat电压;第二十nmos管mn20与第二十一nmos管mn21串联,第二十nmos管mn20的源极与第二十一nmos管mn21的漏极相连接,第二十nmos管mn20栅极与漏极短接并与第二十一nmos管mn21的栅极相连,第二十一nmos管mn21的源极接前一级输出即第十九nmos管mn19的漏极,第二十一nmos管mn21的漏极即为本设计所需要的ptat电压。

5、基准电压生成电路包括第二十三pmos管mp23、第二十四pmos管mp24、第二十五pmos管mp25、第二十六pmos管mp26、第二十七pmos管mp27、第二十八pmos管mp28、第二十二nmos管mn22、第二十三nmos管mn23、第二十四nmos管mn24、第二十五nmos管mn25。其中,第二十二nmos管mn22、第二十三nmos管mn23、第二十三pmos管mp23、第二十四pmos管mp24、第二十四nmos管mn24构成差分输入单端输出的五管放大器,为运放第一级,第二十三nmos管mn23的栅极与级联ptat电压电路的输出端相连,由运放作用,使得第二十二nmos管mn22的栅极电压也为产生的ptat电压;第二十五pmos管mp25、第二十五nmos管mn25构成运放第二级,第二十五pmos管mp25为输出管,提高电路的带载能力;第二十六pmos管mp26、第二十七pmos管mp27、第二十八pmos管mp28提供负温电压vgs,与ptat电压相加,得到输出的带隙电压vbg;c1为密勒补偿电容,r2为调零电阻,c1与r2串联在五管放大器输出端与整个电路输出端之间,保证环路稳定性。

- 还没有人留言评论。精彩留言会获得点赞!