低压差线性稳压电路的制作方法

本发明涉及电路,尤其涉及一种低压差线性稳压电路。

背景技术:

1、低压差线性稳压电路简称ldo,现有的ldo已经能够实现超低功耗、低成本设计。为了实现高电源电压抑制比,现有技术多采用三种方法:

2、方法一、将参考电流加载到两个二极管接法的nmos管上,产生的参考电压为2vth;其优点是电路结构简单、消耗面积小;其缺点是,两个阈值叠加使得参考电压受工艺角及温度影响极大。

3、方法二、将参考电流加载到电阻上,得到参考电压;其优点是,参考电压受温度及工艺角影响甚微;其缺点是,在10na小电流情况下,实现0.72v需要72m得电阻,面积非常大。

4、方法三、参考电压采用饱和接法的nmos管,采用反馈支路,支路用电阻设计;其优点是,输出电压受nmos阈值变化而变化,输出电压随温度变化为1个vth,输出通过反馈支路的电阻比例提升至所需电压;其缺点是,对于低功耗要求,na级的电流,需要m级别的电阻,面积较大。

技术实现思路

1、本发明提供了一种低压差线性稳压电路,以在提升电源电压抑制比的同时,解决现有技术存在的技术问题。

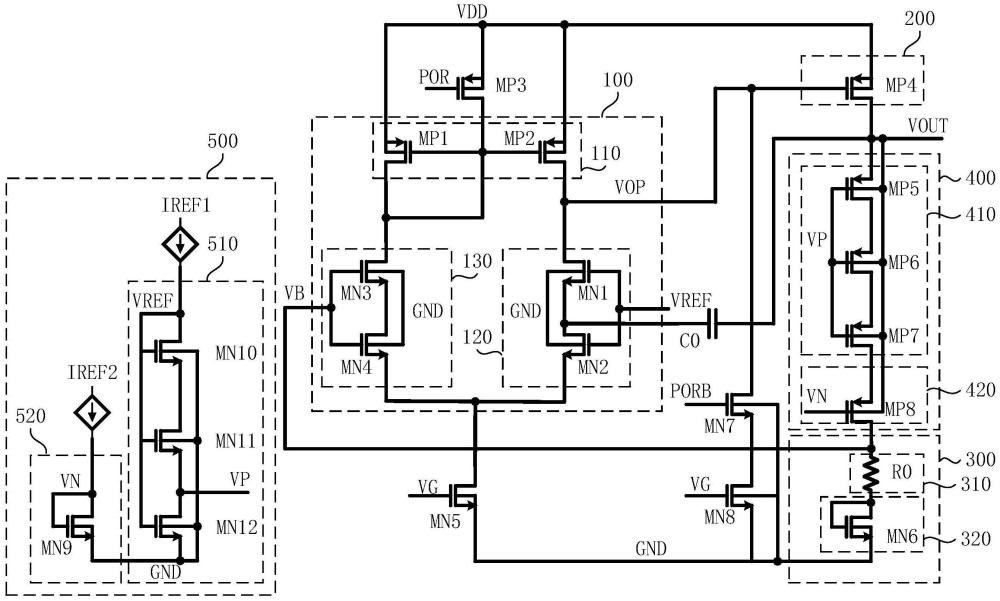

2、该低压差线性稳压电路包括:

3、误差放大模块,所述误差放大模块包括电流镜、第一对管和第二对管;所述电流镜的第一输入端和第二输入端均接入第一电源电压;所述电流镜的第一输出端与所述第一对管的输入端电连接,所述第一对管的输出端接入第二电源电压,所述第一对管的控制端接入参考电压;所述电流镜的第二输出端与所述第二对管的输入端电连接,所述第二对管的输出端接入所述第二电源电压,所述第二对管的控制端的电压为所述参考电压的等效电压;

4、输出模块,所述输出模块的控制端与所述电流镜的第一输出端电连接,所述输出模块的输入端接入所述第一电源电压,所述输出模块的输出端作为所述低压差线性稳压电路的输出端;

5、反馈模块,所述反馈模块包括电阻单元和消除工艺偏差单元,所述电阻单元的第一端与所述第二对管的控制端电连接,所述电阻单元的第二端与所述消除工艺偏差单元的第二端电连接,所述消除工艺偏差单元的第一端接入所述第二电源电压;

6、温度特性调整模块,所述温度特性调整模块包括第一调整单元和第二调整单元,所述第一调整单元的控制端接入第一调整电压,所述第一调整单元的输入端与所述输出模块的输出端电连接,所述第一调整单元的输出端与所述第二调整单元的输入端电连接;所述第二调整单元的控制端接入第二调整电压,所述第二调整单元的输出端与所述电阻单元的第一端电连接;

7、参考电压产生模块,所述参考电压产生模块包括第一电流源、第二电流源、第一电压产生单元和第二电压产生单元;所述第一电流源的输出端与所述第一电压产生单元的第一端电连接,所述第一电压产生单元的第二端接入所述第二电源电压,所述第一电压产生单元用于产生所述参考电压和所述第一调整电压;所述第二电流源的输出端与所述第二电压产生单元的第一端电连接,所述第二电压产生单元的第二端接入所述第二电源电压,所述第二电压产生单元用于产生所述第二调整电压。

8、可选地,所述电流镜包括:

9、第一p型晶体管,所述第一p型晶体管源极接入所述第一电源电压,所述第一p型晶体管的漏极与所述第二对管的输入端电连接,所述第一p型晶体管的漏极与所述第一p型晶体管的栅极电连接;所述第一p型晶体管的衬底和源极电连接;

10、第二p型晶体管,所述第二p型晶体管的源极接入所述第一电源电压,所述第二p型晶体管的漏极与所述第一对管的输入端电连接;所述第二p型晶体管的栅极和所述第一p型晶体管的栅极均接入所述第一电源电压;所述第二p型晶体管的衬底和源极电连接。

11、可选地,低压差线性稳压电路还包括:

12、第三p型晶体管,所述第三p型晶体管的栅极接入第一复位电压,所述第三p型晶体管串联于所述电流镜的控制端和所述第一电源电压之间,所述第三p型晶体管的衬底和源极电连接。

13、可选地,所述第一对管包括:第一n型晶体管和第二n型晶体管;

14、所述第一n型晶体管的栅极和所述第二n型晶体管的栅极均接入所述参考电压,所述第一n型晶体管的漏极与所述电流镜的第一输出端电连接,所述第一n型晶体管的源极与所述第二n型晶体管的漏极电连接,所述第二n型晶体管的源极与所述第二电源电压电连接;所述第一n型晶体管的衬底和所述第二n型晶体管的衬底均接地;

15、和/或,所述第二对管包括:第三n型晶体管和第四n型晶体管;

16、所述第三n型晶体管的栅极和所述第四n型晶体管的栅极均与所述电阻单元的第一端电连接,所述第三n型晶体管的漏极与所述电流镜的第二输出端电连接,所述第三n型晶体管的源极与所述第四n型晶体管的漏极电连接,所述第四n型晶体管的源极与所述第二电源电压电连接,所述第三n型晶体管的衬底和所述第四n型晶体管的衬底均接地。

17、可选地,低压差线性稳压电路还包括:

18、第五n型晶体管,所述第五n型晶体管的栅极接入输出控制电压,所述第五n型晶体管串联于所述第二n型晶体管的源极和所述第二电源电压之间,且所述第五n型晶体管串联于所述第四n型晶体管的源极和所述第二电源电压之间,所述第五n型晶体管的衬底与源极电连接。

19、可选地,所述电阻单元包括:第一电阻,所述第一电阻的第一端与所述第二对管的控制端电连接;

20、所述消除工艺偏差单元包括:第六n型晶体管,所述第六n型晶体管的栅极与漏极电连接,所述第六n型晶体管的漏极与所述第一电阻的第二端电连接,所述第六n型晶体管的源极接入所述第二电源电压,所述第六n型晶体管的衬底和源极电连接。

21、可选地,低压差线性稳压电路还包括:

22、第七n型晶体管,所述第七n型晶体管的栅极接入第二复位电压,所述第二复位电压与所述第一复位电压相反,所述第七n型晶体管的漏极与输出模块的控制端电连接,所述第七n型晶体管的漏极作为所述低压差线性稳压电路的输出端;

23、第八n型晶体管,所述第八n型晶体管的栅极接入输出控制电压,所述第八n型晶体管的漏极与所述第七n型晶体管的源极电连接,所述第八n型晶体管的源极接入所述第二电源电压,所述第七n型晶体管的衬底和所述第八n型晶体管的衬底接入所述第二电源电压。

24、可选地,所述输出模块包括:

25、第四p型晶体管,所述第四p型晶体管的栅极与所述电流镜的第一输出端电连接,所述第四p型晶体管的源极接入所述第一电源电压,所述第四p型晶体管的漏极作为所述低压差线性稳压电路的输出端;所述第四p型晶体管的衬底和源极电连接。

26、可选地,所述第一调整单元包括:串联连接的至少一个p型晶体管,所述至少一个p型晶体管的栅极均接入所述第一调整电压,所述至少一个p型晶体管的衬底均与所述低压差线性稳压电路的输出端电连接;

27、和/或,所述第二调整单元包括:串联连接的至少一个p型晶体管,所述至少一个p型晶体管的栅极均接入所述第二调整电压,所述至少一个p型晶体管的衬底均与所述低压差线性稳压电路的输出端电连接。

28、可选地,所述第二电压产生单元包括:第九n型晶体管,所述第九n型晶体管的漏极和所述第二电流源的输出端电连接,所述第九n型晶体管的栅极和漏极晶体管,所述第九n型晶体管的源极接入所述第二电源电压,所述第九n型晶体管的衬底和源极电连接;所述第九n型晶体管的漏极输出所述第二调整电压;

29、和/或,所述第一电压产生单元包括:第十n型晶体管、第十一n型晶体管和第十二n型晶体管,所述第十n型晶体管、所述第十一n型晶体管和所述第十二n型晶体管的栅极均与所述第一电流源的输出端电连接,所述第十n型晶体管的漏极与所述第一电流源的输出端电连接,所述第十n型晶体管的源极与所述第十一n型晶体管的漏极电连接,所述第十一n型晶体管的源极与所述第十二n型晶体管的漏极电连接,所述第十二n型晶体管的源极接地;所述第十n型晶体管、所述第十一n型晶体管和所述第十二n型晶体管的衬底均接入所述第二电源电压;

30、其中,所述第十n型晶体管的源极或者所述第十一n型晶体管的源极输出所述第一调整电压。

31、本发明实施例设置低压差线性稳压电路包括误差放大模块、输出模块、反馈模块、温度特性调整模块和参考电压产生模块。其中,通过增设反馈模块,在反馈模块中会增加少量功耗,但反馈模块的设置使得参考电压的工艺偏差得以消除,使得输出电压受工艺的偏差的影响更小。本发明实施例通过增加少量功耗来换取更高的电源电压抑制比,可以适用于更复杂的应用环境。同时本发明实施例采用温度特性调整模块,实现随电压可变的电阻,获得温度特性可调节的输出电压,可以根据需求输出正温度系数电压,零温度系数电压以及负温度系数电压。综上所述,本发明实施例解决了低功耗要求下的高电源电压抑制比的需求,同时兼顾输出电压的温度特性可调功能。

32、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!