电压偏置电路、芯片及其移动终端的制作方法

本技术与移动通信相关,特别是与移动通信相关之电压偏置电路、芯片及其移动终端。

背景技术:

1、基准电源在通信设备中用于为通信设备提供一个精确的基准参考点,具有至关重要的作用。基准电源所需解决的主要问题是提高其温度抑制与电源抑制,即如何实现与温度有确定关系且与电源基本无关的结构。由于在半导体中几乎没有与温度无关的参数,因此需要寻找具有正温度系数和负温度系数的参数,通过合适的组合,以得到与温度无关的量,且这些参数与电源无关。

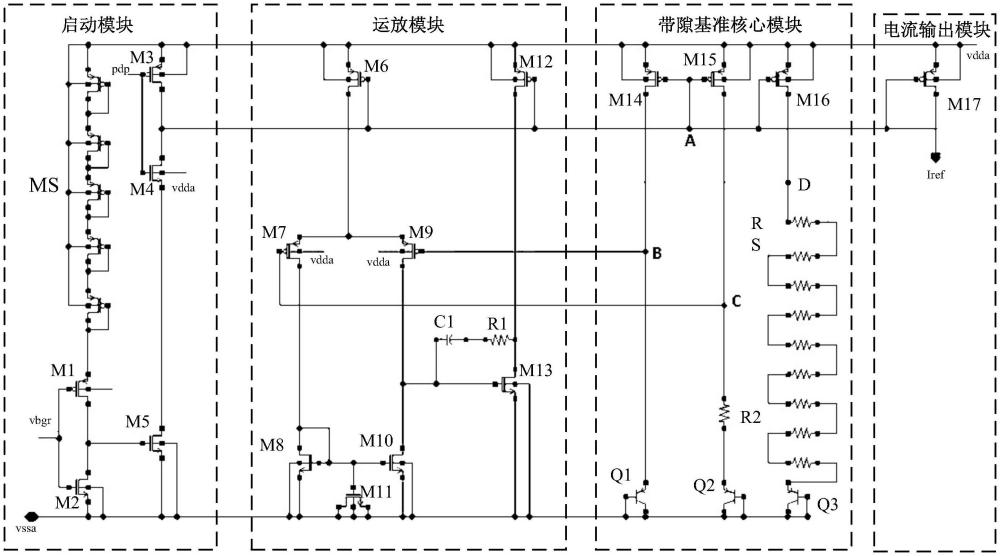

2、电压偏置电路是利用一个具有正温度系数的电压与具有负温度系数的电压之和,二者温度系数相互抵消,实现与温度无关的电压基准。图1为现有电压偏置电路的结构示意图,其功能是产生一个稳定的电压输出从而为系统提供直流参考电压。该电路利用q1的栅极-发射极电压(vbe1)来产生负温度系数电压,两个npn三极管q1和q2的栅极-发射极电压的差值(δvbe)来产生正温度系数电压,并以合适的权重相加,最终获得具有零温度系数的基准电压。其中,三极管q1和q2并联个数比为1:n,其中n为自然数,电阻r1和r2的阻值比为1:1,带隙基准单元输出电压vref为:选取合适的r3和r1,就可以得到一个零温系数的基准电压。

3、随着通信技术的飞速发展,对电压偏置电路也提出了越来越高的要求,不但希望能获得稳定的参考电压,同时希望电压偏置电路具有温度补偿功能,例如,在低温下具有相对的高压,在高温下具有相对的低压,即一种具有温度系数,特别是具有负温度系数的电压或者电流基准。从而改善通信质量,使得移动设备的适应性更强。遗憾的是,现有的电压偏置电路只能实现不可调的单一输出,已不能满足现代通信技术之要求。

技术实现思路

1、针对现有技术的缺陷,本实用新型提供了一种电压偏置电路、芯片及其移动终端。

2、一种电压偏置电路,包括逻辑控制单元、带隙基准单元和输出单元,所述逻辑控制单元和带隙基准单元分别与输出单元相连,其中,所述带隙基准单元,用于产生多个不同温度系数的基准电压;所述逻辑控制单元,用于控制输出单元的输出;所述输出单元,用于根据所述逻辑控制单元的控制输出选定的温度系数的基准电压。

3、进一步的,所述带隙基准单元,包括依次连接的启动模块、运放模块和带隙基准核心模块,其中,所述启动模块,用于在启动时输出启动信号使得所述带隙基准核心模块脱离零兼并点;所述运放模块,利用栅极-发射极电压的差值产生基础电压;所述带隙基准核心模块,通过分压网络对所述基础电压进行分压,从而生成所述多个不同温度系数的基准电压。

4、进一步的,所述带隙基准单元中还具有电源纹波抑制比(psrr)模块,所述电源纹波抑制比模块分别与所述启动模块、运放模块和带隙基准核心模块相连,用于为各模块提供稳定的工作电源。

5、进一步的,所述启动模块包括pmos管m1、pmos管m3和nmos管m2、nmos管m4、nmos管m5,其中pmos管m1的栅极与nmos管m2的栅极相连后与基准电压vbgr相连,pmos管m1的漏极与nmos管m2的漏极连接后与nmos管m5的栅极相连,pmos管m1的源极通过多个串联连接的nmos管与电源vdda相连,nmos管m2的源极接地,pmos管m3的栅极与nmos管m4的栅极连接后与正使能控制信号pdp相连,pmos管m3的源极与电源vdda相连,pmos管m3的漏极与nmos管m4的漏极相连,nmos管m4的源极与nmos管m5的漏极连接,nmos管m5的源极接地,pmos管m3和nmos管m4的漏极连接点作为启动模块的输出端与带隙基准核心模块相连。

6、进一步的,所述运放模块包括pmos管m6、pmos管m7、pmos管m9、pmos管m12和nmos管m8、nmos管m10、nmos管m11、nmos管m13,其中pmos管m6的栅极与pmos管m12的栅极连接后再与pmos管m3的漏极相连,pmos管m6与pmos管m12的源极均同电源vdda相连,pmos管m7与pmos管m9的源极连接后与pmos管m6漏极相连,pmos管m7的栅极与pmos管m9的栅极分别同带隙基准核心模块相连,其中pmos管m9的栅极与带隙基准核心模块中pnp晶体管q1的发射极相连,pmos管m7的栅极与带隙基准核心模块中pnp晶体管q2的发射极相连,pmos管m7的漏极与nmos管m8的漏极相连,pmos管m9的漏极与nmos管m10的漏极相连,nmos管m8的栅极与nmos管m10的栅极同nmos管m11的栅极相连,nmos管m8的源极与nmos管m10的源极均接地,pmos管m12的漏极与nmos管m13的漏极连接,nmos管m13的栅极与pmos管m9的漏极连接,nmos管m13的源极接地,在nmos管m13的栅极与漏极之间串联连接有电阻r1与电容c1。

7、进一步的,所述带隙基准核心模块包括pmos管m14、pmos管m15、pmos管m16和pnp晶体管q1、pnp晶体管q2、pnp晶体管q3,pmos管m14、pmos管m15以及pmos管m16的栅极连接在一起,pmos管m14、pmos管m15以及pmos管m16的源极均同电源vdda相连,pmos管m14的漏极与pnp晶体管q1的发射极相连,pnp晶体管q1的基极与集电极接地;pmos管m15的漏极与电阻r2的一端相连,电阻r2的另一端与pnp晶体管q2的发射极连接,pnp晶体管q2的基极与集电极接地;pmos管m16的漏极与电阻分压网络rs的一端相连,分压网络rs的另一端与pnp晶体管q3的发射极连接,pnp晶体管q3的基极与pnp晶体管q3集电极接地;pmos管m14的栅极、pmos管m15的栅极以及pmos管m16的栅极与输出模块相连。

8、进一步的,所述分压网络rs由多个电阻串联而成,在每个串联的所述电阻的一端能获得一个不同电压值的所述温度系数的基准电压。

9、进一步的,还包括电流输出模块,其与所述带隙基准核心模块连接,所述电流输出模块包括pmos晶体管m17,pmos晶体管m17的栅极和pmos晶体管的漏极连接在一起,并连接到pmos晶体管m14、pmos晶体管m15和pmos晶体管m16栅极的共同连接处以输出基准电流信号。

10、进一步的,所述电源纹波抑制比模块包括pmos管m30、pmos管m31、pmos管m32、pmos管m33和nmos管m34、nmos管m35,pmos管m30的栅极与pmos管m31的栅极相连,pmos管m30和pmos管m32的源极均与电源vdda相连,pmos管m31的栅极连接到pmos管m31的漏极处,pmos管m31的漏极与nmos管m35的漏极相连,nmos管m35的源极接地,pmos管m30的漏极与pmos管m32的源极以及pmos管m33的源极相连,pmos管m33的漏极接地,pmos管m33的栅极与pmos管m12的漏极相连,pmos管m32的漏极通过nmos管m34接地,nmos管m34的源极和栅极连接在一起,nmos管m34的源极接地,nmos管m35的栅极与nmos管m34的栅极连接在一起。

11、进一步的,所述逻辑控制单元包括依次连接的逻辑阵列和与非门阵列,其中,所述逻辑阵列与控制信号输入端相连,用于根据所述控制信号产生相应的逻辑输出;所述与非门阵列,用于根据所述逻辑输出产生一对互补信号。

12、进一步的,所述输出单元,用于根据所述互补信号来输出选定的温度系数的基准电压。

13、进一步的,所述逻辑阵列包括多条结构相同的信号通路,所述信号通路由相互串联连接在一起的两个反相器组成。

14、进一步的,所述输出单元包括多个并联连接的输出门,所述输出门的输入端与温度补偿电压相连,所述输出门的输出端并联连接在一起,所述输出门的控制端连接所述与非门阵列,通过互补的控制信号控制相应的输出门通断。

15、一种芯片,包括所述的电压偏置电路。

16、一种移动终端,包括所述的电压偏置电路。

17、本实用新型的有益效果是:本实用新型提供了一种电压偏置电路,包括逻辑控制单元、带隙基准单元和输出单元,所述逻辑控制单元分别与带隙基准单元和输出单元相连,所述带隙基准单元和输出单元相连,其中,所述带隙基准单元,用于产生多个不同电压值的温度系数的基准电压;所述逻辑控制单元,用于选定多个所述不同电压值的温度系数的基准电压中的一个;所述输出单元,用于输出所述选定的基准电压。通过本实用新型的电压偏置电路可以得到了输出可调的偏置电压,其具有温度系数和温度补偿功能。

- 还没有人留言评论。精彩留言会获得点赞!