一种低温漂电压型带隙基准及高灵敏度负温电压生成电路的制作方法

本发明涉及带隙基准源领域,具体涉及一种低温漂电压型带隙基准及高灵敏度负温电压生成电路。

背景技术:

1、带隙基准源,简称带隙,是一种提供基准电压或基准电流的电路,广泛应用于高精度的比较器、数据转换器及其他模拟集成电路中。带隙基准源的核心思想在于通过电路设计来补偿温度带来的变化。它利用具有正温度系数的电压与具有负温度系数的电压之和,通过合理配置这两种电压,使得它们的温度系数相互抵消,从而实现与温度无关的电压基准。这种优异的温度稳定性使得带隙基准源成为高精度电压参考的理想选择。

2、带隙基准源可以分为双极型带隙基准源和cmos带隙基准源。这两种类型的带隙基准源在工艺条件上都具有较宽的适应性,输出电压受温度和电源电压影响小,并且精度高。其中,cmos型带隙基准源的适用性好且功耗较低,得到广泛的使用。但是,传统的一阶补偿后电压型cmos带隙基准源仍具有较高的温度系数,难以满足对温度变化敏感的高精度芯片的应用需求。

技术实现思路

1、本发明的目的在于提供一种低温漂电压型带隙基准及高灵敏度负温电压生成电路,旨在改善传统的一阶补偿后电压型cmos带隙基准源仍具有较高的温度系数,难以满足对温度变化敏感的高精度芯片的应用需求的问题。

2、为实现上述目的,本发明采用以下技术方案:

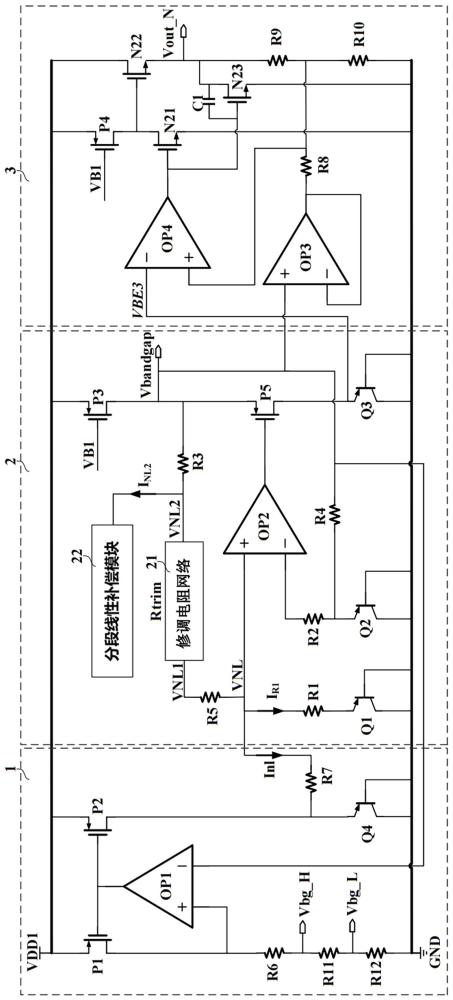

3、一种低温漂电压型带隙基准及高灵敏度负温电压生成电路,包括曲率补偿模块、带隙基准核心模块、高灵敏度ntc电压模块;

4、所述曲率补偿模块、带隙基准核心模块、高灵敏度ntc电压模块的电源输入端均与外部电源vdd1电性连接;

5、所述带隙基准核心模块包括正温度系数电压项产生支路和负温度系数电压项产生支路,所述曲率补偿模块的输出端与正温度系数电压项产生支路和负温度系数电压项产生支路的输入端电性连接,所述正温度系数电压项产生支路和负温度系数电压项产生支路的输出端相连,并输出低温漂带隙电压vbandgap;

6、所述带隙基准核心模块输出低温漂带隙电压vbandgap至曲率补偿模块;

7、所述带隙基准核心模块输出低温漂带隙电压vbandgap和vbe3电压至高灵敏度ntc电压模块,所述高灵敏度ntc电压模块输出负温度电压vout_n。

8、进一步的,所述正温度系数电压项产生支路包括修调电阻网络、分段线性补偿模块、mos管p3和电阻r3、电阻r5;

9、所述负温度系数电压项产生支路包括运算放大器op2、mos管p5、三极管q1、三极管q2、三极管q3和电阻r1、电阻r2、电阻r4;

10、mos管p3的源极与外部电源vdd1电性连接;所述分段线性补偿模块输出偏置电压vb1至mos管p3的栅极;

11、所述曲率补偿模块的输出端与电阻r1的一端、电阻r5的一端和运算放大器op2的同向输入端电性连接,所述电阻r1的另一端与三极管q1的发射极电性连接;所述运算放大器op2的反向输入端与电阻r2的一端电性连接,所述电阻r2的另一端与电阻r4的一端和三极管q2的发射极电性连接;所述运算放大器op2的输出端与mos管p5的栅极电性连接,所述mos管p5的漏极与三极管q3的发射极电性连接,并输出vbe3电压至高灵敏度ntc电压模块;

12、所述电阻r5的另一端与修调电阻网络的vnl1端口电性连接,所述修调电阻网络的vnl2端口与分段线性补偿模块和电阻r3的一端电性连接,所述电阻r3的另一端与mos管p3的漏极、mos管p5的源极、电阻r4的另一端电性连接,并作为输出端输出低温漂带隙电压vbandgap至高灵敏度ntc电压模块和曲率补偿模块;

13、所述三极管q1、三极管q2、三极管q3的集电极和基极均接地。

14、进一步的,所述曲率补偿模块包括运算放大器op1、mos管p1、mos管p2、三极管q4和电阻r6、电阻r7、电阻r11、电阻r12;

15、所述mos管p1的源极和mos管p2的源极均与外部电源vdd1电性连接;

16、所述带隙基准核心模块输出低温漂带隙电压vbandgap至运算放大器op1的反向输入端;所述mos管p1的漏极与运算放大器op1的同向输入端电性连接,所述mos管p1的栅极与mos管p2的栅极和运算放大器op1的输出端电性连接;所述电阻r6、电阻r11和电阻r12依次串联在mos管p1的漏极和地之间;

17、所述mos管p2的漏极与电阻r7的一端和三极管q4的发射极电性连接,所述电阻r7的另一端作为输出端与正温度系数电压项产生支路和负温度系数电压项产生支路的输入端电性连接;

18、所述三极管q4的基极和集电极均接地。

19、进一步的,所述高灵敏度ntc电压模块包括运算放大器op3、运算放大器op4、mos管p4、mos管n21、mos管n22、mos管n23、电容c1和电阻r8、电阻r9、电阻r10;

20、所述mos管p4的源极和mos管n22的漏极均与外部电源vdd1电性连接;所述分段线性补偿模块输出偏置电压vb1至mos管p4的栅极;

21、所述带隙基准核心模块输出低温漂带隙电压vbandgap至运算放大器op3的同向输入端,所述运算放大器op3的反相输入端和输出端均与电阻r8的一端电性连接;所述电阻r8的另一端与电阻r9的一端、电阻r10的一端和运算放大器op4的同向输入端电性连接,所述带隙基准核心模块输出vbe3电压至运算放大器op4的反向输入端,所述运算放大器op4的输出端与mos管n21的栅极、mos管n23的栅极和电容c1的一端电性连接;所述mos管n21的漏极与mos管p4的漏极和mos管n22的栅极电性连接,所述mos管n22的源极与电容c1的另一端、mos管n23的漏极和电阻r9的另一端电性连接,并作为输出端输出负温度电压vout_n;

22、所述mos管n21的源极、mos管n23的源极和电阻r10的另一端接地。

23、进一步的,所述分段线性补偿模块包括启动单元、偏置及ipata生成单元、ictat生成单元和分段线性补偿单元;

24、所述启动单元、偏置及ipata生成单元、ictat生成单元和分段线性补偿单元的电源输入端均与外部电源vdd1电性连接;

25、所述启动单元的输出端与偏置及ipata生成单元的信号输入端电性连接,所述偏置及ipata生成单元的输出端输出偏置电压vb1至mos管p3的栅极,并输出偏置电压vb1和电流ipata至分段线性补偿单元的第一输入端;所述ictat生成单元输出电流ictat至分段线性补偿单元的第二输入端,所述分段线性补偿单元的输出端与修调电阻网络的vnl2端口电性连接;

26、所述电流ipata为与绝对温度呈正比特性的电流,所述电流ictat为与绝对温度互补特性的电流。

27、进一步的,所述启动单元包括mos管p6、mos管p18、mos管n1和mos管n2;

28、所述mos管p18的源极与外部电源vdd1电性连接;

29、所述mos管p18的漏极与mos管p6的源极电性连接,所述mos管p18的栅极与mos管p6的栅极、mos管n1的栅极电性连接,并作为第一输出端与偏置及ipata生成单元的信号输入端电性连接;

30、所述mos管p6的漏极与mos管n1的漏极和mos管n2的栅极电性连接,所述mos管n2的漏极作为第二输出端与偏置及ipata生成单元的信号输入端电性连接;

31、所述mos管n1的源极和mos管n2的源极均接地。

32、进一步的,所述偏置及ipata生成单元包括mos管p7、mos管p8、mos管n3、mos管n4和电阻r14;

33、所述mos管p7的源极和mos管p8的源极均与外部电源vdd1电性连接;

34、所述启动单元的第一输出端与mos管n3的栅极、mos管p7的漏极和电阻r14的一端电性连接,所述电阻r14的另一端与mos管n3的漏极和mos管n4的栅极电性连接,所述启动单元的第二输出端与mos管p7的栅极、mos管p8的栅极、漏极和mos管n4的漏极电性连接,所述mos管p7的栅极作为输出端输出偏置电压vb1至mos管p3的栅极,并输出偏置电压vb1和电流ipata至分段线性补偿单元的第一输入端;

35、所述mos管n3的源极和mos管n4的源极均接地。

36、进一步的,所述ictat生成单元包括运算放大器op5、mos管p16、mos管p17、三极管q5和电阻r13;

37、所述mos管p16的源极和mos管p17的源极均与外部电源vdd1电性连接;

38、所述mos管p16的栅极与mos管p17的栅极和运算放大器op5的输出端电性连接,并输出电流ictat至分段线性补偿单元的第二输入端;所述mos管p16的漏极与电阻r13的一端和运算放大器op5的同向输入端电性连接,所述mos管p17的漏极与三极管q5的发射极和运算放大器op5的反向输入端电性连接;

39、所述三极管q5的集电极和基极以及电阻r13的另一端均接地。

40、进一步的,所述分段线性补偿单元包括mos管p9、mos管p10、mos管p11、mos管p12、mos管p13、mos管p14、mos管p15、mos管n5、mos管n6、mos管n7、mos管n8、mos管n9、mos管n10、mos管n11、mos管n12、mos管n13、mos管n14和mos管n15;

41、所述mos管p9的源极、mos管p10的源极、mos管p11的源极、mos管p12的源极、mos管p13的源极、mos管p14的源极和mos管p15的源极均与外部电源vdd1电性连接;

42、所述mos管p9的栅极与mos管p10的栅极、漏极、mos管n6的漏极、mos管p13的栅极、漏极、mos管n11的栅极、mos管n12的栅极、漏极和mos管n13的漏极电性连接;所述mos管p9的漏极与mos管n5的漏极、栅极和mos管n8的栅极电性连接;

43、所述偏置及ipata生成单元输出偏置电压vb1和电流ipata至mos管p11的栅极,所述mos管p11的漏极与mos管n7的栅极、漏极和mos管n6的栅极电性连接;

44、所述mos管p12的栅极与mos管p15的栅极、漏极和mos管n15的漏极电性连接,所述mos管p12的漏极与mos管n8的漏极、mos管n9的栅极、漏极和mos管n10的栅极电性连接;

45、所述ictat生成单元输出电流ictat至mos管p14的栅极,所述mos管p14的漏极与mos管n14的栅极、漏极、mos管n13的栅极和mos管n15的栅极电性连接;

46、所述mos管n11的漏极与mos管n10的漏极电性连接,并作为输出端与修调电阻网络的vnl2端口电性连接;

47、所述mos管n5的源极、mos管n6的源极、mos管n7的源极、mos管n8的源极、mos管n9的源极、mos管n10的源极、mos管n11的源极、mos管n12的源极、mos管n13的源极、mos管n14的源极和mos管n15的源极均接地。

48、采用上述技术方案后,本发明与背景技术相比,具有如下优点:

49、带隙基准核心模块采用电压型cmos带隙基准结构,正温度系数电压项产生支路产生δvbe,负温度系数电压项产生支路产生vbe,两者互补生成低温漂带隙电压vbandgap;同时曲率补偿模块进一步抵消负温度系数电压项vbe中的高阶项带来的影响,获得低温漂带隙基准。并且通过低温漂带隙电压vbandgap和vbe3电压和高灵敏度ntc电压模块输出特定温度斜率的负温特性电压vout_n。

- 还没有人留言评论。精彩留言会获得点赞!