一种电源管理装置、电子设备及可移动平台组件的制作方法

[0001]

本申请涉及电子技术领域,尤其涉及一种电源管理装置、电子设备及可移动平台组件。

背景技术:

[0002]

电子设备的处理器(例如应用处理器(application processor,ap))一般有相应配套的电源管理芯片(power management ic,pmic),pmic提供了处理器系统工作所需的各个电源以及上电时序。如图1所示,电子设备产品上电开机需要有个外部触发信号,这个外部触发信号一般接到pmic的专用管脚(例如上电触发onkey管脚),pmic检测到这个信号后,开启内部上电逻辑,完成处理器系统的各路电源(电源1、电源2、电源3、

……

、电源n)开启。如图1所示,目前的外部触发信号大多是通过按下按键实现的,然而,在有些应用场景下,由于产品需求原因,按键是不适用的,无法使用按键进行开机。

技术实现要素:

[0003]

本申请实施例公开了一种电源管理装置、电子设备及可移动平台组件,可以在系统电源供电后自动生成上电控制信号以完成处理器系统的上电,从而有效解决不使用按键开机的场景中处理器系统的正常上电问题。

[0004]

第一方面,本申请实施例提供了一种电源管理装置,应用于电子设备,所述电子设备包括系统电源以及处理器,所述电源管理装置包括上电控制电路和电源管理芯片,其中:

[0005]

所述上电控制电路连接所述系统电源和所述电源管理芯片,所述电源管理芯片连接所述处理器;

[0006]

所述上电控制电路,用于在所述系统电源供电后产生一上电控制信号,并将所述上电控制信号输入所述电源管理芯片,所述上电控制信号用于触发所述电源管理芯片对所述处理器上电。

[0007]

第二方面,本申请实施例还提供一种电子设备,包括:系统电源;处理器;以及上述第一方面所述的电源管理装置,所述电源管理装置用于在所述系统电源供电后对所述处理器上电。

[0008]

第三方面,本申请实施例还提供了一种可移动平台组件,包括:可移动平台;遥控终端,用于控制所述可移动平台;

[0009]

其中,所述遥控终端包括:系统电源;处理器;以及上述第一方面所述的电源管理装置,所述电源管理装置用于在所述系统电源供电后对所述处理器上电。

[0010]

本申请实施例提供的电源管理装置可应用于电子设备,该电子设备包括系统电源以及处理器,该电源管理装置包括上电控制电路和电源管理芯片,其中,上电控制电路连接系统电源和电源管理芯片,电源管理芯片连接处理器,上电控制电路,用于在系统电源供电后产生一上电控制信号,并将上电控制信号输入电源管理芯片,以触发电源管理芯片对处理器上电,可以在系统电源供电后自动生成上电控制信号以完成处理器系统的上电,从而

有效解决不使用按键开机的场景中处理器系统的正常上电问题。

附图说明

[0011]

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

[0012]

图1是现有技术提供的一种电源管理方案的电路结构示意图;

[0013]

图2是本申请实施例提供的一种电源管理装置的电路结构示意图;

[0014]

图3是本申请实施例提供的一种上电控制电路的电路结构示意图;

[0015]

图4是本申请实施例提供的另一种上电控制电路的电路结构示意图;

[0016]

图5是本申请实施例提供的又一种上电控制电路的电路结构示意图;

[0017]

图6是本申请实施例提供的另一种电源管理装置的电路结构示意图;

[0018]

图7是本申请实施例提供的一种上电控制电路中电容的端电压的变化示意图;

[0019]

图8是本申请实施例提供的一种电源管理芯片的开机电源时序图;

[0020]

图9是本申请实施例提供的一种上电控制电路产生的上电控制信号的波形示意图;

[0021]

图10是本申请实施例提供的又一种电源管理装置的电路结构示意图;

[0022]

图11是本申请实施例提供的一种电子设备的电路结构示意图;

[0023]

图12是本申请实施例提供的一种可移动平台组件的电路结构示意图。

具体实施方式

[0024]

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行描述。

[0025]

本申请实施例中的电子设备具体可以是用于对无人机等可移动平台进行控制的遥控终端。遥控终端例如可以是遥控器,遥控器的其中一个功能模块包括核心板,核心板上用到了手机等移动领域的应用处理器ap,该应用处理器对应有相配套的电源管理芯片pmic。当遥控器上的一按键触发开机,待各功能模块上电完成后,可以通过遥控器的另一按键对该应用处理器执行上电流程。然而,在这样的使用场景中,想要用户准确判断各功能模块上电完成,然后再通过按键手动触发以及时产生该应用处理器所需的上电触发信号显然是无法做到的。可见,通过按下按键的方式对该应用处理器进行上电是不适用的,亟需提供一种能够自动产生上电触发信号的电路设计方案。

[0026]

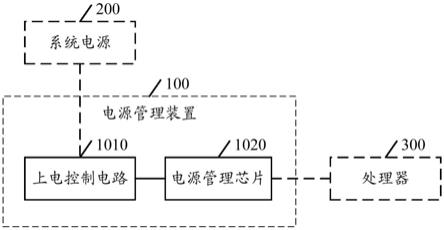

请参阅图2,为本申请实施例提供的一种电源管理装置的电路结构示意图。所述电源管理装置100应用于电子设备,所述电子设备包括系统电源200以及处理器300,所述电源管理装置100包括上电控制电路1010和电源管理芯片1020,其中:

[0027]

上电控制电路1010连接系统电源200和电源管理芯片1020,电源管理芯片1020连接处理器300;

[0028]

上电控制电路1010,用于在系统电源200供电后产生一上电控制信号,并将该上电控制信号输入电源管理芯片1020,该上电控制信号用于触发电源管理芯片1020对处理器300上电。

[0029]

其中,上电控制信号包括从低电平到高电平的脉冲信号。

[0030]

可选的,根据电源管理芯片1020的类型不同以及对上电控制信号的要求,上电控制信号也可以包括从高电平到低电平的脉冲信号,本申请实施例不做限定。

[0031]

可见,本申请实施例提供的电源管理装置包括有上电控制电路和电源管理芯片,上电控制电路能够在电子设备的系统电源供电后自动产生一上电控制信号,并将该上电控制信号输入电源管理芯片,电源管理芯片在该上电控制信号满足触发条件后对处理器上电,可以在系统电源供电后自动生成上电控制信号以完成处理器系统的上电,从而有效解决不使用按键开机的场景中处理器系统的正常上电问题。

[0032]

可选的,上电控制电路1010具体可以通过两个电阻电容rc充放电电路来实现。其中,该两个rc电路中各个rc电路之间对应的时间常数不同,以产生上述上电控制信号。具体的,各个rc电路均连接系统电源200,在系统电源200供电后,各个rc电路在充电过程中,由于时间常数不同,两个rc电路的电压的高低变化方式和/或高低变化时序不同,即可产生上述上电控制信号。可以理解,上电控制电路1010还可以包括其它元件或电路,此处不做具体限定。

[0033]

可选的,如图3所示,两个rc电路具体可以包括第一rc电路1011和第二rc电路1013,上电控制电路1010还包括开关元件1012。开关元件1012连接在第一rc电路1011和第二rc电路1013之间,第一rc电路1011和第二rc电路1013均连接系统电源200(图中未示出),第二rc电路1013连接电源管理芯片1020(图中未示出),通过开关元件1012的配合,使得系统电源200供电后,第一rc电路1011和第二rc电路1013在充电过程中即可产生上述上电控制信号。

[0034]

可选的,开关元件1012与第一rc电路1011和第二rc电路1013的具体连接方式可以是:开关元件1012的第一端连接在第一rc电路1011的电阻和电容之间,开关元件1012的第二端连接在第二rc电路1013的电阻和电容之间,开关元件1012的第三端接地。

[0035]

可选的,开关元件1012包括三极管或金属氧化物半导体场效应(metal oxide semiconductor,mos)管。

[0036]

可选的,第二rc电路1013的输出端连接电源管理芯片1020的上电控制管脚(例如上电触发onkey管脚),第二rc电路1013的输出端位于第二rc电路1013的电阻和电容之间,第二rc电路1013的输出端,用于系统电源200供电后,在第一rc电路1011和第二rc电路1013的充电过程中,产生上电控制信号,并将上电控制信号通过上电控制管脚输入电源管理芯片1020。

[0037]

可选的,如图4所示,上电控制电路1010还包括放电回路1014。放电回路1014与第一rc电路1011并联连接,放电回路1014,用于在系统电源200下电后对第一rc电路1011放电,以保证在系统电源200下一次供电后,通过开关元件1012的配合,使得第一rc电路1011和第二rc电路1013在充电过程中可再次产生上述上电控制信号,保证电路可靠性。

[0038]

可选的,放电回路1014包括二极管和电阻,放电回路1014包括的二极管和电阻与第一rc电路1011的电阻并联连接。

[0039]

可选的,第一rc电路1011的时间常数大于第二rc电路1013的时间常数,意味着第二rc电路1013的电容的端电压比第一rc电路1011的电容的端电压先达到系统电源200的电压,从而得以产生符合要求的上电控制信号。

[0040]

可选的,第一rc电路1011对应的第一时长减去第二rc电路1013对应的第二时长大于或等于预设时长。其中,第一时长为从系统电源200供电开始,第一rc电路1011的电容的端电压达到开关元件1012的开启电压所需的时长,第二时长为从系统电源200供电开始,第二rc电路1013的电容的端电压达到系统电源200的电压所需的时长。

[0041]

可选的,上述预设时长为处理器300从上电开始到上电成功所需的最短时长,以保证产生的上电控制信号能够达到处理器300上电完成的要求。

[0042]

可选的,如图5所示,两个rc电路具体可以包括第三rc电路1015和第四rc电路1016,上电控制电路1010还包括逻辑门电路1017。逻辑门电路1017的输入端连接第三rc电路1015、第四rc电路1016,第三rc电路1015、第四rc电路1016和逻辑门电路1017均连接系统电源200(图中未示出),逻辑门电路1017的输出端连接电源管理芯片1020(图中未示出)。系统电源200供电后,在第三rc电路1015和第四rc电路1016的充电过程中,逻辑门电路1017的输出端即可产生上述上电控制信号。

[0043]

可选的,逻辑门电路1017与第三rc电路1015和第四rc电路1016的具体连接方式可以是:逻辑门电路1017的一个输入端连接在第三rc电路1015的电阻和电容之间,逻辑门电路1017的另一个输入端连接在第四rc电路1016的电阻和电容之间,第三rc电路1015的电阻连接系统电源200,第四rc电路1016的电容连接系统电源200。

[0044]

可选的,逻辑门电路1017包括与门电路。

[0045]

可选的,逻辑门电路1017的输出端连接电源管理芯片1020的上电控制管脚,逻辑门电路1017的输出端,用于产生上述上电控制信号,并将上电控制信号通过上电控制管脚输入电源管理芯片1020。

[0046]

可选的,上电控制电路1010还包括放电回路。放电回路与第三rc电路1015并联连接,放电回路,用于在系统电源200下电后对第三rc电路1015放电,以保证在系统电源200下一次供电后,通过逻辑门电路1017的配合,使得第三rc电路1015和第四rc电路1016在充电过程中可再次产生上述上电控制信号,保证电路可靠性。

[0047]

可选的,放电回路包括二极管。二极管与第三rc电路1015的电阻并联连接。

[0048]

可选的,第三rc电路1015的时间常数小于第四rc电路1016的时间常数,意味着第四rc电路1016的电阻和电容之间的电压降为低电平所花费的时间比第三rc电路1015的电容的端电压达到系统电源的电压所花费的时间要长,从而得以产生符合要求的上电控制信号。

[0049]

可选的,第四rc电路1016对应的第四时长减去第三rc电路1015对应的第三时长大于或等于预设时长。其中,第三时长为从系统电源200供电开始,第三rc电路1015的电容的端电压达到系统电源200的电压所需的时长,第四时长为从系统电源200供电开始,第四rc电路1016的电阻和电容之间的电压从系统电源200的电压降为低电平所需的时长。

[0050]

可选的,上述预设时长为处理器300从上电开始到上电成功所需的最短时长,以保证产生的上电控制信号能够达到处理器300上电完成的要求。

[0051]

可选的,如图6所示,是本申请实施例提供的另一种电源管理装置的电路结构示意图,其中:

[0052]

电阻r1、电容c1、mos管q1、电阻r2、电容c2、二极管d1和电阻r3构成上述电源管理装置的上电控制电路1010。

[0053]

具体的,电阻r1、电容c1构成上电控制电路1010的第一rc电路1011,mos管q1作为上电控制电路1010的开关元件1012,电阻r2、电容c2构成上电控制电路1010的第二rc电路1013,二极管d1和电阻r3构成上电控制电路1010的放电回路1014,图中的q1以n沟道mos管为例。

[0054]

其中,第一rc电路1011和第二rc电路1013的一端均连接系统电源vsys,第一rc电路1011和第二rc电路1013的另一端均接地,第二rc电路1013的输出端b点(位于r2和c2之间)连接电源管理芯片pmic的上电控制管脚(即上电触发onkey管脚),作为开关元件1012的q1的栅极(gate,g)连接在第一rc电路1011的r1和c1之间的a点,开关元件1012的漏极(drain,d)连接在第二rc电路1013的输出端b点,开关元件1012的源极(source,s)接地,放电回路1014的d1与第一rc电路1011的r1并联连接,放电回路1014的r3的一端连接系统电源vsys,另一端接地。

[0055]

其中,第一rc电路1011的时间常数大于第二rc电路1013的时间常数。

[0056]

其中,第一rc电路1011对应的第一时长减去第二rc电路1013对应的第二时长大于或等于预设时长。其中,第一时长为从系统电源vsys供电开始,第一rc电路1011的电容c1的端电压(即a点电压)达到q1的开启电压所需的时长,第二时长为从系统电源vsys供电开始,第二rc电路1013的电容c2的端电压(即b点电压)达到系统电源vsys的电压所需的时长,该预设时长为电子设备的处理器从上电开始到上电成功所需的最短时长。

[0057]

具体的电路工作原理如下:

[0058]

(1)系统电源vsys刚供电的瞬间,由于电容c1两端的电压不能瞬变,故a点初始电压为0v,q1不导通,同样的,由于电容c2两端的电压也不能瞬变,故b点初始电压也为0v。

[0059]

(2)由于第一rc电路1011的时间常数大于第二rc电路1013的时间常数,故b点电压比a点电压先拉到系统电源vsys的电压,b点先产生上升沿信号。

[0060]

(3)当r1、c1充电使得a点电压达到q1的开启电压vth时,q1导通,此时b点电压被拉低为0v,在这个过程中,b点自动产生了一个从低电平到高电平的脉冲信号(即上述上电控制信号)。

[0061]

(4)当系统电源vsys下电时,d1、r3构成的放电回路1014对第一rc电路1011进行放电,使得a点电压慢慢泄放到0v,以保证在系统电源vsys下一次刚供电的瞬间,a点初始电压仍为0v,使得第一rc电路1011和第二rc电路1013在充电过程中b点可再次自动产生上述上电控制信号,以保证电路可靠性。

[0062]

其中,如图7所示,是第一rc电路1011和第二rc电路1013在充放电过程中电容的端电压的变化示意图。结合图7可知,在t1时刻,系统电源vsys开始供电,b点电压比a点电压先拉到系统电源vsys的电压,在t2时刻,a点电压达到q1的开启电压vth,q1导通,b点电压被拉低为0v,在t3时刻,a点电压拉到系统电源vsys的电压。可以理解的是,通过调整r1、r2、c1、c2、q1等元器件的参数,可以使得从b点电压拉到系统电源vsys的电压到b点电压被拉低为0v所持续的时长大于或等于电子设备的处理器从上电开始到上电成功所需的最短时长,或者说,从系统电源vsys供电开始,a点电压拉到q1的开启电压所需的时长减去b点电压拉到系统电源vsys的电压所需的时长达到电子设备的处理器从上电开始到上电成功所需的最短时长。

[0063]

可选的,如图8所示,是本申请实施例提供的一种电源管理芯片的开机电源时序

图,其中:上电控制信号产生并输入电源管理芯片的上电触发管脚后,首先有一定的防抖动debounce的时长(如100ms),然后上电控制信号维持在高电平,处理器系统的各个单元相继进行上电(包括参考电源vref、核心电源vcore、中央处理器电源varm、图形处理器电源vgpu、输入/输出接口电源vio1/vio2),并且上电控制信号需要保持高电平直到处理器系统的最后一个单元完成上电(如输入/输出接口电源vio1/vio2)才能使得处理器系统成功上电,可见,上电控制信号保持在高电平的时长需要达到一定时长才能完成处理器系统的全部上电。

[0064]

需要说明的是,结合图8,上述预设时长(即电子设备的处理器从上电开始到上电成功所需的最短时长)具体应包括使得pmic进入开机时序的100ms(即防抖动debounce的时长),以及处理器系统的各个单元全部完成上电所需的时长。其中,这里的100ms只是示意性说明,具体数值和电源管理芯片的类型相关。

[0065]

其中,如图9所示,是第二rc电路1013的b点产生的上电控制信号的实测波形图,系统电源vsys供电后,b点电压拉到系统电源vsys的电压,a点电压达到q1的开启电压vth时,q1导通,b点电压被拉低为0v,在这个过程中,b点产生符合触发条件的上电控制信号。其中,触发条件即:从低电平到高电平的脉冲信号,且该脉冲信号需要维持高电平的时长达到电子设备的处理器从上电开始到上电成功所需的最短时长。

[0066]

可选的,当电子设备的其它电路模块上电成功后,本申请实施例中的处理器以及电源管理装置对应的系统电源vsys才会上电,才会执行本申请实施例所描述的上电控制逻辑。

[0067]

需要说明的是,图6所示的电路中r1、r2、c1、c2、q1等元器件的参数取值以及电路连接方式并不唯一,可以根据电源管理芯片对上电控制信号的波形要求而灵活设计,本申请实施例不做限定。

[0068]

可选的,如图10所示,是本申请实施例提供的又一种电源管理装置的电路结构示意图,其中:

[0069]

电阻r1、电容c1、电阻r2、电容c2、与门(and)电路u1和二极管d1构成上述电源管理装置的上电控制电路1010。

[0070]

具体的,电阻r1、电容c1构成上电控制电路1010的第三rc电路1015,电阻r2、电容c2构成上电控制电路1010的第四rc电路1016,二极管d1构成上电控制电路1010的放电回路。

[0071]

其中,第三rc电路1015和第四rc电路1016的一端均连接系统电源vsys,具体是第三rc电路1015的电阻r1连接系统电源vsys,第四rc电路1016的电容c2连接系统电源vsys。第三rc电路1015和第四rc电路1016的另一端均接地gnd,与门电路u1的输入端1连接在第三rc电路1015的电阻r1和电容c1之间的a点,与门电路u1的输入端2连接在第四rc电路1016的电阻r2和电容c2之间的b点。与门电路u1的输出端4连接电源管理芯片pmic的上电控制管脚(例如上电触发onkey管脚),与门电路u1的电源正极端5连接系统电源vsys,与门电路u1的电源负极端3接地gnd,二极管d1与第三rc电路1015的电阻r1并联连接。

[0072]

其中,可选的,第三rc电路1015的时间常数小于第四rc电路1016的时间常数。

[0073]

其中,第四rc电路1016对应的第四时长减去第三rc电路1015对应的第三时长大于或等于预设时长。其中,第三时长为从系统电源vsys供电开始,第三rc电路1015的电容c1的

端电压(即a点电压)达到系统电源vsys的电压所需的时长,第四时长为从系统电源vsys供电开始,第四rc电路1016的电阻r2和电容c2之间的电压(即b点电压)从系统电源vsys的电压降为低电平所需的时长,该预设时长为电子设备的处理器从上电开始到上电成功所需的最短时长。

[0074]

具体的电路工作原理如下:

[0075]

(1)系统电源vsys刚供电的瞬间,由于电容c1和c2两端的电压不能瞬变,故a点初始电压为0v,b点初始电压为系统电源vsys的电压,由于u1是个与门电路,故与门电路u1的输出端c的输出为低电平。

[0076]

(2)由于第三rc电路1015的时间常数小于第四rc电路1016的时间常数,故a点电压先拉到系统电源vsys的电压变为高电平,然后b点电压后降为低电平。

[0077]

(3)在a点电压变为高电平,b点电压也是高电平的期间,与门电路u1的输出端c的输出为高电平,此时a点电压处于稳定,第四rc电路1016的电容c2还在充电中。

[0078]

(4)当第四rc电路1016的电容c2完成充电后,b点电压降为低电平,此时a点电压还是高电平,则与门电路u1的输出端c的输出为低电平,从而与门电路u1的输出端c的输出电平变化为:低电平—>高电平—>低电平,从而产生了符合要求的上电控制信号。

[0079]

需要说明的是,图10所示的电路中r1、r2、c1、c2、u1等元器件的参数取值以及电路连接方式并不唯一,可以根据电源管理芯片对上电控制信号的波形要求而灵活设计,本申请实施例不做限定。

[0080]

可见,本申请实施例利用分立元器件即可搭建上电控制电路,并在系统电源供电后自动产生上电控制信号,替代了目前常用的按键触发信号,适用在各种不需要使用按键的场景下完成上电触发开机功能,有效解决不使用按键开机的场景中处理器系统的正常上电问题。此外,本申请实施例利用分立元器件搭建上电控制电路,并没有粗暴地使用集成芯片直接产生上电控制信号,降低产品成本的同时也降低了硬件出错的概率,保证产品稳定性。

[0081]

请参阅图11,为本申请实施例提供的一种电子设备的电路结构示意图。所述电子设备10包括系统电源200、处理器300以及前文所述的电源管理装置100,其中:

[0082]

电源管理装置100,用于在系统电源200供电后对处理器300上电。

[0083]

可选的,电子设备10包括但不限于遥控设备。

[0084]

可选的,遥控设备为可移动平台的遥控终端,例如,可移动平台包括无人机、无人车等,对应的遥控终端包括遥控器等。

[0085]

请参阅图12,为本申请实施例提供的一种可移动平台组件的电路结构示意图。所述可移动平台组件包括遥控终端20和可移动平台30,其中:

[0086]

遥控终端20,用于控制可移动平台30。

[0087]

其中,遥控终端20包括系统电源200、处理器300以及前文所述的电源管理装置100,电源管理装置100用于在系统电源200供电后对处理器300上电。

[0088]

综上可知,本申请实施例中用于对无人机等可移动平台进行控制的遥控器,在开机待各功能模块上电完成后,通过电源管理装置即可自动、准确地产生其中的应用处理器所需的上电触发信号,有效替代了目前常用的按键触发信号,解决了无法使用按键开机的场景中处理器系统的正常上电问题。此外,本申请实施例的电源管理装置都是利用分立元

器件搭建的,并没有粗暴地直接使用集成芯片,从而降低产品成本的同时也降低了硬件出错的概率,保证产品稳定性。进一步的,减少了按键的数量,有利于应用该电源管理装置的电子设备的空间布局以及简约化设计。

[0089]

以上对本申请实施例所提供的一种电源管理装置、电子设备及可移动平台组件进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的核心思想;同时,对于本领域的一般技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1