电路信号偏移的调整装置以及调整方法与流程

1.本发明涉及一种电路信号偏移(skew)的调整装置以及调整方法,尤其涉及一种依据时钟树(clock tree)进行分析的电路信号偏移的调整装置以及调整方法。

背景技术:

2.在电路设计领域中,基于电路在运作中,可能发生大数量的缓存器,在相同的时间上发生转态现象,而导致操作电压瞬时大幅被抽载而造成电压下降的状况。为避免这样的情况发生,在电路中进行适度的偏移值(skew)调整,是需要的。

3.在现有的技术领域中,设计者需要针对电路中,关于时钟信号的架构、电路的功率消耗、实体的布局位置等多种变因进行考虑,才能有效的进行偏移值的调整动作。这在电路架构越来越复杂的今天,会使得电路的分析动作旷日废时。

4.另外,现有的技术领域中,设计者常仅针对电路中缓存器的数量进行考虑,这样所进行的偏移值的调整动作,所能提高的电路效益是有限的。

技术实现要素:

5.本发明是针对一种电路信号偏移的调整装置以及调整方法,可简单的针对电路中的信号偏移进行调整,并提升电路的表现质量。

6.根据本发明的实施例,电路信号偏移的调整方法,包括:提供控制器以执行:基于多个时钟信号的每一,依据电路的网络链接表对电路进行分割以产生多个电路分区;分别针对电路分区进行群集动作以获得多个电路分群;针对电路分群的布局位置的相邻状态进行识别;以及,依据相邻状态以对各电路分群进行偏移值的调整动作。

7.根据本发明的实施例,电路信号偏移的调整装置包括控制器以及存储元件。控制器耦接存储元件,并用以执行上述的电路信号偏移的调整方法。

8.基于上述,本发明通过针对电路进行分割,并进行分群的动作,通过电路分群的布局位置的相邻状态进行识别,并依据电路分群的相邻状态来进行各电路分群的偏移值的调整动作。可简化电路信号偏移的调整动作。以在兼顾信号质量以及设计时间的前提下,完成电路偏移的调整。

附图说明

9.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

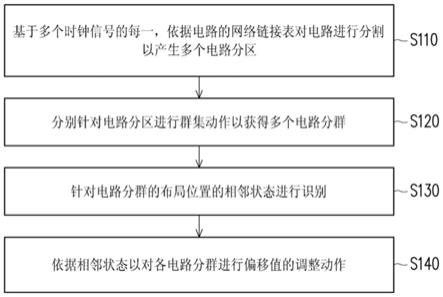

10.图1为本发明一实施例的电路信号偏移的调整方法的流程图;

11.图2、图3a以及图3b为本发明实施例的电路分区产生方式的示意图;

12.图4以及图5a至图5b为本发明实施例的电路分区的群集动作的示意图;

13.图6为本发明实施例的电路分群的布局位置的相邻状态的识别动作的示意图;

14.图7为本发明实施例的电路分群的偏移值的调整动作的流程图;

15.图8为本发明实施例的电流-时间表的示意图;

16.图9为本发明一实施例的电路信号偏移的调整装置的示意图。

17.附图标号说明

18.200:电路;

19.610:电路布局;

20.810:电流表;

21.820:时间轴;

22.830:电流和;

23.900:调整装置;

24.910:控制器;

25.920:存储元件;

26.a、b、c、d:分支端口;

27.a1~a3、b1、b:子分支端口;

28.bt:上层区块;

29.cli:延迟信息;

30.clk:时钟信号;

31.cm、cm1~cmn:价值矩阵;

32.cra1~cra3、crb1、crb2、crc:电路;

33.g1c~g4c:分布范围;

34.g1c1、g1c2:子分布范围;

35.ga、gb、gc、g1~g4:电路分群;

36.pi:电源信息;

37.pt1、pt2、pta:分区树;

38.rg1~rg4、rg1a、rg2a:缓存器;

39.sna、snb、snc、sna1~sna3、snb1、snb2:分支节点;

40.s110~s140:电路信号偏移的调整步骤;

41.s310~s314:建立分区树的步骤;

42.s410~s4110:电路分区的群集动作步骤;

43.s710~s790:偏移值的调整动作步骤;

44.sb1、sb2:下层区块。

具体实施方式

45.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在附图和描述中用来表示相同或相似部分。

46.请参照图1,图1为本发明一实施例的电路信号偏移的调整方法的流程图。本发明实施例的动作流程,可针对电路的网络链接表(netlist)来进行。其中,在步骤s110中,基于电路中的多个时钟信号的每一,依据电路的网络链接表对电路进行分割以产生多个电路分区。其中,步骤s110中针对电路进行分割所产生的多个电路分区,可以分别产生对应的分区树(partition tree)。分区树可用以表示对应的电路分区的架构。

47.并且,在步骤s120中,分别针对电路分区进行群集动作,并藉以获得多个电路分群,藉由上述群集动作来使各电路分区的分区树的尺寸可以缩减,并降低计算的复杂度。

48.接着,在步骤s130中,针对电路分群在电路中的实体布局位置的相邻状态进行识别,并在步骤s140中,依据上述的相邻状态,以对各电路分群进行偏移值的调整动作。

49.在本发明实施例中,步骤s110中的电路分割动作,是依据电路的网络链接表,依据由上层至下层(top-down)的方式来进行的。在步骤s120中,针对电路分区的群集动作,则是依据由下层至上层(bottom-up)的方式来进行。在此请注意,本发明通过针对电路的分区以及群集动作,可有效简化偏移分析的复杂度,并配合电路分群的相邻状态,来进行电路偏移值的调整动作。可在兼顾电路表现度的前提下,提升电路偏移的分析速度。

50.以下请参照图2、图3a以及图3b,图2、图3a以及图3b为本发明实施例的电路分区产生方式的示意图。在图2中,电路200为完整电路中的一部分电路。电路200具有上层区块bt,上层区块bt中包括下层区块sb1以及sb2。电路200基于时钟信号clk进行操作。基于时钟信号clk以针对电路200进行追踪,可在下层区块sb1获得分支端口a以及b。而由分支端口a出发,往下层区块sb2的方向追踪,则可获得分支端口c以及d。

51.在图3a中表示对应上述的电路追踪动作所产生的一分区树pt1。图3b中则表示建立分区树pt1的动作流程。其中,在进行电路追踪的初始状态,可产生分区树pt1的根节点rn。接着,在图3b中,当在每一分支端口被发现时,可执行步骤s310,并判断各分支端口上的控制缓存器数量或控制缓存器的功率消耗是否小于预设的临界值。当分支端口上的控制缓存器数量或控制缓存器的功率消耗小于预设的临界值时,可终止这个路径的追踪动作(步骤s320)。相反的,当分支端口上的控制缓存器数量或控制缓存器的功率消耗不小于预设的临界值时,则针对对应的分支端口进行追踪(步骤s311)。接着,步骤s312则在分区树中,对应每一个分支端口建立分支节点。并在步骤s313中,以分支节点进行连接以作为子(child)分支节点。并在步骤s314中完成各电路分区的产生动作。

52.依据图2的电路200为范例,在图3a中,当电路追踪动作发现分支端口a以及b时,可依据分支端口a以及b分别建立分支节点sn11以及sn21。并使分支节点sn11以及sn21连接至根节点rn。其中,分支节点sn11以及sn21可以为根节点rn的子分支节点,相对的根节点rn为分支节点sn11以及sn21的亲(parent)节点。在此,判断分支端口a以及分支端口b的控制缓存器数量或控制缓存器的功率消耗,例如,若分支端口b的控制缓存器数量或控制缓存器的功率消耗小于临界值,则可终止针对分支端口b下游的电路进行追踪。若分支端口a的控制缓存器数量或控制缓存器的功率消耗不小于临界值,则针对分支端口a下游的电路进行追踪,并获得下层区块sb2上的分支端口c以及d。对应分支端口c以及d,则可分别建立分支节点sn12以及sn22。

53.接续上述,若判断出分支端口c以及d的控制缓存器数量或控制缓存器的功率消耗均小于临界值,则可结束电路200的追踪动作。在电路200的追踪动作结束的同时,电路的分割动作可以完成。对应电路200的分区树pt1的建立也可以完成。

54.以下请参照图4以及图5a至图5b。图4以及图5a至图5b为本发明实施例的电路分区的群集动作的示意图。其中,图4为针对电路分区进行群集动作的流程图。在步骤s410中,针对每一电路分区的分区树,取得最深层次d,并在步骤s420中设定目前层次为层次i,其中i=d-1。也就是说目前层次(层次i)为最深层次d的上一层。

55.接着,步骤s430中,取用层次i中,对应最深层次d的分支节点为子分支节点,并取用上述子分支节点在层次i中对应的亲分支节点。

56.在此值得一提的,在每一电路分区的分区树,其中的分支节点具有多个数值,其中,上述的多个数值分别表示分支节点对应的缓存器数量或功率消耗。

57.步骤s440中,建立暂存字段p,其中暂存字段p具有一容量值。步骤s440并判断出子分支节点中,具有最大数值的子分支节点k,并将子分支节点k搬移至暂存字段p中。另外,使暂存字段p的容量值与子分支节点k的数值相减,并获得暂存字段p的剩余容量值。

58.步骤s450则取用多个分支节点中,尚未被群集的另一子分支节点c。步骤s460判断暂存字段p的剩余容量值是否大于子分支节点c的数值,以判断暂存字段p的剩余容量是否不足。若当暂存字段p的剩余容量不足时,建立另一暂存字段p’,并将子分支节点c放置于暂存字段p’中(步骤s4120),并重新执行步骤s480。相反的,若当暂存字段p的剩余容量足够时,则搬移子分支节点c至暂存字段p中,并再次计算出暂存字段p的剩余容量(步骤s470)。

59.步骤s480中,判断层次d中,是否尚有未群集的子分支节点。若尚有未群集的子分支节点,则重复执行步骤s450至s470,直至层次d中所有的子分支节点的群集动作均完成。接着执行步骤s490。

60.在步骤s490中,针对目前层次i中是否有其他的亲分支节点。若有其他的亲分支节点,则重新执行步骤s430来针对另一亲分支节点的子分支节点进行群集动作。相反的,若无其他的亲分支节点,则使i递减1(步骤s4100)。

61.步骤s4110中,则判断i是否等于0,并在当i=0时,结束电路分区的群集动作。此外,若i不等于0,则重新执行步骤s480。其中,当i=0时,表示所有层次的分支节点都完成群集动作。

62.在图5a至图5b的实施范例中,电路分区z1中包括端口t以及子电路分区sz1~sz3。端口t接收时钟信号clk。电路分区sz1中包括分支端口a以及子分支端口a1~a3。子分支端口a1~a3分别对应连接电路cra1~cra3,电路cra1~cra3分别具有相同或不相同量值的控制缓存器数量或控制缓存器的功率消耗。电路分区sz3中包括分支端口b以及子分支端口b1、b2。子分支端口b1、b3分别对应连接电路crb1、crb2,电路crb1、crb2分别具有不相同量值的控制缓存器数量或控制缓存器的功率消耗。电路分区sz2中则包括分支端口c。分支端口c对应连接电路crc。

63.本发明实施例中,依据电路分区z1可以建立分区树pta。分区树pta具有多个分支节点sna、snb、snc、sna1~sna3、snb1以及snb2。分支节点sna、snb、snc、sna1~sna3、snb1以及snb2分别对应分支端口a、b、c以及子分支端口a1~a3、b1以及b2。在分区树pta中,最底层的分支节点snc、sna1~sna3、snb1以及snb2分别记录多个数值,在本实施例中,这些分支节点snc、sna1~sna3、snb1以及snb2记录的数值分别为4、4、2、1、5、2。各分支节点snc、sna1~sna3、snb1以及snb2记录的数值分别表示对应的分支端口连接的控制缓存器数量或控制缓存器的功率消耗的量值。以控制缓存器数量为例,分支节点sna1记录的数值4可以表示子分支端口a1连接4000个控制缓存器。

64.接着,通过分割算法(partition algorithm),可针对分区树pta执行群集动作,并产生多个电路分群g1~g4。本实施例的群集动作,可基于电路分群g1~g4中的多个分群数值总合的均匀度,来对进行调整。所谓的分群数值总合,就是各个电路分群中包括的所有的

分支节点中所记录的数值的总和。以电路分群g1为范例,电路分群g1的分群数值总合可等于分支节点snb1、snb2、snc中的数值总和(=2+5+4=11)。而多个分群数值总合的均匀度,则可以通过多个分群数值总合的标准偏差来获得。在本实施例中,分割算法的群集动作,可以通过使多个分群数值总合的标准偏差最小化的方式来进行。

65.以下请参照图6,图6为本发明实施例的电路分群的布局位置的相邻状态的识别动作的示意图。在完成了电路中的多个电路分群的群集动作后,可针对电路分群中的多个缓存器在电路中的实体布局的位置进行分析。

66.在图6中,电路布局610中具有多个缓存器rg1~rg4、rg1a以及rg2a。其中,缓存器rg1、rg1a属于相同的第一电路分群;缓存器rg2、rg2a属于相同的第二电路分群;缓存器rg3属于相同的第三电路分群;缓存器rg4则属于相同的第四电路分群。在进行电路分群的布局位置的相邻状态识别时,可通过本领域技术人员所熟知的聚类分析(clustering analysis)算法,例如k-平均算法或基于密度的空间聚类算法(density-based spatial clustering of application with noise,dbscan),或其他聚类分析算法,来针对电路布局610进行分析,并可产生多个分簇的分布范围g1c~g4c,并依据分布范围g1c~g4c彼此间的距离来建立相邻状态。

67.值得注意的,分布范围g1c~g4c分别对应第一电路分群至第四电路分群。分布范围g1c~g4c不必要包括对应的电路分群的所有缓存器。以缓存器rg1a、rg2a为范例,由于缓存器rg1a、rg2a与同一电路分群的其他缓存器rg1、rg2相距较远,因此在进行分簇动作时,会将缓存器rg1a、rg2a进行排除。另外,分布范围g1c~g4c两两间也可能相互重叠,未必会相互隔离。且同一分簇的分布范围可能分布在两个分开的区域中,例如分布范围g1c由子分布范围g1c1以及g1c2所组成,子分布范围g1c1以及g1c2相互分离。

68.关于各电路分群的偏移值的调整动作,请参照图7以及图8的为。其中图7为本发明实施例的电路分群的偏移值的调整动作的流程图。图8则为本发明实施例的电流-时间表的示意图。

69.在图7中,步骤s710中,通过接收已完成群集动作的各个电路分群(i),并找出电路分群(i)所可能调整的最大偏移(i)。步骤s720中,则针对各个电路分群(i)进行电流波形分析,并获得各个电路-时间表(i)。在此,步骤s720中,另通过时钟信号的延迟信息cli以及电源信息pi,来进行各个电路分群(i)的电流波形分析。其中延迟信息cli记录时钟信号在电路工作时所可能产生的延迟状态,电源信息pi则记录电路工作时的功率消耗状态。而所产生的电流-时间表如图8所示。其中,第一行记录随着时间画的电流状态分布的电流表810;第二行则为对应时钟信号的延迟的时间轴820,其中时间轴820区分为多个时间区间0至时间区间6;第三行则为对应时间区间0至时间区间6的多个电流和830。

70.步骤s730则依据小于最大偏移(i)的多个参考偏移值sk,来进行各个电路-时间表(i)的平移动作。步骤s740则基于多个参考偏移值sk来使对应各个电路分群(i)的电路-时间表(i)进行平移,并使平移后的电路-时间表(i)相互重叠比较,并在步骤s750中,产生任两电路分群间,在不同参考偏移值下的电流加总值。步骤s760中则依据计算出的多个电流加总值来建立出价值矩阵cm。其中,价值矩阵cm可依据参考偏移值sk来建立,也就是说,价值矩阵cm的数量与所设定的参考偏移值sk的数量是相同的。

71.附带一提的,在产生任两电路分群间的电流加总值的关系时,另可依据电路分群

的相邻状态,来进行各电流加总值的适度调整。简单来说明,当两电路分群间具有相对高程度的相邻状态(彼此间的距离小于一第一临界值)时,可调高对应的电流加总值。相反的,当两电路分群间具有相对低程度的相邻状态时(彼此间的距离大于一第二临界值),可不需调整对应的电流加总值。上述的第二临界值可以大于或等于第一临界值。

72.在图7中,单一个价值矩阵(例如价值矩阵cm1)可对应多个参考偏移值sk的其中之一。价值矩阵cm1记录多个电路分群ga~gf间,任两间对应的电流加总值。其中,电路分群ga与gb对应的电流加总值注记为cost(a,b),其余可依此原则类推。

73.步骤s770中,使全部的价值矩阵cm1~cmn中,分别对应各电路分群的电流加总值相加,并获得对应各电路分群的全区和。以电路分群ga为范例,对应电路分群ga的全区和等于全部的价值矩阵cm1~cmn中的电流加总值cost(a,b)至cost(a,f)的总和。对应电路分群gc的全区和等于全部的价值矩阵cm1~cmn中的电流加总值cost(c,a)至cost(c,f)的总和。接着,并依据电路分群ga~gf对应的全区和的大小,来设定电路分群ga~gf的偏移值调整的优先度。其中,在本实施例中,电路分群ga~gf的偏移值调整的优先度高低,正相关于电路分群ga~gf对应的全区和的大小。也就是说,若电路分群ga具有最大的全区和,则电路分群ga具有最高的优先度。

74.步骤s780则依据步骤s770所获得的优先度来对各个电路分群ga~gf进行排序。并且,在步骤s790中,基于优先度,对应各个参考偏移值sk,分别计算各电路分群ga~gf的电流加总值的多个分区和。细节上来说明,所谓的分区和,则是在单一价值矩阵(例如价值矩阵cm1)中,各电路分群(以电路分群ga为范例)的行中所有的电流加总值cost(a,b)至cost(a,f)的和。也就是说,对应电路分群ga,依据不同的价值矩阵cm1~cmn,可以计算出不同的分区和。接着,再依据所有分区和中的最小者,其所对应的参考偏移值来对电路分群ga进行偏移值的调整。例如,若价值矩阵cm1中的电路分群ga的分区和是最小的,且价值矩阵cm1对应偏移值sk1时,则依据偏移值sk1来进行电路分群ga的偏移值调整。

75.以下请参照图9,图9为本发明一实施例的电路信号偏移的调整装置的示意图。电路信号偏移的调整装置900包括控制器910以及存储元件920。控制器910耦接存储元件920,用以接收电路的网络链接表。控制器910并用以执行如上所述的多个实施例的电路信号偏移的调整方法,并通过在电路的网络链接表中,针对各电路分群加入延迟组件,以调整对各电路分群的偏移值。

76.在实体电路中,依据电路分群的偏移值的调整动作,控制器910所加入的延迟组件,可产生调整后的网络链接表,并通过调整实体电路的布局,可使所产生的集成电路的表现度符合设计的预期。

77.附带一提的,在本实施例中,控制器910可以为具运算能力的处理器。或者,控制器910可以是通过硬件描述语言(hardware description language,hdl)或是其他任意本领域技术人员所熟知的数字电路的设计方式来进行设计,并通过现场可程序逻辑门阵行(field programmable gate array,fpga)、复杂可程序逻辑装置(complex programmable logic device,cpld)或是特殊应用集成电路(application-specific integrated circuit,asic)的方式来实现的硬件电路。此外,存储元件920可为各式随机存取内存(ram)、闪存(flash)等任意形式的储存媒介,但不以此为限。

78.综上所述,本发明通过针对电路进行分割以产生多个电路分区,再通过针对电路

分区进行群集以简化电路架构。本发明并分析电路分群的布局位置的相邻状态来对各电路分群进行偏移值的调整动作。在基于电路的表现度下,可有效降低分析动作的时间长度,提升偏移值调整动作的效能。

79.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1