时钟控制装置及相关产品的制作方法

1.本公开涉及集成电路技术领域,特别是涉及一种时钟控制装置及相关产品。

背景技术:

2.通常芯片在上电和负载功耗突然增加时,由于电源供电网络带宽的限制,无法及时响应负载电流的变化,导致芯片供电电压短时间内(通常小于20ns)产生较大的下降。电压的下降会导致芯片中逻辑电路时延增大。如果负载电流过大,导致电压下降到芯片安全电压以下,则会使得逻辑电路的时序无法满足建立时间的要求,从而产生亚稳态并导致电路运算结果出错。该问题称为电源随载下降(voltage droop)。相关技术中的处理方式对电源随载下降的控制效果较差。

技术实现要素:

3.基于此,有必要针对上述技术问题,提供一种时钟控制装置及相关产品。

4.根据本公开的一方面,提供了一种时钟控制装置,应用于处理器,所述装置包括:

5.电压检测模块,用于检测所述处理器中目标位置的供电电压;在所述供电电压小于或等于预设的第一阈值时,输出电压警报信号;

6.时钟展宽模块,连接到所述电压检测模块,用于在接收到所述电压警报信号时,根据与基准频率对应的第一时钟信号,生成第二时钟信号,以使所述处理器采用所述第二时钟信号进行数据处理,

7.其中,所述第二时钟信号的频率低于所述基准频率。

8.根据本公开的另一方面,提供了一种人工智能芯片,所述芯片包括上述的时钟控制装置。

9.根据本公开的另一方面,提供了一种电子设备,所述电子设备包括上述的人工智能芯片。

10.根据本公开的另一方面,提供了一种板卡,所述板卡包括:存储器件、接口装置和控制器件以及上述的人工智能芯片;

11.其中,所述人工智能芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;所述存储器件,用于存储数据;所述接口装置,用于实现所述人工智能芯片与外部设备之间的数据传输;所述控制器件,用于对所述人工智能芯片的状态进行监控。

12.根据本公开的时钟控制装置,能够在关键路径的供电电压低于阈值时,对时钟信号进行降频,增加逻辑电路建立时间裕量,并且降低处理器的负载,从而避免数据处理结果出错,并且实现对电压随载下降的控制。

13.根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

circuit,专用集成电路)芯片中的一种或组合。本公开对处理器的具体类型不作限制。

30.在一种可能的实现方式中,本公开中所提及的处理器可包括多个处理单元,每个处理单元可以独立运行所分配到的各种任务,如:卷积运算任务、池化任务或全连接任务等。本公开对处理单元及处理单元所运行的任务不作限制。

31.图1示出根据本公开实施例的时钟控制装置的处理器的示意图。如图1所示,处理器100包括多个处理单元101以及存储单元102,多个处理单元101用于执行指令序列,存储单元102用于存储数据,可包括随机存储器(ram,random access memory)和寄存器堆。

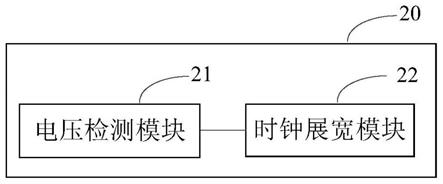

32.图2示出根据本公开实施例的时钟控制装置的结构框图。如图2所示,所述装置20包括:

33.电压检测模块21,用于检测所述处理器中目标位置的供电电压;在所述供电电压小于或等于预设的第一阈值时,输出电压警报信号;

34.时钟展宽模块22,连接到所述电压检测模块21,用于在接收到所述电压警报信号时,根据与基准频率对应的第一时钟信号,生成第二时钟信号,以使所述处理器采用所述第二时钟信号进行数据处理,

35.其中,所述第二时钟信号的频率低于所述基准频率。

36.举例来说,可以将处理器中关键路径的位置设定为目标位置,通过电压检测模块21检测该目标位置的供电电压。如果该供电电压小于或等于预设的第一阈值,也即该供电电压低于预设的低压阈值,则电压检测模块21可产生并输出警报信号。

37.在一种可能的实现方式中,时钟展宽模块22接收到电压检测模块21输出的警报信号时,可对基准频率对应的第一时钟信号进行降频,生成并输出降频后第二时钟信号,以使处理器采用第二时钟信号进行数据处理。

38.通过这种方式,能够在关键路径的供电电压低于阈值时,对时钟信号进行降频,增加逻辑电路建立时间裕量,并且降低处理器的负载,从而避免数据处理结果出错,并且实现对电压随载下降的控制。

39.在一种可能的实现方式中,电压检测模块21可包括第一检测单元,用于实现关键路径检测(critical path monitor,cpm)。

40.图3示出根据本公开实施例的第一检测单元的电路示意图。如图3所示,第一检测单元包括:

41.脉冲产生电路31,输入第五时钟信号,输出脉冲信号;

42.延迟电路32,连接到所述脉冲产生电路,输入所述脉冲信号,输出延迟后的脉冲信号,所述延迟后的脉冲信号和所述脉冲信号之间的延迟与所述目标位置的供电电压负相关;

43.电压检测及处理电路33,连接到所述延迟电路,用于根据所述延迟后的脉冲信号及所述第五时钟信号,确定所述目标位置的供电电压;在所述供电电压小于或等于第一阈值时,输出第一电压警报信号。

44.举例来说,脉冲产生电路(pulse generation circuit)31可例如包括串联的多级反相器和一个与非门,第五时钟信号(clk)直接输入与非门的一输入端,并经过多级反相器后,输入与非门的另一输入端。脉冲产生电路31在输入的第五时钟信号的第一个周期,产生用于测量的脉冲信号。该脉冲信号的脉宽可根据实际情况进行调节,本公开对此不作限制。

该第五时钟信号的频率可与第一时钟信号相同或不同,本公开对此不作限制。

45.在一种可能的实现方式中,延迟电路(tunable replica circuit,trc)32连接到脉冲产生电路31,可例如包括串联的多级反相器。输入的脉冲信号经过延迟电路32,会产生相应的传播延迟,输出延迟后的脉冲信号。其中,延迟后的脉冲信号和脉冲信号之间的延迟与目标位置的供电电压负相关,也即该延迟的大小会随着供电电压降低而变大。

46.图4示出根据本公开实施例的时钟控制装置的脉冲信号的示意图。如图4所示,在时钟信号(clk)41的第一个周期,脉冲产生电路产生脉冲信号(detect pulse)42,该脉冲信号42的脉宽可例如等于时钟信号41的时钟周期。脉冲信号42经过延迟电路后,输出延迟后的脉冲信号(delayed pulse in trc)43。如图4所示,该脉冲信号43的延迟随着供电电压减低而变大。可预先设定有参考延迟(detect reference)44(例如为一个时钟周期),如果脉冲信号43的延迟小于或等于参考延迟44,则可认为供电电压在合理的范围内;反之,如果脉冲信号43的延迟大于参考延迟44,则可认为供电电压异常(也即低于低压阈值),需要进行降频。

47.在一种可能的实现方式中,电压检测及处理电路33可对延迟后的脉冲信号进行时间-数字转换(time to digital convertor,tdc),并对转换后的信号进行处理。如图3所示,电压检测及处理电路33包括多级的延时器(例如偶数个反相器)、多级寄存器以及比较电路,输入延迟后的脉冲信号和第五时钟信号,生成与延时对应的数字信号,例如图3中的64位信号bit[0]、bit[1]、

…

、bit[63]、bit[64]。根据该数字信号,可确定出该延迟对应的电压值,该电压值与目标位置的供电电压相对应。其中,该数字信号、延时和供电电压之间的对应关系可以根据实验测量等方式预先确定,本公开对具体的确定方式不作限制。

[0048]

在一种可能的实现方式中,当电压降低时,脉冲信号经过可调延迟电路的传播延迟变大,时间-数字转换电路输出值中为高电平的比特变少,也即确定出该延迟对应的电压值降低。如果该电压值对应供电电压小于或等于预设的第一阈值(即低压阈值vth_low),则可输出第一电压警报信号(alarm1),以触发时钟展宽电路降频。可通过比较电路直接对多级寄存器输出的数字信号与预设的阈值信号(即低压阈值)进行比较,输出比较结果;根据比较结果确定是否发出第一电压警报信号,本公开对比较电路的具体实现方式不作限制。

[0049]

通过这种方式,可实现供电电压的检测,并在检测到电压随载下降的当前周期就输出警报信号,以便实现对电压随载下降的控制,提高了装置的响应速度。与相关技术相比,简化了电路结构,减小了电路面积。

[0050]

在一种可能的实现方式中,电压检测及处理电路33还用于:

[0051]

在输出所述第一电压警报信号期间,当所述供电电压大于或等于预设的第二阈值,且所述供电电压大于或等于第二阈值的持续时间达到预设的第一时长时,输出第一电压正常信号,其中,所述第二阈值大于所述第一阈值

[0052]

举例来说,在时钟展宽电路进行降频后,会导致处理器的数据处理性能下降,因此,在供电电压回升到设定的高压阈值且持续一定时间时,可恢复输出时钟的频率,输出时钟的频率为基准频率。

[0053]

在电压检测及处理电路33输出第一电压警报信号期间,可持续获取延迟对应的电压值,如果该电压值对应供电电压大于或等于预设的第二阈值,且所述供电电压大于或等于第二阈值的持续时间达到预设的第一时长,则可输出第一电压正常信号,以使时钟展宽

电路恢复输出时钟的频率,输出时钟的频率为基准频率。其中,第二阈值为设定的高压阈值(vth_high),大于第一阈值(低压阈值vth_low);第一时长可例如为预设的多个时钟周期,本公开对第二阈值及第一时长的具体取值不作限制。

[0054]

在一种可能的实现方式中,可通过比较电路直接对多级寄存器输出的数字信号与预设的阈值信号(即高压阈值)进行比较,输出比较结果;根据比较结果以及符合条件的比较结果的次数,确定是否发出第一电压正常信号,本公开对比较电路的具体实现方式不作限制。

[0055]

图5示出根据本公开实施例的时钟控制装置的供电电压调节过程的示意图。如图5所示,高压阈值(vth_high)>低压阈值(vth_low)>安全电压(safe_voltage)。在未采用时钟控制的情况下,如图5中的曲线a1所示,供电电压vdd随负载的增加而不断下降,从高压阈值(图5中的位置0)到达低压阈值(图5中的位置1)后继续下降,直到低于安全电压,可能导致数据处理结果出错。

[0056]

在采用时钟控制的情况下,如图5中的曲线a2所示,供电电压vdd从高压阈值(图5中的时间点0)到达低压阈值(图5中的时间点1)时,电压检测及处理电路输出电压警报信号,时钟展宽模块在接收到电压警报信号后进行降频,输出展宽后的时钟信号(stretched_clock),使得供电电压vdd在到达安全电压之前回升,从而避免了数据处理结果出错。

[0057]

在一种可能的实现方式中,在供电电压vdd回升到超过高压阈值(图5中的时间点2),并持续n个时钟周期(也即第一时长),到达图5中的时间点3后,电压检测及处理电路输出电压正常信号,以使时钟展宽电路恢复输出时钟的频率,输出时钟的频率为基准频率。

[0058]

根据本公开实施例的电压检测及处理电路,采用双稳线控制的方式,即在时间点1供电电压低于低阈值触发警报,供电电压回升到低阈值以上高阈值以下,警报不撤销;只有在时间点2供电电压回升到高阈值以上后再保持n个时钟周期到时间点3才撤销警报。该方式可以滤除供电电压上的微小波动对警报信号的影响,避免警报信号产生震荡,导致时钟展宽电路在降频和升频之间震荡,从而造成更大的供电电压波动。

[0059]

在一种可能的实现方式中,电压检测模块21可包括第二检测单元,第二检测单元包括:

[0060]

环形振荡电路,用于根据所述目标位置的供电电压,输出第四时钟信号;

[0061]

处理电路,连接到所述环形振荡电路,用于根据所述第四时钟信号确定预设的第二时长内的计数值;在所述计数值小于或等于预设的第一计数阈值时,输出第二电压警报信号。

[0062]

举例来说,电压检测模块21可采用环形振荡电路(ring oscillator)进行电压检测。图6示出根据本公开实施例的时钟控制装置的环形振荡电路的示意图。如图6所示,环形振荡电路可以是将奇数个反相器首尾连接,只要处理器上电,环形振荡电路就会自动振荡起来,产生所述第四时钟信号,其振荡频率与电压、温度、工艺有关,因此可利用环形振荡电路作为处理器工作状态的检测器。如果处理器的芯片工艺确定,工作温度变化不大,环形振荡电路的振荡频率随着电压升高而升高,随着电压降低而降低。

[0063]

在一种可能的实现方式中,环形振荡电路可根据目标位置(也即处理器的关键路径)的供电电压,输出第四时钟信号;处理电路可连接到所述环形振荡电路,根据第四时钟信号确定预设的第二时长内的计数值。其中,处理电路可包括计数器(未示出),将第四时钟

信号作为计数器的输入,在预设的第二时长(如1000ns)内,计数器的计数值可以反映供电电压的高低。

[0064]

在一种可能的实现方式中,处理电路可将计数值与预设的第一计数阈值进行比较,如果计数值小于或等于预设的第一计数阈值,则可认为供电电压异常(也即低于低压阈值),处理电路可输出第二电压警报信号,以触发时钟展宽电路降频。其中,第一计数阈值可为预先设定的对应低压阈值的计数值,本公开对第一计数阈值的具体取值不作限制。

[0065]

通过这种方式,可实现供电电压的检测,以便实现对电压随载下降的控制。

[0066]

在一种可能的实现方式中,所述处理电路还用于:

[0067]

在输出所述第二电压警报信号期间,当所述计数值大于或等于预设的第二计数阈值,且所述计数值大于或等于所述第二计数阈值的次数达到预设次数时,输出第二电压正常信号;

[0068]

其中,所述第二计数阈值大于所述第一计数阈值。

[0069]

举例来说,在时钟展宽电路进行降频后,会导致处理器的数据处理性能下降,因此,在供电电压回升到设定的高压阈值时,可恢复输出时钟的频率为基准频率。

[0070]

在处理电路输出第二电压警报信号期间,可持续获取多个第二时长的计数值,如果计数值大于或等于预设的第二计数阈值,且计数值大于或等于所述第二计数阈值的次数达到预设次数,则可输出第二电压正常信号,以使时钟展宽电路恢复输出时钟的频率为基准频率。其中,第二计数阈值为可为预先设定的对应高压阈值的计数值,大于第一计数阈值;预设次数可例如为5-10次,本公开对第二计数阈值及预设次数的具体取值不作限制。

[0071]

通过采用双稳线控制的方式,可以滤除供电电压上的微小波动对警报信号的影响,避免警报信号产生震荡,导致时钟展宽电路在降频和升频之间震荡,从而造成更大的供电电压波动。

[0072]

图7示出根据本公开实施例的时钟控制装置的结构框图。如图7所示,所述装置20的电压检测模块21包括第一检测单元211、所述第二检测单元212以及第一选择单元213,第一选择单元213分别连接第一检测单元211、所述第二检测单元212以及时钟展宽模块22。其中,第一选择单元213用于:

[0073]

将所述第一检测单元的输出信号或所述第二检测单元的输出信号输出到所述时钟展宽模块。

[0074]

举例来说,第一选择单元213可包括选择器,根据使能信号选通第一检测单元211的输出信号或所述第二检测单元212的输出信号,以便通过第一检测单元或第二检测单元对时钟展宽模块进行控制。其中,第一检测单元211和所述第二检测单元212可以独立工作,互不影响。

[0075]

当要求对电压随载下降进行快速响应时,可通过第一检测单元对时钟展宽模块进行控制;反之,可通过第二检测单元对时钟展宽模块进行控制。本领域技术人员可根据实际情况设定所选用的检测单元,本公开对此不作限制。通过这种方式,可提高时钟展宽控制的灵活性。

[0076]

在一种可能的实现方式中,电压检测模块可包括第一检测单元、第二检测单元及第二选择单元(未示出)。第二选择单元分别连接到第一检测单元、第二检测单元及时钟展宽模块,第二选择单元用于:

[0077]

在所述第一检测单元输出第一电压警报信号,和/或所述第二检测单元输出第二电压警报信号时,输出电压警报信号到所述时钟展宽模块;

[0078]

在所述第一检测单元输出第一电压正常信号,且所述第二检测单元输出第二电压正常信号时,输出电压正常信号到所述时钟展宽模块。

[0079]

举例来说,第二选择单元可例如包括或门(or),将第一检测单元的第一电压警报信号和第二检测单元的第二电压警报信号作为逻辑1,将第一检测单元的第一电压正常信号和第二检测单元的第二电压正常信号作为逻辑0。

[0080]

在所述第一检测单元输出第一电压警报信号(逻辑1),和/或所述第二检测单元输出第二电压警报信号(逻辑1)时,第二选择单元输出电压警报信号(逻辑1)到时钟展宽模块,以使时钟展宽模块进行降频;在第一检测单元输出第一电压正常信号(逻辑0),且所述第二检测单元输出第二电压正常信号(逻辑0)时,第二选择单元输出电压正常信号(逻辑0)到所述时钟展宽模块,以使时钟展宽模块恢复输出时钟的频率为基准频率。

[0081]

也就是说,第一电压警报信号和第二电压警报信号中只要有一个拉起,时钟展宽电路就发生降频;两个警报信号都撤销,时钟展宽电路才恢复原来的频率。

[0082]

通过这种方式,可以结合第一检测单元(cpm)对电压随载下降的快速响应与第二检测单元(环形振荡电路)对电压噪声不敏感的特性,保证系统可以快速响应电压垂降事件,降频之后又不会因为电压噪声而在电压垂降事件结束之前就恢复频率,进一步提高了时钟展宽控制的可靠性。

[0083]

在一种可能的实现方式中,如图7所示,时钟展宽模块22包括:

[0084]

时钟相位生成电路221,用于根据所述第一时钟信号,输出多个相位时钟信号;

[0085]

时钟展宽电路222,连接到所述时钟相位生成电路,用于在接收到所述电压警报信号时,根据所述多个相位时钟信号,通过门控时钟电路(integrate clock gating,icg)生成所述第二时钟信号。

[0086]

举例来说,时钟相位生成电路221可例如为dll(delay lock loop,延迟锁相环)电路,输入来自pll(phase lock loop,相位锁相环)的第一时钟信号,输出多个相位时钟信号,例如输出相位分别为0、45、90、135、180、225、270、315的8个相位时钟信号(相邻相位时钟之间的相位差为45度)。

[0087]

图8示出根据本公开实施例的时钟展宽模块的电路示意图。如图8所示,时钟相位生成电路221可生成8相位时钟,分别输入8个icg电路(icg0、icg1、

…

、icg7)。

[0088]

时钟展宽电路222在接收到来自电压检测模块21的电压警报信号(alarm)时,计数器cnt可开始进行计数,产生使能信号icg_en[7:0]的数字编码,并分别输入各个icg电路(icg0、icg1、

…

、icg7),使得各个icg电路分时段有效,输出多个相位时钟信号中的一个;经过或门(or)后,生成第二时钟信号clk_out。其中,门控时钟电路可采用相关技术中的任意电路结构,本公开对此不作限制。

[0089]

在一种可能的实现方式中,可在输出点对不同相位时钟进行组合,得到不同比例的降频时钟。在相位时钟信号为8个的情况下,可例如输出基准频率的8/9或4/5两种降频时钟(即第二时钟信号)。本领域技术人员可根据实际情况设置降频时钟的降频比例,本公开对此不作限制。

[0090]

图9a和图9b示出根据本公开实施例的第二时钟信号的示意图。图9a是生成频率为

8/9基准频率的第二时钟信号的示意图;图9b是生成频率为4/5基准频率的第二时钟信号的示意图。

[0091]

如图9a和图9b所示,可根据8个icg电路(icg0、icg1、

…

、icg7)的使能信号icg_en[7:0]的编码,控制各个icg在不同的时间段内生效(例如各个相位时钟信号的加粗部分),从而分时间段输出8个相位时钟信号(clk0、clk45、clk90、clk135、clk180、clk225、clk270、clk315)中的一个。经过或门(or)后,输出第二时钟信号clk_out,从而完成时钟的降频过程。其中,对于图9a的8/9基准频率,需要第一时钟信号的9个时钟周期,生成8个周期的第二时钟信号;对于图9b的4/5基准频率,需要第一时钟信号的5个时钟周期,生成4个周期的第二时钟信号。

[0092]

通过这种方式,能够实现时钟展宽,降低时钟频率从而降低处理器的负载,实现对电压随载下降的控制;并且采用门控时钟组成同步电路实现时钟展宽,能够提高展宽后的时钟信号的稳定性,不会产生毛刺。

[0093]

在一种可能的实现方式中,所述时钟展宽模块22还用于:在接收到电压正常信号时,根据所述第一时钟信号或所述多个相位时钟信号,生成第三时钟信号,以使所述处理器采用所述第三时钟信号进行数据处理,所述第三时钟信号的频率等于所述基准频率。

[0094]

举例来说,如果时钟展宽模块22接收到来自电压检测模块21的电压正常信号,则可停止时钟降频,生成并输出第三时钟信号,该第三时钟信号的频率等于基准频率。该第三时钟信号的相位可与第一时钟信号相同或不同,本公开对此不作限制。

[0095]

在一种可能的实现方式中,时钟展宽电路222在接收到电压正常信号时,可将第一时钟信号直接作为第三时钟信号输出;也可对第一时钟信号相位调整并作为第三时钟信号输出;还可选通多个相位时钟信号中的任意一个,作为第三时钟信号输出。本公开对第三时钟信号的具体生成方式不作限制。

[0096]

根据本公开实施例的时钟控制装置,能够在关键路径的供电电压低于阈值时,对处理器的时钟信号降频,增加逻辑电路建立时间裕量,并且降低处理器的负载,从而避免数据处理结果出错,并且实现对电压随载下降的控制。

[0097]

根据本公开的实施例,在采用关键路径检测cpm进行随载下降检测时,精度可以做到很高,其最小分辨率仅受限于电路所使用生产工艺本身的最小时延。因此可以对电压随载下降做到精细化检测;同时,cpm作为一个开环系统,其检测值在每个采样周期都会更新,可以做到检测到电压随载下降的当前采样周期就输出警报信号用于动态调频,提高了装置的响应速度。

[0098]

应该理解,上述的装置实施例仅是示意性的,本公开的装置还可通过其它的方式实现。例如,上述实施例中所述单元/模块的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式。例如,多个单元、模块或组件可以结合,或者可以集成到另一个系统,或一些特征可以忽略或不执行。

[0099]

另外,若无特别说明,在本公开各个实施例中的各功能单元/模块可以集成在一个单元/模块中,也可以是各个单元/模块单独物理存在,也可以两个或两个以上单元/模块集成在一起。上述集成的单元/模块既可以采用硬件的形式实现,也可以采用软件程序模块的形式实现。

[0100]

所述集成的单元/模块如果以硬件的形式实现时,该硬件可以是数字电路,模拟电

路等等。硬件结构的物理实现包括但不局限于晶体管,忆阻器等等。若无特别说明,所述人工智能处理器可以是任何适当的硬件处理器,比如cpu、gpu、fpga、dsp和asic等等。若无特别说明,所述存储单元可以是任何适当的磁存储介质或者磁光存储介质,比如,阻变式存储器rram(resistive random access memory)、动态随机存取存储器dram(dynamic random access memory)、静态随机存取存储器sram(static random-access memory)、增强动态随机存取存储器edram(enhanced dynamic random access memory)、高带宽内存hbm(high-bandwidth memory)、混合存储立方hmc(hybrid memory cube)等等。

[0101]

所述集成的单元/模块如果以软件程序模块的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储器中。基于这样的理解,本公开的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储器中,包括若干指令用以使得一台计算机设备(可为个人计算机、服务器或者网络设备等)执行本公开各个实施例所述方法的全部或部分步骤。而前述的存储器包括:u盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

[0102]

在一种可能的实现方式中,还公开了一种人工智能芯片,其包括了上述时钟控制装置。

[0103]

在一种可能的实现方式中,还公开了一种板卡,其包括存储器件、接口装置和控制器件以及上述人工智能芯片;其中,所述人工智能芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;所述存储器件,用于存储数据;所述接口装置,用于实现所述人工智能芯片与外部设备之间的数据传输;所述控制器件,用于对所述人工智能芯片的状态进行监控。

[0104]

图10示出根据本公开实施例的板卡的结构框图,参阅图10,上述板卡除了包括上述芯片389以外,还可以包括其他的配套部件,该配套部件包括但不限于:存储器件390、接口装置391和控制器件392;

[0105]

所述存储器件390与所述人工智能芯片通过总线连接,用于存储数据。所述存储器件可以包括多组存储单元393。每一组所述存储单元与所述人工智能芯片通过总线连接。可以理解,每一组所述存储单元可以是ddr sdram(英文:double data rate sdram,双倍速率同步动态随机存储器)。

[0106]

ddr不需要提高时钟频率就能加倍提高sdram的速度。ddr允许在时钟脉冲的上升沿和下降沿读出数据。ddr的速度是标准sdram的两倍。在一个实施例中,所述存储装置可以包括4组所述存储单元。每一组所述存储单元可以包括多个ddr4颗粒(芯片)。在一个实施例中,所述人工智能芯片内部可以包括4个72位ddr4控制器,上述72位ddr4控制器中64bit用于传输数据,8bit用于ecc校验。可以理解,当每一组所述存储单元中采用ddr4-3200颗粒时,数据传输的理论带宽可达到25600mb/s。

[0107]

在一个实施例中,每一组所述存储单元包括多个并联设置的双倍速率同步动态随机存储器。ddr在一个时钟周期内可以传输两次数据。在所述芯片中设置控制ddr的控制器,用于对每个所述存储单元的数据传输与数据存储的控制。

[0108]

所述接口装置与所述人工智能芯片电连接。所述接口装置用于实现所述人工智能

芯片与外部设备(例如服务器或计算机)之间的数据传输。例如在一个实施例中,所述接口装置可以为标准pcie接口。比如,待处理的数据由服务器通过标准pcie接口传递至所述芯片,实现数据转移。优选的,当采用pcie 3.0x 16接口传输时,理论带宽可达到16000mb/s。在另一个实施例中,所述接口装置还可以是其他的接口,本公开并不限制上述其他的接口的具体表现形式,所述接口单元能够实现转接功能即可。另外,所述人工智能芯片的计算结果仍由所述接口装置传送回外部设备(例如服务器)。

[0109]

所述控制器件与所述人工智能芯片电连接。所述控制器件用于对所述人工智能芯片的状态进行监控。具体的,所述人工智能芯片与所述控制器件可以通过spi接口电连接。所述控制器件可以包括单片机(micro controller unit,mcu)。如所述人工智能芯片可以包括多个处理芯片、多个处理核或多个处理电路,可以带动多个负载。因此,所述人工智能芯片可以处于多负载和轻负载等不同的工作状态。通过所述控制装置可以实现对所述人工智能芯片中多个处理芯片、多个处理和或多个处理电路的工作状态的调控。

[0110]

在一种可能的实现方式中,公开了一种电子设备,其包括了上述人工智能芯片。电子设备包括数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、手机、行车记录仪、导航仪、传感器、摄像头、服务器、云端服务器、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、交通工具、家用电器、和/或医疗设备。所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、b超仪和/或心电图仪。

[0111]

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。上述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0112]

依据以下条款可更好地理解前述内容:

[0113]

条款a1.一种时钟控制装置,应用于处理器,所述装置包括:

[0114]

电压检测模块,用于检测所述处理器中目标位置的供电电压;在所述供电电压小于或等于预设的第一阈值时,输出电压警报信号;

[0115]

时钟展宽模块,连接到所述电压检测模块,用于在接收到所述电压警报信号时,根据与基准频率对应的第一时钟信号,生成第二时钟信号,以使所述处理器采用所述第二时钟信号进行数据处理,

[0116]

其中,所述第二时钟信号的频率低于所述基准频率。

[0117]

条款a2.根据条款a1所述的装置,所述电压检测模块包括第一检测单元,所述第一检测单元包括:

[0118]

脉冲产生电路,输入第五时钟信号,输出脉冲信号;

[0119]

延迟电路,连接到所述脉冲产生电路,输入所述脉冲信号,输出延迟后的脉冲信号,所述延迟后的脉冲信号和所述脉冲信号之间的延迟与所述目标位置的供电电压负相关;

[0120]

电压检测及处理电路,连接到所述延迟电路,用于根据所述延迟后的脉冲信号及所述第五时钟信号,确定所述目标位置的供电电压;在所述供电电压小于或等于第一阈值时,输出第一电压警报信号。

[0121]

条款a3.根据条款a2所述的装置,所述电压检测及处理电路还用于:

[0122]

在输出所述第一电压警报信号期间,当所述供电电压大于或等于预设的第二阈值,且所述供电电压大于或等于第二阈值的持续时间达到预设的第一时长时,输出第一电压正常信号,

[0123]

其中,所述第二阈值大于所述第一阈值。

[0124]

条款a4.根据条款a1所述的装置,所述电压检测模块包括第二检测单元,所述第二检测单元包括:

[0125]

环形振荡电路,用于根据所述目标位置的供电电压,输出第四时钟信号;

[0126]

处理电路,连接到所述环形振荡电路,用于根据所述第四时钟信号确定预设的第二时长内的计数值;在所述计数值小于或等于预设的第一计数阈值时,输出第二电压警报信号。

[0127]

条款a5.根据条款a2或a3所述的装置,所述电压检测模块还包括第二检测单元,所述第二检测单元包括:

[0128]

环形振荡电路,用于根据所述目标位置的供电电压,输出第四时钟信号;

[0129]

处理电路,连接到所述环形振荡电路,用于根据所述第四时钟信号确定预设的第二时长内的计数值;在所述计数值小于或等于预设的第一计数阈值时,输出第二电压警报信号。

[0130]

条款a6.根据条款a5所述的装置,所述处理电路还用于:

[0131]

在输出所述第二电压警报信号期间,当所述计数值大于或等于预设的第二计数阈值,且所述计数值大于或等于所述第二计数阈值的次数达到预设次数时,输出第二电压正常信号;

[0132]

其中,所述第二计数阈值大于所述第一计数阈值。

[0133]

条款a7.根据条款a5或a6所述的装置,所述电压检测模块还包括第一选择单元,连接到所述第一检测单元、所述第二检测单元及所述时钟展宽模块,所述第一选择单元用于:

[0134]

将所述第一检测单元的输出信号或所述第二检测单元的输出信号输出到所述时钟展宽模块。

[0135]

条款a8.根据条款a6所述的装置,所述电压检测模块还包括第二选择单元,连接到所述第一检测单元、所述第二检测单元及所述时钟展宽模块,所述第二选择单元用于:

[0136]

在所述第一检测单元输出第一电压警报信号,和/或所述第二检测单元输出第二电压警报信号时,输出电压警报信号到所述时钟展宽模块;

[0137]

在所述第一检测单元输出第一电压正常信号,且所述第二检测单元输出第二电压正常信号时,输出电压正常信号到所述时钟展宽模块。

[0138]

条款a9.根据条款a1-a8中任意一项所述的装置,所述时钟展宽模块包括:

[0139]

时钟相位生成电路,用于根据所述第一时钟信号,输出多个相位时钟信号;

[0140]

时钟展宽电路,连接到所述时钟相位生成电路,用于在接收到所述电压警报信号时,根据所述多个相位时钟信号,通过门控时钟电路生成所述第二时钟信号。

[0141]

条款a10.根据条款a9所述的装置,所述时钟展宽模块还用于:

[0142]

在接收到电压正常信号时,根据所述第一时钟信号或所述多个相位时钟信号,生成第三时钟信号,以使所述处理器采用所述第三时钟信号进行数据处理,所述第三时钟信

号的频率等于所述基准频率。

[0143]

条款a11、一种人工智能芯片,所述芯片包括如条款a1-a10中任意一项所述的时钟控制装置。

[0144]

条款a12、一种电子设备,所述电子设备包括如条款a11所述的人工智能芯片。

[0145]

条款a13、一种板卡,所述板卡包括:存储器件、接口装置和控制器件以及如条款a11所述的人工智能芯片;

[0146]

其中,所述人工智能芯片与所述存储器件、所述控制器件以及所述接口装置分别连接;

[0147]

所述存储器件,用于存储数据;

[0148]

所述接口装置,用于实现所述人工智能芯片与外部设备之间的数据传输;

[0149]

所述控制器件,用于对所述人工智能芯片的状态进行监控。

[0150]

以上对本公开实施例进行了详细介绍,本文中应用了具体个例对本公开的原理及实施方式进行了阐述,以上实施例的说明仅用于帮助理解本公开的方法及其核心思想。同时,本领域技术人员依据本公开的思想,基于本公开的具体实施方式及应用范围上做出的改变或变形之处,都属于本公开保护的范围。综上所述,本说明书内容不应理解为对本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1