闪存的内存控制器及其控制方法与流程

1.本发明涉及一种闪存的内存控制器及其控制方法,尤其涉及有关于一种可提升错误纠正能力的闪存的内存控制器及其控制方法。

背景技术:

2.在反及式闪存中,一个存储页可以区分为多个存储分节,一个存储分节可以区分为多个存储行,一个存储行内有八个存储位。对应多个存储分节,闪存另提供存储多个备用行来存储错误纠正码。

3.在现有技术领域中,备用行的数量是固定的,且对应执行的错误纠正动作的层级也是固定的。在实际的应用上,存储分节中发生的错误位数可能有一定的数量是来自于损坏存储行。而一个损坏存储行所造成的每一个存储位错误,皆需要14个位的错误纠正码来进行错误纠正动作。在这样的条件下,在当存储分节中发生的错误位数过高时,则可能使错误纠正码不足以进行错误纠正的动作,并降低闪存的数据可靠度。

技术实现要素:

4.本发明是针对一种闪存的内存控制器及其控制方法,可提升错误纠正的能力。

5.根据本发明的实施例,闪存的控制方法包括:检查闪存中多个存储分节分别对应的多个损坏存储行数量;依据每一损坏存储行数量以选择n个备用行来取代对应的每一存储分节中的n个损坏存储行,其中n为不小于0的整数;以及,依据每一损坏存储行数量以调整对应每一存储分节的错误纠正动作的层级。

6.根据本发明的实施例,内存控制器包括核心电路以及错误纠正装置。核心电路在闪存中多个存储分节分别对应的多个损坏存储行数量中,依据每一损坏存储行数量以选择n个备用行来取代对应的每一存储分节中的n个损坏存储行,其中n为不小于0的整数。错误纠正装置耦接闪存,用以依据每一损坏存储行数量以调整对应每一存储分节的错误纠正动作的层级。

7.根据上述,本发明通过利用备用行来取代存储分节中的损坏存储行来降低错误纠正动作所需纠正的位数,再通过动态调整错误纠正动作的层级,以增加错误纠正动作的处理速度。如此一来,内存控制器的错误纠正能力可以有效的被提升。

附图说明

8.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

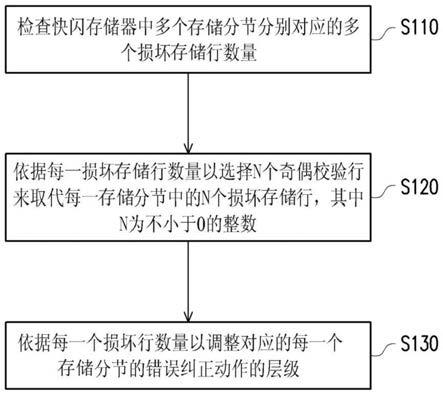

9.图1是根据本发明的实施例的一种闪存的控制方法的流程图;

10.图2a以及图2b是根据本发明实施例的损坏存储行的取代动作的示意图;

11.图3为根据本发明一实施例的内存控制器的示意图;

12.图4是依照本发明实施例的内存控制器的错误纠正装置的实施方式的示意图;

13.图5是根据本发明实施例的内存控制器的错误纠正装置的实施方式的示意图。

14.附图标号说明

15.s110~s130:步骤;

16.sec1、sec1’:存储分节;

17.spc1:备用区;

18.mc1~mca:存储行;

19.sc1~scm:备用行;

20.bb1、bb2、bb3、eb1、eb2:位;

21.dssc:未被选中区;

22.ssc:被选中区;

23.300:内存控制器;

24.301、401:闪存;

25.310、410:核心电路;

26.320:错误纠正装置;

27.411、511、512:计数器;

28.412、521、522:查找表;

29.413、530:错误纠正编译码器;

30.531:编码器;

31.532:译码器;

32.414、541、542:内存。

具体实施方式

33.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

34.图1是依据本发明的实施例的一种闪存的控制方法的流程图。本发明实施例中的闪存可以是反及式(nand)闪存。在步骤s110中,检查闪存中多个存储分节(section)分别对应的多个损坏存储行数量。上述针对闪存的检查动作,可以通过针对闪存的每一存储分节的多个存储行执行写入动作以及写入验证动作。并依据对应每一存储行的写入验证动作,来获知所执行的写入动作是否可以正确完成。当执行写入验证的存储行的写入动作被判断为无法正确完成时,则可以设定此存储行为损坏存储行。

35.在步骤s110中,可针对每一存储分节中的损坏存储行的数量进行统计。对应多个存储分节,则可获得分别对应的多个损坏存储行的数量。

36.在本实施例中,在闪存中,对应多个存储分节,并分别具有多个备用区。其中每一备用区中具有备用行。在步骤s120中,针对每一个存储分节,依据对应的损坏存储行数量来选择备用区中的n个备用行来取代存储分节中的n个损坏存储行。其中n可以为不小于0的整数。

37.在此可参照图2a以及图2b,图2a以及图2b是依据本发明实施例的损坏存储行的取代动作的示意图。在图2a中,存储分节sec1对应备用区spc1。存储分节sec1中具有存储行mc1~mca,备用区spc1中则具有m个备用行sc1~scm。其中,通过步骤s110的检查动作,可以

获知存储分节sec1的存储行mc2以及mc4中分别具有数据错误的位eb1以及eb2,存储分节sec1的存储行mc3以及mca中则分别具有无法被正常写入的位bb1、bb2以及bb3。在此,数据错误的位eb1以及eb2是可通过重新写入来进行数据的更正。无法被正常写入的位bb1、bb2以及bb3则可能发生物理性的错误,并无法被修复。因此,具有无法被正常写入的位bb1、bb2以及bb3的存储行mc3以及mca,可被注记为损坏存储行。且在图2a的范例中,存储分节sec1的损坏存储行的数量为2。

38.在图2b中,备用区spc1中的两个备用行sc1以及sc2,依据存储分节sec1的损坏存储行的数量(=2),被设定为被选中区ssc。被选中区ssc中的备用行sc1以及sc2并用以取代判定为损坏的存储行mc3以及mca,并产生具有新的范围的存储分节sec1’。以每一存储行、每一备用行均记录一个字节的数据为范例,备用行sc1以及sc2用以记录存储分节sec1’中所存储的数据的最后两个字节。

39.在另一方面,未被选中区dssc中的m-2个备用行sc3~scm则用以存储错误纠正码(error correction code,ecc)。

40.举例来说明,以备用行sc1~scm最大可提供个字节为范例,备用行sc1~scm至多可提供以纠正160个字节*8/14=91个错误位。若存储分节sec1中出现100个错误位时,则无法有效纠正所有的错误位。而在本实施例中,以100个错误位中,有20个位属于损坏存储行为范例,备用行sc1~scm的其中20个可被用以取代存储分节sec1中的损坏存储行。如此一来,需纠正的错误位降低为80个,且未被选中区dssc中的备用行则可提供140的字节的错误纠正码。在这样的条件下,未被选中区dssc中的奇备用行所提供的错误纠正码至多可提供140个字节*8/14=80的错误位的纠正动作。也就是说,数据的错误纠正动作可有效的被完成。

41.请重新参照图1,在步骤s130中,依据每一个损坏行数量,来调整对应的每一个存储分节错误纠正动作的层级(level)。

42.在本发明实施例中,在当存储分节中的损坏存储行的数量越多时,用以取代损坏存储行的备用行的数量就会越多。相对的,未被选中的备用行可提供的错误纠正码的数量就会相对的被降低。也因此,对应每一个存储分节的错误纠正动作的层级,需依据每一个存储分节的损坏存储行的数量来进行调整。本发明实施例可针对损坏存储行与错误纠正动作层级信息预先设定一个关系。接着,基于存储分节的损坏存储行的数量,通过设置查找表,来记录多个存储分节与错误纠正动作层级信息的对应关系。

43.也因此,在步骤s130中,可依据目前存取的存储分节,来对查找表执行查找动作,便可获得对应目前存取的存储分节的错误纠正动作层级信息。错误纠正动作层级信息用以设定针对目前存取的存储分节的错误纠正动作的层级(亦即错误纠正位数)。

44.以下请参照图3,图3为依据本发明一实施例的内存控制器的示意图。内存控制器300耦接至闪存301。内存控制器300包括核心电路310以及错误纠正装置320。核心电路310以及错误纠正装置320耦接至闪存301。

45.在本实施例中,核心电路310内存控制器300在对闪存301执行存取动作时,核心电路310可针对被存取的存储分节,以依据存储分节损坏存储行数量中,来选择备用行以取代被存取的存储分节中的一个或多个损坏存储行。错误纠正装置320则用以依据被存取的存储分节的损坏存储行数量来调整对应存储分节的错误纠正动作的层级,并针对所存取的数

据来执行错误纠正的编码或译码动作。

46.在此请注意,关于闪存301的多个存储分节的损坏存储行数量的判断动作,可由另一电子装置(例如闪存的测试机台)来执行,或者也可以由核心电路310来执行。核心电路310或外部电子装置所测得的损坏存储行数量的相关信息可被传入至错误纠正装置320中,并据以建立记录存储分节以及错误纠正动作层级信息间的关系的查找表。

47.关于硬件架构的部分,核心电路310可以为具运算能力的处理器电路。或者,核心电路310可以是通过硬件描述语言(hardware description language,hdl)或是其他任意本领域技术人员所熟知的数字电路的设计方式来进行设计的硬件电路。

48.关于错误纠正装置的实施细节,请参照图4,图4是依照本发明实施例的内存控制器的错误纠正装置的实施方式的示意图。错误纠正装置410耦接至闪存401。错误纠正装置410包括计数器411、查找表412、错误纠正编译码器413以及内存414。在本实施例中,闪存401中的多个存储分节可被设定为多个编码。计数器411则用以产生对应被存取的存储分节的编码的计数值cnt。在本实施例中,多个存储分节可依据编码的顺序,依序被存取。计数器411则可依序产生对应至被存取的存储分节的编码的计数值cnt。在本实施例中,计数器411可应用本领域技术人员和所熟知的任意形式的计数电路来实施,没有特别的限制。

49.查找表412中记录存储分节的编码,与对应的错误纠正动作层级信息ecci的对照关系。在本实施方式中,闪存中401的每一存储分节的损坏存储行的数量已预先被检测出。查找表412可依据每一存储分节的损坏存储行的数量,以及对应被选用的错误纠正动作层级来被建立。查找表412可以由任意形式的内存来建构,没有特定的限制。

50.查找表412可依据所接收的计数值cnt以输出错误纠正动作层级信息ecci。错误纠正动作层级信息ecci可被传送至错误纠正编译码器413。错误纠正编译码器413则可依据错误纠正动作层级信息ecci来设定错误纠正动作的层级来执行编码或译码动作,并针对闪存401的存取数据,进行错误纠正动作。

51.此外,发明实施例中的错误纠正装置410中被设置内存414。内存414可以是随机存取内存,提供错误纠正编译码器413存取所需的数据。

52.请参照图5,图5是依据本发明实施例的内存控制器的错误纠正装置的实施方式的示意图。错误纠正装置500耦接至闪存501。错误纠正装置500包括对应数据写入动作的计数器511、查找表521、编码器531以及内存541,错误纠正装置500另包括对应数据读出动作的计数器512、查找表522、译码器532以及内存542。其中,编码器531与译码器532构成错误纠正编译码器530。

53.计数器511、查找表521、编码器531以及内存541用以针对写入至闪存501的存取存储分节的数据执行错误纠正动作。计数器512、查找表522、译码器532以及内存542则用以针对由闪存501的存取存储分节读出的数据执行错误纠正动作。相关的动作细节与图4的实施方式类似,在此不多赘述。

54.在本实施方式中,查找表521、531可记录相同的内容。计数器511、512则可具有相同的电路架构。内存541、542可以为相同型式的随机存取内存。

55.根据上述,本发明利用备用行来取代存储分节中的损坏存储行来降低错误纠正动作所需纠正的位数。并且,对应损坏存储行的数量来调整错误纠正动作的层级。如此一来,内存控制器的错误纠正能力可以有效的被提升。

56.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1