一种兼容万兆千兆网卡的计算机、千兆网卡以及万兆网卡的制作方法

[0001]

本发明涉及一种兼容万兆千兆网卡的计算机、千兆网卡以及万兆网卡。

背景技术:

[0002]

随着用户应用对链路带宽和性能的要求越来越高,万兆以太网技术以其优异的性能,逐渐替代千兆以太网在网络互连中的地位。在消费升级时代,产品需求轻薄,简洁,但是传统标准的千兆网卡和万兆网卡采用pcie插槽与计算机互连,体积大,成本较高,集成度较低,影响整机密度,而且对安装要求高,布局不太方便,物理限制较多,不符合产品轻薄化,简洁化需求。

技术实现要素:

[0003]

本发明要解决的技术问题,在于提供一种兼容万兆千兆网卡的计算机、千兆网卡以及万兆网卡,采用fpc接口的网卡更小,布局灵活,安装方便,更利于工业设计发挥,设计出更美观的产品,节约成本,符合产品轻薄化,简洁化需求,同时可以兼容千兆网卡,提高产品适用性。

[0004]

本发明之一是这样实现的:一种兼容万兆千兆网卡的计算机,包括一fpc接口,

[0005]

所述fpc接口上设有4个引脚,若连接万兆网卡则连接+12v供电;若连接千兆网卡,则为空闲引脚;

[0006]

所述fpc接口上设有3个用于连接+3.3v供电引脚;

[0007]

所述fpc接口上分别设有用于连接lanwakeb信号、perstb信号以及时钟差分对信号的引脚;

[0008]

所述fpc接口上设有四组用于连接pcie tx、rx差分对信号的引脚,每组设有四个引脚;

[0009]

所述fpc接口上设有一引脚,若连接万兆网卡,则为空闲;若连接千兆网卡,则为clkreqb信号。

[0010]

进一步地,所述fpc接口上还设有四个引脚,所述四个引脚均为接地,所述四个引脚将四组pcie tx、rx差分对信号的引脚进行间隔。

[0011]

本发明之二是这样实现的:一种采用fpc接口的万兆网卡,用于与计算机主板连接,包括fpc接口、万兆网卡芯片以及万兆rj45接口,所述万兆网卡芯片分别连接所述fpc接口以及万兆rj45接口,所述fpc接口通过fpc柔性电路板连接至计算机主板;

[0012]

所述fpc接口上设有4个连接万兆网卡芯片+12v供电引脚;

[0013]

所述fpc接口设有三个连接万兆网卡芯片+3.3v供电引脚,

[0014]

所述fpc接口分别设有接lanwakeb信号以及perstb信号的引脚;

[0015]

所述fpc接口分别设有接时钟差分对信号pcie_clk_p和pcie_clk_n的引脚;

[0016]

所述fpc接口上设有四组用于连接pcie tx、rx差分对信号的引脚,每组设有四个引脚;

[0017]

进一步地,所述fpc接口上还设有四个引脚,所述四个引脚均为接地,所述四个引脚将四组pcie tx、rx差分对信号的引脚进行间隔。

[0018]

本发明之三是这样实现的:一种采用fpc接口的千兆网卡,用于与计算机主板连接,包括fpc接口、千兆网卡芯片以及千兆rj45接口,所述千兆网卡芯片分别连接所述fpc接口以及千兆rj45接口,所述fpc接口通过fpc柔性电路板连接至计算机主板;

[0019]

所述fpc接口上设有三个千兆网卡+3.3v供电引脚;

[0020]

所述fpc接口上分别设有接lanwakeb信号、perstb信号以及clkreqb信号的引脚

[0021]

所述fpc接口上分别设有接时钟差分对信号pcie_clk_p和pcie_clk_n的引脚;

[0022]

所述fpc接口上分别设有一组pcie tx、rx差分对信号的引脚。

[0023]

进一步地,所述fpc接口上还设有2个引脚,所述2个引脚均为接地,所述2个引脚将一组pcie tx、rx差分对信号的引脚与其他引脚进行间隔。

[0024]

本发明的优点在于:

[0025]

1、本发明采用fpc接口,通过fpc印制电路板实现万兆网卡和计算机互连,相比于标准的万兆网卡金手指方案,降低了成本,给计算机万兆网卡布局提供了灵活的选择,有效提升了整机系统布局的灵活性,有利于产品工业设计,有利于产品的轻薄化、简洁化需求;

[0026]

2、本发明的fpc接口信号定义与千兆网卡接口信号定义兼容,并与计算机主板fpc接口构成完整的系统,提高产品兼容性,同一主板可以灵活配置千兆网卡或者万兆网卡,降低主板改板造成的资源浪费。

附图说明

[0027]

下面参照附图结合实施例对本发明作进一步的说明。

[0028]

图1是本发明一种采用fpc接口的万兆网卡的示意图。

[0029]

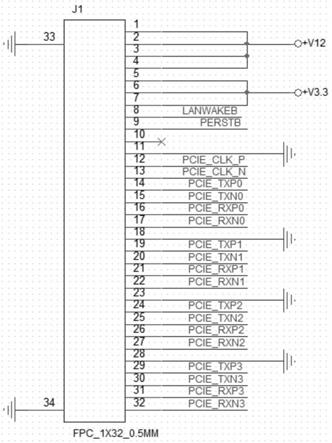

图2是本发明万兆网卡fpc接口设计示意图。

[0030]

图3是本发明千兆网卡fpc接口设计示意图。

具体实施方式

[0031]

本发明解决了传统标准的千兆网卡和万兆网卡采用pcie插槽与计算机互连,体积大,成本较高,集成度较低,影响整机密度,而且对安装要求高,布局不太方便,物理限制较多,不符合产品轻薄化,简洁化需求;使得采用fpc接口的网卡更小,布局灵活,安装方便,更利于工业设计发挥,设计出更美观的产品,节约成本,符合产品轻薄化,简洁化需求,同时可以兼容千兆网卡,提高产品适用性。

[0032]

1、如图1所示,一种采用fpc接口的万兆网卡,包括fpc接口、万兆网卡芯片模块和万兆rj45接口,所述fpc接口通过fpc柔性电路板连接至计算机主板,所述计算机主板上设有相同的fpc接口。

[0033]

2、如图2所示,为万兆网卡fpc接口设计,j1为万兆网卡fpc接口座,1pin-5pin是万兆网卡+12v供电引脚,5pin-7pin是万兆网卡+3.3v供电引脚,8pin接lanwakeb信号,9pin接perstb信号,10pin空闲,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_n。14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。19pin-22pin分别接第1组pcie tx、rx差分对信号

pcie_txp1、pcie_txn1、pcie_txp1和pcie_txn1。24pin-27pin分别接第2组pcie tx、rx差分对信号pcie_txp2、pcie_txn2、pcie_txp2和pcie_txn2。29pin-32pin分别接第3组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。

[0034]

3、如图3所示,为千兆网卡fpc接口设计,j2为千兆网卡fpc接口座,5pin-7pin是千兆网卡+3.3v供电引脚,8pin接lanwakeb信号,9pin接perstb信号,10pin接clkreqb信号,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_n。千兆网卡fpc接口的pcie tx、rx信号与万兆网卡fpc接口4对pcie tx、rx信号中的任意一对相对应,本实施例采用14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。剩余引脚空闲。

[0035]

4、如表1所示,为计算机主板fpc接口、万兆网卡fpc接口以及千兆网卡fpc接口各个信号引脚定义。计算机主板fpc接口包含1组时钟加4组pcie tx、rx差分信号,以及lanwakeb、clkreqb和perstb信号组成,并需要若干电源和地信号,其中+3.3v为网卡模块主供电源,+12v为输入电压,可通过电源模块转换为网卡模块需要的其他供电电压。接万兆网卡时,clkreqb信号空闲,其他引脚信号定义与计算机主板fpc接口一致。接千兆网卡时,仅需要1组pcie tx、rx差分信号,接4组pcie tx、rx差分信号中的任意一组即可,剩下三组未接的pcie tx、rx差分信号空闲,+12v信号空闲,其他引脚信号定义与计算机主板fpc接口一致。本实施例仅展示一种信号引脚的线序,只要保证计算机主板fpc接口、万兆网卡fpc接口以及千兆网卡fpc接口每个信号定义相对应,改变信号引脚的顺序,仍应当落入该发明的保护范围内。通过该定义方式,实现万兆网卡fpc接口和千兆网卡fpc接口兼容应用,可以自由搭配万兆网卡或千兆网卡,无需计算机主板改板。

[0036]

[0037][0038]

表1

[0039]

实施例一

[0040]

本实施例提供一种兼容万兆千兆网卡的计算机,包括一fpc接口,

[0041]

所述fpc接口上设有4个引脚,若连接万兆网卡则连接+12v供电;若连接千兆网卡,则为空闲引脚;

[0042]

所述fpc接口上设有3个用于连接+3.3v供电引脚;

[0043]

所述fpc接口上分别设有用于连接lanwakeb信号、perstb信号以及时钟差分对信号的引脚;

[0044]

所述fpc接口上设有四组用于连接pcie tx、rx差分对信号的引脚,每组设有四个引脚;

[0045]

所述fpc接口上设有一引脚,若连接万兆网卡,则为空闲;若连接千兆网卡,则为clkreqb信号。

[0046]

所述fpc接口上还设有四个引脚,所述四个引脚均为接地,所述四个引脚将四组pcie tx、rx差分对信号的引脚进行间隔。

[0047]

当连接万兆网卡时,其引脚定义为:1pin-5pin是万兆网卡+12v供电引脚,5pin-7pin是万兆网卡+3.3v供电引脚,8pin接lanwakeb信号,9pin接perstb信号,10pin空闲,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_n。14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。19pin-22pin分别接第1组pcie tx、rx差分对信号pcie_txp1、pcie_txn1、pcie_txp1和pcie_txn1。24pin-27pin分别接第2组pcie tx、rx差分对信号pcie_txp2、pcie_txn2、pcie_txp2和pcie_txn2。29pin-32pin分别接第3组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。

[0048]

当连接千兆网卡是,其引脚定义为:5pin-7pin是千兆网卡+3.3v供电引脚,8pin接

lanwakeb信号,9pin接perstb信号,10pin接clkreqb信号,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_n。千兆网卡fpc接口的pcie tx、rx信号与万兆网卡fpc接口4对pcie tx、rx信号中的任意一对相对应,本实施例采用14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。剩余引脚空闲。

[0049]

实施例二

[0050]

本实施例提供一种采用fpc接口的万兆网卡,用于与计算机主板连接,包括fpc接口、万兆网卡芯片以及万兆rj45接口,所述万兆网卡芯片分别连接所述fpc接口以及万兆rj45接口,所述fpc接口通过fpc柔性电路板连接至计算机主板;

[0051]

所述fpc接口上设有4个连接万兆网卡芯片+12v供电引脚;

[0052]

所述fpc接口设有三个连接万兆网卡芯片+3.3v供电引脚,

[0053]

所述fpc接口分别设有接lanwakeb信号以及perstb信号的引脚;

[0054]

所述fpc接口分别设有接时钟差分对信号pcie_clk_p和pcie_clk_n的引脚;

[0055]

所述fpc接口上设有四组用于连接pcie tx、rx差分对信号的引脚,每组设有四个引脚;

[0056]

所述fpc接口上还设有四个引脚,所述四个引脚均为接地,所述四个引脚将四组pcie tx、rx差分对信号的引脚进行间隔。

[0057]

如图2所示,为万兆网卡fpc接口设计,j1为万兆网卡fpc接口座,1pin-5pin是万兆网卡+12v供电引脚,5pin-7pin是万兆网卡+3.3v供电引脚,8pin接lanwakeb信号,9pin接perstb信号,10pin空闲,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_n。14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。19pin-22pin分别接第1组pcie tx、rx差分对信号pcie_txp1、pcie_txn1、pcie_txp1和pcie_txn1。24pin-27pin分别接第2组pcie tx、rx差分对信号pcie_txp2、pcie_txn2、pcie_txp2和pcie_txn2。29pin-32pin分别接第3组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。所述33pin和34pin为固定焊点。

[0058]

实施例三

[0059]

本实施例提供一种采用fpc接口的千兆网卡,用于与计算机主板连接,包括fpc接口、千兆网卡芯片以及千兆rj45接口,所述千兆网卡芯片分别连接所述fpc接口以及千兆rj45接口,所述fpc接口通过fpc柔性电路板连接至计算机主板;

[0060]

所述fpc接口上设有三个千兆网卡+3.3v供电引脚;

[0061]

所述fpc接口上分别设有接lanwakeb信号、perstb信号以及clkreqb信号的引脚

[0062]

所述fpc接口上分别设有接时钟差分对信号pcie_clk_p和pcie_clk_n的引脚;

[0063]

所述fpc接口上分别设有一组pcie tx、rx差分对信号的引脚。

[0064]

所述fpc接口上还设有2个引脚,所述2个引脚均为接地,所述2个引脚将一组pcie tx、rx差分对信号的引脚与其他引脚进行间隔。

[0065]

如图3所示,为千兆网卡fpc接口设计,j2为千兆网卡fpc接口座,5pin-7pin是千兆网卡+3.3v供电引脚,8pin接lanwakeb信号,9pin接perstb信号,10pin接clkreqb信号,11pin、18pin、23pin、28pin接地,12pin和13pin接时钟差分对信号pcie_clk_p和pcie_clk_

n。千兆网卡fpc接口的pcie tx、rx信号与万兆网卡fpc接口4对pcie tx、rx信号中的任意一对相对应,本实施例采用14pin-17pin分别接第0组pcie tx、rx差分对信号pcie_txp0、pcie_txn0、pcie_txp0和pcie_txn0。剩余引脚空闲。所述33pin和34pin为固定焊点。

[0066]

虽然以上描述了本发明的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本发明的范围的限定,熟悉本领域的技术人员在依照本发明的精神所作的等效的修饰以及变化,都应当涵盖在本发明的权利要求所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1