一种检测VR异常掉电定位功能自动化测试方法与系统与流程

一种检测vr异常掉电定位功能自动化测试方法与系统

技术领域

1.本发明涉及服务器测试技术领域,特别是一种检测vr异常掉电定位功能自动化测试方法与系统。

背景技术:

2.在服务器日常使用及测试时,会出现某一路vr输出有问题,但是服务器供电vr几十组,不方便快速定位问题所在。后来服务器添加了一种vr异常掉电定位功能,即某一路vr异常掉电后,通过bmc芯片日志可以读取异常掉电报警日志,可以报出异常掉电vr的错误码,这样可以帮助快速定位出故障vr。

3.该vr异常掉电定位功能的原理是:cpld芯片检测每一路vr的pg信号,当某一路vr的pg信号出现由高到低的动作时,cpld芯片会将该信号发送给bmc芯片,bmc芯片会发出报警日志。每个vr都有特定的错误码,根据报警日志的错误码可快速定位故障位置。

4.但是,vr异常掉电定位功能需要cpld芯片、错误码以及bmc芯片报警功能三个方面合作才能完成,任何一方面出现问题,都会导致vr异常掉电定位功能异常,这就不能很好的定位故障位置。

5.因此,为了确保该vr异常掉电定位功能的准确性,需要测试该vr异常掉电定位功能。现有的测试方法基本分为两种:

6.将vr进行scp保护操作,需要将被测vr的输出焊接出负载线连接到电子负载仪上,对于大电流需要焊接较粗的负载线,需要焊接,操作繁琐,而且增大坏板的几率;

7.选取vr上的en引脚,用镊子将其短路,需要找所有vr的en位置,用镊子对地短路,针对四路服务器,会有40多组vr需要该功能的测试,操作风险较高,且手持镊子有烫伤风险,操作不当会将cpld芯片烧坏。

技术实现要素:

8.本发明的目的是提供一种检测vr异常掉电定位功能自动化测试方法与系统,旨在解决现有技术中vr异常掉电定位功能测试中存在操作繁琐且风险性高的问题,实现。

9.为达到上述技术目的,本发明提供了一种检测vr异常掉电定位功能自动化测试方法,所述方法包括以下操作:

10.根据vr依次上电的时序制定时序表格,并填入相应的错误码,导入pc控制器中,根据时序表格进行顺序掉电测试;

11.pc控制器根据时序表格发送掉电信号至cpld芯片,cpld芯片控制vr的en信号由高电平变为低电平,模拟异常掉电;

12.cpld监测到vr的pg信号由高电平变为低电平时,将变化信息发送至bmc芯片,bmc芯片上报含有错误码的报警日志;

13.pc控制器根据报警日志中的错误码,时序表格中的错误码进行对比,获得测试结果。

14.优选地,所述时序表格还存储在数据库中。

15.优选地,当cpld芯片检测到所有pg信号均上电后,将信号发送至bmc芯片,bmc芯片发送报警解除日志。

16.优选地,所述pc控制器接收到报警解除日志后,根据时序表格判断是否为最后一组vr,若不是则按照时序表格进行下一组vr的掉电测试,若是则结束测试。

17.本发明还提供了一种检测vr异常掉电定位功能自动化测试系统,所述系统包括:

18.pc控制器、bmc芯片、cpld芯片以及被测服务器;

19.所述pc控制器与bmc芯片连接,bmc芯片与cpld芯片连接,cpld芯片连接被测服务器;

20.pc控制器根据时序表格发送掉电信号至cpld芯片,cpld芯片控制vr的en信号由高电平变为低电平,当cpld监测到vr的pg信号由高电平变为低电平时,将变化信息发送至bmc芯片,bmc芯片上报含有错误码的报警日志,所述pc控制器比对错误码,获得测试结果。

21.优选地,所述pc控制器与bmc芯片之间通过usb

‑

usb线缆连接。

22.优选地,所述bmc芯片与cpld芯片之间以及cpld芯片与被测服务器之间均通过i2c通信。

23.优选地,所述时序表格还存储在数据库中。

24.发明内容中提供的效果仅仅是实施例的效果,而不是发明所有的全部效果,上述技术方案中的一个技术方案具有如下优点或有益效果:

25.与现有技术相比,本发明通过在控制器中导入时序表格,根据时序表格进行顺序掉电测试,通过cpld控制被测vr的en由高电平转为低电平,模拟异常掉电,bmc由此发出报警日志,控制器根据报警日志的错误码与时序表格的错误码进行对比,从而实现vr异常掉电定位的测试。本发明完全实现了自动化测试,不需要做焊接、寻找位置以及手动短路等操作,可有效提高vr异常掉电定位功能的测试效率,且不会对服务器进行破坏操作,降低坏板风险。

附图说明

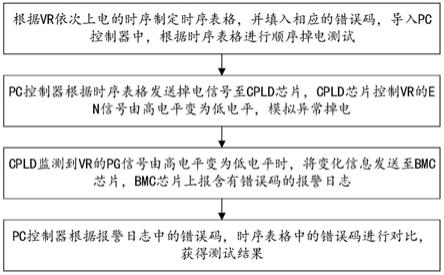

26.图1为本发明实施例中所提供的一种检测vr异常掉电定位功能自动化测试方法流程图;

27.图2为本发明实施例中所提供的一种检测vr异常掉电定位功能自动化测试系统框图。

具体实施方式

28.为了能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

29.下面结合附图对本发明实施例所提供的一种检测vr异常掉电定位功能自动化测

试方法与系统进行详细说明。

30.如图1所示,本发明公开了一种检测vr异常掉电定位功能自动化测试方法,所述方法包括以下操作:

31.根据vr依次上电的时序制定时序表格,并填入相应的错误码,导入pc控制器中,根据时序表格进行顺序掉电测试;

32.pc控制器根据时序表格发送掉电信号至cpld芯片,cpld芯片控制vr的en信号由高电平变为低电平,模拟异常掉电;

33.cpld监测到vr的pg信号由高电平变为低电平时,将变化信息发送至bmc芯片,bmc芯片上报含有错误码的报警日志;

34.pc控制器根据报警日志中的错误码,时序表格中的错误码进行对比,获得测试结果。

35.vr具有两个信号,一个是en信号,即芯片的使能芯片,控制芯片上下电,一般高电平有效;另一个是pg信号,用来检测vr正常输出状态,vr正常输出时,pg信号成高电平状态。

36.本发明实施例通过cpld芯片检测每一路vr的pg信号,当某一路vr的pg信号出现由高电平到低电平动作时,cpld芯片将该信号发送至bmc芯片,bmc芯片发出报警日志,由于每个vr都有特定的错误码,根据报警日志的错误码即可快速定位故障位置。

37.pc控制器通过usb

‑

usb线缆连接bmc芯片,可显示bmc的报警日志,也可编辑命令或根据时序表格发送命令给bmc芯片,bmc芯片发送给cpld芯片,使被测vr的en由高电平变为低电平,模拟异常掉电。测试哪一路电就可以发送相应的命令码,不需要查看线路图查找焊接负载线的位置,不需要焊接操作,也不需要查看线路图查找en信号测试点。

38.服务器的时序有先后顺序,将相应的错误码填入制定好的时序表格,之后导入pc控制器,根据该时序表格进行顺序掉电测试,并将时序表格存入数据库中。

39.pc控制器给bmc芯片发送pvccin en掉电信号给cpld芯片,cpld芯片控制pvccin的vr的en信号掉电,模拟pvccin的输出异常掉电,pvccin的pg信号掉电。

40.vr芯片异常掉电后,cpld芯片监测倒vr的pg信号由高电平变为低电平,将该变化信息发送给bmc芯片,bmc芯片报出报警日志,pc控制器将测试结果与数据库中的时序表格的错误码进行对比,得出失败与通过结果。

41.pc控制器对服务器进行软启操作,bmc芯片会发出报警解除日志,并根据时序表格判断是否为最后一组vr,如果不是则按照时序表格进行下一组vr的掉电测试,如果是则结束测试。

42.本发明实施例通过在控制器中导入时序表格,根据时序表格进行顺序掉电测试,通过cpld控制被测vr的en由高电平转为低电平,模拟异常掉电,bmc由此发出报警日志,控制器根据报警日志的错误码与时序表格的错误码进行对比,从而实现vr异常掉电定位的测试。本发明完全实现了自动化测试,不需要做焊接、寻找位置以及手动短路等操作,可有效提高vr异常掉电定位功能的测试效率,且不会对服务器进行破坏操作,降低坏板风险。

43.如图2所示,本发明实施例还公开了一种检测vr异常掉电定位功能自动化测试系统,所述系统包括:

44.pc控制器、bmc芯片、cpld芯片以及被测服务器;

45.所述pc控制器与bmc芯片连接,bmc芯片与cpld芯片连接,cpld芯片连接被测服务

器;

46.pc控制器根据时序表格发送掉电信号至cpld芯片,cpld芯片控制vr的en信号由高电平变为低电平,当cpld监测到vr的pg信号由高电平变为低电平时,将变化信息发送至bmc芯片,bmc芯片上报含有错误码的报警日志,所述pc控制器比对错误码,获得测试结果。

47.pc控制器通过usb

‑

usb线缆连接bmc芯片,可显示bmc的报警日志,也可编辑命令或根据时序表格发送命令给bmc芯片,bmc芯片发送给cpld芯片,使被测vr的en由高电平变为低电平,模拟异常掉电。测试哪一路电就可以发送相应的命令码,不需要查看线路图查找焊接负载线的位置,不需要焊接操作,也不需要查看线路图查找en信号测试点。

48.服务器的时序有先后顺序,将相应的错误码填入制定好的时序表格,之后导入pc控制器,根据该时序表格进行顺序掉电测试,并将时序表格存入数据库中。

49.pc控制器给bmc芯片发送pvccinen掉电信号给cpld芯片,cpld芯片控制pvccin的vr的en信号掉电,模拟pvccin的输出异常掉电,pvccin的pg信号掉电。

50.vr芯片异常掉电后,cpld芯片监测倒vr的pg信号由高电平变为低电平,将该变化信息发送给bmc芯片,bmc芯片报出报警日志,pc控制器将测试结果与数据库中的时序表格的错误码进行对比,得出失败与通过结果。

51.pc控制器对服务器进行软启操作,bmc芯片会发出报警解除日志,并根据时序表格判断是否为最后一组vr,如果不是则按照时序表格进行下一组vr的掉电测试,如果是则结束测试。

52.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1