一种基于RISCV的随机指令生成平台及方法与流程

一种基于riscv的随机指令生成平台及方法

技术领域

1.本发明属于集成电路设计技术领域,具体涉及一种基于riscv的随机指令生成平台及方法。

背景技术:

2.随机指令生成技术最早用于快速高效验证处理器,随着集成电路工艺的发展,芯片的规模越来越大,需要引入随机指令生成器生成指令来应对越来越复杂的处理器结构和种类繁多的指令集。随机指令生成技术通过生成随机化指令,在保证cpu性能的前提下,产生更科学的随机化指令,提高验证的速度和覆盖率。

3.目前的随机指令生成技术大多采用简单的随机指令生成或者针对特定的处理器设计,可复用性和覆盖率都不足,难以提高验证覆盖率,因此亟需研发一种基于riscv的随机指令生成平台及方法来解决上述问题。

技术实现要素:

4.针对现有技术的不足,本发明提供了一种基于riscv的随机指令生成平台及方法,以解决现有的随机指令生成技术可复用性和覆盖率不足的问题,提高验证效率。

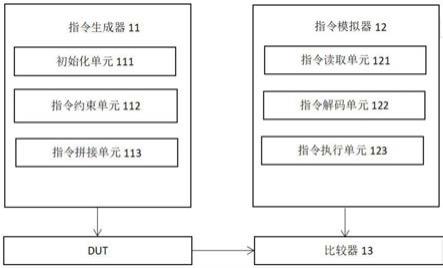

5.本发明通过以下技术方案予以实现:一种基于riscv的随机指令生成平台,能够生成随机化指令进行验证,该生成平台包括:指令生成器模块,用于初始化平台,添加约束并随机、拼接形成指令,将生成的指令输入dut中;指令模拟器模块,用于读取指令,将指令解码,然后执行指令;比较器模块,比较dut与指令模拟器输出的结果。

6.优选的,所述指令生成器模块包括初始化单元、指令约束单元和指令拼接单元。

7.优选的,所述指令模拟器模块包括指令读取单元、指令解码单元和指令执行单元。

8.优选的,所述指令约束单元包含基于riscv指令规则约束和基于流水线的规则约束。

9.优选的,所述指令拼接单元包括单条指令拼接模块和程序拼接模块,分别根据riscv指令生成规则和riscv程序规则生成指令和程序。

10.一种包含上述所述的随机指令生成的实现方法,包括如下步骤:步骤1、搭建基于uvm的随机指令生成平台,在generate类中生成随机指令;步骤2、指令生成器模块将指令进行分类;步骤3、指令生成模块器根据指令布局生成操作码、操作数、格式类型;步骤4、指令生成器模块根据riscv指令规则拼接形成合法指令;步骤5、指令生成器模块构建具体场景,根据程序规则拼接步骤4中生成的riscv指令形成合法程序。

11.优选的,所述步骤2中的指令进行分类时,具体包括alu指令、分支跳转指令、存储指令、控制指令和浮点运算指令。

12.优选的,所述步骤5中的具体场景,程序规则遵循流水线中存在的结构相关冲突,具体的包括alu冲突、访存冲突、数据相关冲突和转移指令冲突。

13.优选的,所述步骤5中的程序规则,具体包括约束乘除法之间周期、约束取指指令与取操作数指令之间的周期、约束取操作数与写寄存器之间周期金和构建包含循环的完整程序的方式。

14.本发明的有益效果为:所述指令生成器模块采用uvm平台搭建,对riscv指令的各个部分进行约束并随机化,根据指令规则进行拼接形成单条指令,然后根据程序规则拼接形成完成程序,将程序输入dut中,所示指令模拟器读取指令生成器产生的程序指令,进行解码并指行,所述比较器比较dut的结果与指令模拟器的仿真结果;本发明的基于riscv的随机指令生成平台能够根据需求对指令的数量、类型、复杂度、权重进行配置,生成符合条件的随机指令,然后根据程序规则拼接形成完成程序,通过指令模拟器对随机指令进行仿真,最后进行比较,相比于现有的随机指令生成方法,可复用性和覆盖率更高,验证效率更快。

附图说明

15.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

16.图1是本发明提供的基于riscv的随机指令生成平台的示意图;图2是本发明提供的指令约束单元的结构示意图。

具体实施方式

17.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

18.实施例一:请参阅图1所示:本实施例一具体提供了一种基于riscv的随机指令生成平台,能够生成随机化指令,其结构示意图如图1所示,该生成平台包括指令生成器11模块、指令模拟器12模块、比较器13模块,其中指令生成器11模块,用于初始化平台,添加约束并随机、拼接形成指令,将生成的指令输入dut中;指令模拟器12模块,用于读取指令,将指令解码,然后执行指令;比较器13模块,用于比较dut与指令模拟器12的结果;具体的,指令生成器11模块包括初始化单元111、指令约束单元112和指令拼接单元113;指令模拟器模块包括指令读取单元121、指令解码单元122和指令执行单元123;具体的,指令生成器11模块将指令分成alu指令、分支跳转指令、存储指令、控制指

令和浮点运算指令,每种指令有对应的操作码、操作数、格式类型,对操作码、操作数、格式类型进行约束,生成随机指令,指令拼接单元将分别拼接成对应的完整指令。

19.具体的,指令生成器11模块将根据权重生成不同数量的main函数指令,子函数指令,中断处理函数指令,程序初始化指令,指令拼接单元根据完整的程序生成规则拼接形成一个能运行的完整程序。

20.具体的,程序规则主要遵循如下:考虑流水线中存在的复杂问题,包括结构相关冲突,具体的包括alu冲突,访存冲突,数据相关冲突,转移指令冲突。

21.具体的,针对存在的结构相关冲突,其中alu冲突和访存冲突,采用约束乘除法之间周期的方法,防止资源冲突来解决alu冲突,采用约束取指指令与取操作数指令之间的周期来解决访存冲突。

22.具体的,针对数据相关冲突,采用约束取操作数与写寄存器之间周期的方式解决数据相关冲突。

23.具体的,针对转移指令冲突,需要构建包含循环的完整程序,对于普通循环,需要包含进入循环与出循环,当调用子函数的时候,需要约束返回值,与恢复现场的指令,对于多层嵌套循环,需要约束返回地址的最大值。

24.指令生成器11模块采用uvm平台搭建,对riscv指令的各个部分进行约束并随机化,根据指令规则进行拼接形成单条指令,然后根据程序规则拼接形成完成程序,将程序输入dut中,所示指令模拟器12读取指令生成器11产生的程序指令,进行解码并指行,比较器13比较dut的结果与指令模拟器12的仿真结果。本发明的基于riscv的随机指令生成平台能够对riscv指令的各个部分进行约束并随机化,根据指令规则进行拼接形成单条指令,然后根据程序规则拼接形成完成程序,通过指令模拟器12对随机指令进行仿真,最后进行比较。

25.请继续参阅图2所示:基于实施例一的基础上,本发明还提供了指令约束单元的结构,其结构示意图如图2所示,指令约束单元112模块包含基类baseic.sv21、历史寄存器类history_reg.sv22、sv类库23,其中基类baseic.sv21包含r型指令24、i型指令25、s型指令26、b型指令27、u型指令28、j型指令29、constr_file类210、generator类211和global_define类212。

26.具体的,指令约束单元112模块分为约束模块和控制模块,其中基类baseic.sv21定义了所有指令的基类,包含了riscv的所有基本指令,所有子类继承于基类,包含了约束的一般场景。

27.具体的,在随机化指令时,首先对r型指令24、i型指令25、s型指令26、b型指令27、u型指令28、j型指令29六种基本指令进行约束并随机,配置调整6种指令的权重,数量,其次对每种指令的寄存器251、操作码252、功能码253的数量、权重进行约束并随机化,生成随机指令。

28.具体的,r型指令24包含寄存器241,操作码242和功能码243三种类型,i型指令25包含寄存器251、操作码252、功能码253和立即数254四种类型,s型指令26包含寄存器261、操作码262、功能码263和立即数264四种类型,b型指令27包含寄存器271、操作码272、功能码273和立即数274四种类型,u型指令28包含操作码281、寄存器282和立即数283三种类型,j型指令29包含操作码291、寄存器292和立即数293三种类型,每种类型的数量,长度都根据对应的riscv指令类型进行约束。

29.具体的,通过历史寄存器类history_reg.sv22记录每一指令周期用到的寄存器,为解决流水线中的复杂问题做准备。

30.具体的,通过sv类库23调用sv类库,对基类进行约束。

31.具体的,通过constr_file类210读取riscv指令的约束信息。

32.具体的,通过generator类211产生激励,例化子类的句柄,根据约束条件产生对应的随机结果。

33.具体的,通过global_define类212进行全局参数的设置,进行各种宏定义。

34.本发明的基于riscv的随机指令生成平台能够根据需求对指令的数量、类型、复杂度、权重进行配置,生成符合条件的随机指令,然后根据程序规则拼接形成完成程序,通过指令模拟器对随机指令进行仿真,最后进行比较,相比于现有的随机指令生成方法,可复用性和覆盖率更高,验证效率更快。

35.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1