一种DDR4内存条及其拓扑结构的制作方法

一种ddr4内存条及其拓扑结构

技术领域

1.本实用新型涉及一内存条,尤其涉及一种ddr4内存条及其拓扑结构。

背景技术:

2.随着技术的发展和各行业的需求的提升,现阶段芯片对于ddr的存储容量和速率的要求都越来越高,对于pcb设计的要求也越来越高。内存条既要满足芯片和ddr颗粒的间距要求,也要使信号质量尽可能的达到最好。

3.要使内存条的pcb具有良好的性能,pcb整体空间的布局、利用率和整个通道的走线长度都有需要严格的管控。

4.如图1所示的传统t型结构,ddr_a芯片和ddr_b芯片分别是top和 bottom面叠在一起摆放的。但是这种t型结构一旦要接入ecc芯片时,由于 ecc芯片的存在导致颗粒的结构不对称,信号的质量始终无法提升到足够的高度。而且在布局的时候端接电阻的摆放位置以及相应的上下拉电源也会成为一个比较难解决的问题。

5.如图2所示的是fly-by的走线拓扑,这种拓扑结构在ddr的走线方式中也是很常见的,但是这种结构一旦用到ddr4内存条中,无法做到读写平衡,所以这种走线方式也没有办法使用。

技术实现要素:

6.本实用新型的一个目的在于提供一种ddr4内存条及其拓扑结构,其中所述ddr4内存条包括一ddr4拓扑结构,其中所述ddr4拓扑结构包括ecc芯片,且符合正规的fly-by拓扑结构的形式。

7.本实用新型的一个目的在于提供一种ddr4内存条及其拓扑结构,其中所述ddr4内存条的所述ddr4拓扑结构使ddr的电源分割变的更容易。

8.本实用新型的一个目的在于提供一种ddr4内存条及其拓扑结构,其中所述ddr4拓扑结构包括至少一芯片组和至少一cpu,其中所述芯片组被电连接于所述cpu,其中所述芯片通过水平错开叠置的方式摆放,并且cpu到每个芯片组中的芯片的走线长度相等,这样不仅能够提高所述ddr4内存条的运行速率及稳定性,还兼具有较小的空间占有率。

9.本实用新型的一个目的在于提供一种ddr4内存条及其拓扑结构,其中所述ddr4内存条具有良好的整个通道运行稳定性。

10.为实现本实用新型以上至少一个目的,本实用新型提供一种ddr4拓扑结构,其中所述ddr4拓扑结构包括:

11.一cpu;和

12.至少一个用于拓扑结构的芯片组件,每组所述用于拓扑结构的芯片组件包括 8个ddr芯片和一ddr_ecc芯片,8个所述ddr芯片和所述ddr_ecc芯片通过水平错开叠置的方式摆放,其中8个所述ddr芯片以及所述ddr_ecc芯片串联且被电连接于所述cpu。

13.根据本实用新型一实施例,8个所述ddr芯片以及所述ddr_ecc芯片走线等长地连

接于所述cpu。

14.根据本实用新型一实施例,所述ddr4拓扑结构包括四个所述用于拓扑结构的芯片组件。

15.根据本实用新型一实施例,相邻两个芯片之间形成一散热空间。

16.根据本实用新型一实施例,所述ddr4拓扑结构还包括至少一去耦电容,至少一个所述去耦电容400被电连接于一个所述用于拓扑结构的芯片组件的一个所述ddr芯片。

17.根据本实用新型一实施例,每组所述用于拓扑结构的芯片组件包括一调阻抗电阻,所述调阻抗电阻被电连接于所述ddr_ecc芯片。

18.根据本实用新型一实施例,所述cpu被实施为ft2000。

19.根据本实用新型的另一个方面,本实用新型提供一种ddr4内存条,其中所述ddr4内存条包括:

20.一内存条主体;和

21.如上任一所述ddr4拓扑结构,其中所述ddr4拓扑结构被设置于所述内存条主体。

22.通过对随后的描述的理解,本实用新型进一步的目的和优势将得以充分体现。

23.本实用新型的这些和其它目的、特点和优势,通过下述的详细说明,得以充分体现。

附图说明

24.图1示出了现有技术中一t型结构的走线图。

25.图2示出了现有技术中的fly-by的走线图。

26.图3示出了本实用新型所述ddr4拓扑结构的一个示意图。

27.图4示出了本实用新型四通道的所述ddr4拓扑结构的一个示意图。

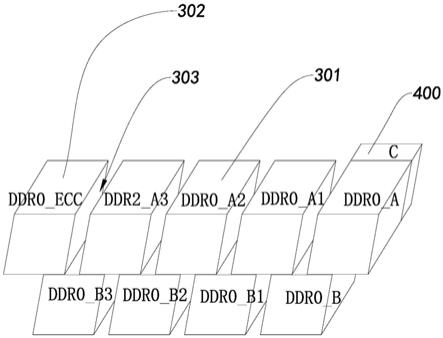

28.图5示出了本实用新型所述ddr4拓扑结构的所述用于拓扑结构的芯片组件中芯片的布局结构示意图。

29.图6示出了本实用新型所述ddr4内存条的一个视图。

具体实施方式

30.以下描述中的优选实施例只作为举例,本领域技术人员可以想到其他显而易见的变型。在以下描述中界定的本实用新型的基本原理可以应用于其他实施方案、变形方案、改进方案、等同方案以及没有背离本实用新型的精神和范围的其他技术方案。

31.本领域技术人员应理解的是,在本实用新型的揭露中,术语“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系是基于附图所示的方位或位置关系,其仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此上述术语不能理解为对本实用新型的限制。

32.结合说明书附图1至图6,依本实用新型一较佳实施例的一种ddr4内存条将在以下被详细阐述,其中所述ddr4内存条包括一ddr4拓扑结构100,其中所述ddr4拓扑结构100包括一cpu 200和至少一用于拓扑结构的芯片组件 300。

33.参考图3,具体地,每组所述用于拓扑结构的芯片组件300包括8个ddr 芯片301和

一ddr_ecc芯片302。8个所述ddr芯片301和所述ddr_ecc 芯片302通过水平错开叠置的方式摆放,如图5所示。8个所述ddr芯片301 以及所述ddr_ecc芯片302走线等长地连接于所述cpu 200。这样能够使8个所述ddr芯片301以及所述ddr_ecc芯片302对称地设置,从而提高信号的质量。8个所述ddr芯片301以及所述ddr_ecc芯片302芯片串联且被电连接于所述cpu 200。

34.此外,增加的所述ddr_ecc芯片302有助于使所述ddr4拓扑结构100进行自纠错。

35.优选地,所述ddr4拓扑结构100包括四个用于拓扑结构的芯片组件300,以形成四通道的所述ddr4拓扑结构100。如图4所示,所述ddr4拓扑结构 100包括的四个所述用于拓扑结构的芯片组件300分别为ddr0组件(其包括 ddr0_a、ddr0_b、ddr0_a1、ddr0_b1、ddr0_a2、ddr0_b2、ddr0_a3、 ddr0_b3和ddr0_ecc)、ddr1组件(其包括ddr1_a、ddr1_b、ddr1_a1、 ddr1_b1、ddr1_a2、ddr1_b2、ddr1_a3、ddr1_b3和ddr1_ecc)、ddr2 组件(其包括ddr2_a、ddr2_b、ddr2_a1、ddr2_b1、ddr2_a2、ddr2_b2、 ddr2_a3、ddr2_b3和ddr2_ecc)以及ddr3组件(其包括ddr3_a、 ddr3_b、ddr3_a1、ddr3_b1、ddr3_a2、ddr3_b2、ddr3_a3、ddr3_b3 合ddr3_ecc)。

36.四组所述用于拓扑结构的芯片组件300中每组用于拓扑结构的芯片组件300 包括8个ddr芯片301和一ddr_ecc芯片302。且8个所述ddr芯片301和所述ddr_ecc芯片302通过水平错开叠置的方式摆放。8个所述ddr芯片301 以及所述ddr_ecc芯片302走线等长地连接于所述cpu 200,如图5所示,其示出了其中ddr0组件中各芯片的摆放示意图。

37.值得一提的是,四组所述用于拓扑结构的芯片组件300中的相邻两个芯片之间形成一散热空间303,以便于每个所述芯片在后续运转过程中能够较好地进行散热。

38.优选地,所述ddr4拓扑结构100还包括至少一去耦电容400。至少一个所述去耦电容400被电连接于一个所述用于拓扑结构的芯片组件300的一个所述 ddr芯片。值得一体的是,所述去耦电容400可以被连接于所述用于拓扑结构的芯片组件300中任一一个所述ddr芯片。

39.更优选地,所述ddr4拓扑结构100包括每个用于拓扑结构的芯片组件300 都包括一个所述去耦电容400。

40.每组所述用于拓扑结构的芯片组件300包括一调阻抗电阻304。所述调阻抗电阻304被电连接于所述ddr_ecc芯片302。所述调阻抗电阻304能够将对应的所述用于拓扑结构的芯片组件300的电阻稳定在40欧,进而能够使得所述 ddr4拓扑结构100地址信号传输的稳定性。

41.所述ddr4内存条还包括一内存条主体500。所述ddr4拓扑结构100被设置于所述内存条主体500,以能够存储和输出数据。

42.优选地,所述cpu 200被实施为ft2000。

43.本领域的技术人员应理解,上述描述所示的本实用新型的实施例只作为举例而并不限制本实用新型。本实用新型的目的已经完整并有效地实现。本实用新型的功能及结构原理已在实施例中展示和说明,在没有背离所述原理下,本实用新型的实施方式可以有任何变形或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1