用于控制量子位的低温CMOS接口的制作方法

用于控制量子位的低温cmos接口

背景技术:

1.在诸如数字处理器等电子设备中使用的基于半导体的集成电路包括基于互补金属氧化物半导体(cmos)技术的数字电路。使用基于cmos技术的处理器和相关组件的附加方法是使用基于超导逻辑的设备。基于超导逻辑的设备也能够被用于处理量子信息,诸如量子位。

技术实现要素:

2.在一个方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制电路,其中第一封装设备被耦合至第二封装设备,并且其中控制电路包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。

3.在另一方面中,本公开涉及一种用于控制量子位门的系统中的方法,该系统包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作,并且控制电路被配置为在低温下操作,并且其中控制电路包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号,并且其中多个电荷锁定电路中的每个电荷锁定电路包括用于接收输入电压信号的第一端子和用于选择性地接收第一电压量或第二电压量的第二端子,并且其中第一电压量大于第二电压量。该方法可以包括在电容模式下操作多个电荷锁定电路的第一子集,使得输出到至少一个量子位门的电压信号包括具有第一受控幅度的脉冲信号,其中第一受控幅度取决于输入电压信号的量以及第一电压量和第二电压量中的每个电压量。该方法还可以包括在直接模式下操作多个电荷锁定电路的第二子集,使得输出到至少一个量子位门的电压信号包括具有第二受控幅度的信号,其中第二受控幅度取决于输入电压信号以及第一电压量或第二电压量中的仅一个电压量。

4.在又一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括被配置为在低温下操作的控制电路,其中控制电路包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号,并且其中多个电荷锁定电路中的每个电荷锁定电路包括用于接收输入电压信号的输入端子和用于选择性地向至少一个量子位门提供电压信号的输出端子,并且其中控制电路还包括控制逻辑,该控制逻辑被配置为提供与多个电荷锁定电路中的每个电荷锁定电路相关联的至少一个控制信号。

5.在又一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括控制电路,该控制电路包括有限状态机,该有限状态机被配置为提供至少一个控制信号,以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路并且选择性地支持将至少一个电压信号提供给多个电荷锁定电路中的一个所选电荷锁定电路。

6.在另一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括控制电路,该控制电路包括控制逻辑,该控制逻辑被配置为提供至少一个控制信号以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路。

7.在又一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括数模转换器,用于生成至少一个电压信号。控制系统还可以包括控制电路,该控制电路包括有限状态机,该有限状态机被配置为提供至少一个控制信号,以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路并且选择性地支持将至少一个电压信号提供给多个电荷锁定电路中的一个所选电荷锁定电路。

8.该发明内容被提供来以简化的形式介绍对于下面在详细描述中进一步描述的概念的选择。该发明内容不旨在标识所要求保护的主题的关键特征或者必要特征,也不旨在被用于限制所要求保护的主题的范围。

附图说明

9.本公开通过示例图示并且不受附图限制,其中相同的附图标记指示类似的元件。附图中的元件为了简单和清晰起见图示,并且不一定按比例绘制。

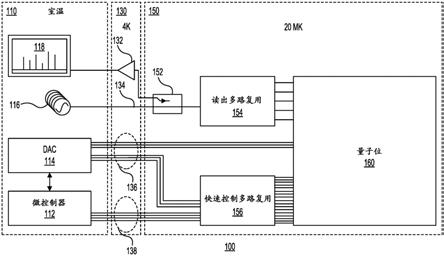

10.图1示出了根据一个示例的用于控制量子位的系统100;

11.图2示出了根据一个示例的包括低温cmos控制芯片、量子位芯片和谐振器芯片的公共衬底;

12.图3示出了根据一个示例的与快速控制多路复用相关联的控制系统的框图;

13.图4示出了根据一个示例的包括控制系统的低温cmos控制芯片的平面图;

14.图5示出了根据一个示例的电荷锁定快速门控(clfg)单元;

15.图6示出了与图5的clfg单元的操作相关联的示例波形600;

16.图7a和图7b示出了根据一个示例的与低温cmos控制芯片700相关联的各种块;

17.图8示出了根据一个示例的电荷锁定和快速门控的框图;

18.图9示出了快速门控电路的示例;

19.图10示出了根据一个示例的用于控制clfg单元的操作的有限状态机;

20.图11a和图11b示出了示例系统,该系统可以被用于生成使能信号作为示例低温cmos控制芯片的一部分;

21.图12示出了根据一个示例的clfg单元阵列;

22.图13示出了根据一个示例的被配置为以电容模式操作的示例clfg单元;

23.图14示出了根据一个示例的被配置为以双模式操作的示例clfg单元,包括电容模式和直接模式;

24.图15示出了与图13和图14所示的clfg单元的信号相关联的示例波形;

25.图16示出了与电容模式中的clfg单元的仿真相关联的示例波形;

26.图17示出了在电荷锁定测试期间示例量子位设备的有源区域的第一视图和第二视图;

27.图18示出了根据一个示例的与量子点触点(qpc)相关联的电压和电流的变化的视图;

28.图19示出了在测试具有量子点的快速门控操作期间对应于低温cmos控制芯片的示例波形;

29.图20示出了在测试低温cmos控制芯片期间与通过量子点的读出信号相对应的示例读出波形;

30.图21示出了根据一个示例的fdsoi数字设备;

31.图22示出了根据一个示例的fdsoi模拟设备;以及

32.图23示出了对应于与本公开中描述的系统相关联的方法的流程图。

具体实施方式

33.本公开中描述的示例涉及一种用于控制量子位门的低温cmos接口。控制量子设备需要生成大量静态和动态的电压信号,最好是在与量子设备紧密集成的低温下。如在本公开中使用的。术语“(多个)低温”是指等于或小于300开尔文的任何温度。考虑到低温环境强烈限制了任何有源电子设备的功耗,这是一项重大挑战。另外,大量的电压信号也需要被耦合至量子计算设备中的量子位门。这是因为可能数以千计的引线需要被连接至电压源,以驱动量子计算设备中的量子位门。而且,照惯例,量子位已利用室温脉冲发生器控制,该室温脉冲发生器必须生成在低温恒温器中衰减的大信号。克服这种衰减所需的功率以及驱动电缆阻抗所需的功率是缩放量子计算机的障碍。

34.本公开中描述的示例涉及用于量子计算设备的低温控制电路和架构。控制架构包括集成电路控制芯片,包含与量子位平面紧密集成的低温控制电路。作为示例,控制芯片能够被引线键合或倒装芯片安装至量子位平面。另外,控制芯片在电容器(包括互连电容)上存储电荷以生成偏压。单个数模转换器可以被用于设置每个电容器上的电荷,由于在这些

温度下极低的泄漏路径,电容器在低温下会保持很长时间。电荷的刷新能够在与量子位操作相称的时间尺度上循环进行。通过部署“电荷混洗”电路—在电容器之间移动电荷以生成电压脉冲,与衰减生成的热量相关联的挑战被解决。经由低温cmos控制芯片和量子位平面之间的紧密集成,电容被尽可能地减少。这种紧密集成(例如经由芯片堆叠封装方法)能够显著减少电容,从而影响耗散功率。

35.在一个示例中,低温cmos控制芯片可以使用完全耗尽的绝缘体上半导体(fdsoi)过程来实现。在一个示例中,基于fdsoi过程的设备可以包括未掺杂的栅极沟道、超薄体、源极、漏极和栅极下方的超薄隐埋氧化物(box)以及与相邻设备的完全介电隔离。用于电荷存储的电容器是使用片上设备实现的。每个晶体管器件的背栅或体偏置能够被用于动态配置阈值电压,以解决与冷却相关联的影响。控制芯片包括被分区为赋予公共背栅偏置的域的电路块。具有单独偏置的示例域包括用于n型设备的电路块、用于p型设备的电路块、用于模拟设备的电路块和用于数字设备的电路块。在一些示例中,不同的背栅偏置针对具有不同纵横比的晶体管提供。

36.量子位平面可以包括可以在大约20毫开尔文(~20mk)下操作的拓扑计算门。量子计算设备可以处理量子信息,例如量子位。量子位可以使用各种物理系统来实现,包括光子、电子、约瑟夫森结、量子点或异质结构。(多种)量子态可以被编码为自旋方向、自旋的另一方面、电荷、能量或作为量子位一部分的激发能级或者超导物质的拓扑相。示例量子位可以基于低频dc信号(例如偏置电流)或高频射频信号(例如10ghz信号)或基于两者的组合来操作。在某些示例中,微波信号可以被用于控制超导设备,包括例如量子比特(量子位)的状态。量子比特(量子位)门的某些实现可能需要高频微波信号。

37.图1示出了根据一个示例的用于控制量子位的系统100。在该示例中,系统100可以包括多个能级,每个能级可以被配置为在不同温度下操作。因此,系统100可以包括能级110、130和150。能级110可以包括被配置为在室温(例如环境温度)下或者在4开尔文和室温之间操作的组件。能级130可以包括被配置为在300开尔文或低于300开尔文以及高达4开尔文下操作的组件。能级150可以包括被配置为在20毫开尔文(mk)或大约20毫开尔文(mk)下操作的组件。能级110可以包括微控制器112(或微处理器)、数模转换器(dac)114、信号发生器116和测量设备118。微控制器112可以生成被配置为控制量子位和系统100的其他方面的控制信号。dac 114可以从微控制器112(或从其他组件)接收数字控制信号,并且将这些信号转换为模拟形式。模拟信号然后可以根据需要被传输给其他能级。根据需要,信号发生器116可以包括微波信号发生器和其他时钟信号发生器。测量设备118可以包括仪器,诸如频谱分析器。

38.继续参照图1,能级130可以包括被配置为以减少热负荷并且允许在室温下的组件与20毫开尔文(mk)下的组件之间的有效连接性的方式将能级110与能级150互连的组件。因此,在该示例中,能级130可以包括组件132、互连134、互连136和互连138。在一个示例中,组件132可以被实现为(多个)高电子迁移率晶体管((多个)hemt)低噪声放大器。互连134、136和138可以被实现为包括诸如铌和铜等导体的电缆。导体可以使用适当的介电材料(诸如聚酰亚胺)在互连内绝缘。

39.仍然参照图1,能级150可以包括耦合器152、读出多路复用154、快速控制多路复用156和量子位160。耦合器152可以将来自信号发生器(例如信号发生器116)的信号耦合至读

出多路复用154。耦合器152还可以将任何反射信号引导到组件132。读出多路复用154和快速控制多路复用156可以在单个控制芯片(有时称为低温控制cmos芯片)上实现。在一个示例中,读出多路复用154可以使用超导材料来实现,诸如在惰性衬底(诸如蓝宝石)上的铌。读出多路复用154芯片可以包含合适大小的多个电感、电容和电阻元件以形成(多个)谐振器组。在低温下,谐振器电路表现出超导性,并且产生具有高质量因子的谐振器。这可以提供有效的低损耗频率多路复用机制。在一个示例中,低温cmos控制芯片(例如使用诸如cmos等半导体技术制造的asic)可以被安装在与量子位(例如量子位160)相同的衬底上,并且可以被配置为在与量子位(例如20mk)相同的低温下操作。

40.图2示出了根据一个示例的包括低温cmos控制芯片210、量子位芯片250和谐振器芯片280的公共衬底200。低温cmos控制芯片210可以经由引线键合(例如引线键合212和214)被耦合至接触焊盘(例如接触焊盘222和224)。低温cmos控制芯片210还可以经由引线键合(例如引线键合216和218)被耦合至接触焊盘(例如接触焊盘226和228)。低温cmos控制芯片210还可以经由引线键合(例如引线键合230和232)被耦合至其他触点(例如触点234和236)。量子位芯片250可以经由引线键合(例如引线键合252和254)被耦合至接触焊盘(例如接触焊盘256和258)。量子位芯片250可以经由引线键合(例如引线键合260和262)被耦合至谐振器芯片280。谐振器芯片280可以经由引线键合(例如引线键合282和284)被耦合至触点(例如触点290和292)。虽然未在图2中示出,但是为了减轻量子设备的不必要加热,芯片封装布置还可以包括通过将每个芯片粘合至单独的镀金铜柱来进行热管理,这些铜柱与稀释制冷机的混合室能级平行热接触。虽然该示例示出了控制芯片和量子位之间经由引线键合的紧密集成,但其他技术也可以被使用。作为示例,控制芯片可以被倒装芯片键合至具有量子位的衬底。备选地,层叠封装、系统级封装或其他多芯片装配件也可以被使用。

41.在该示例中,低温cmos控制芯片可以以28nm-fdsoi技术实现,这是适合低温操作的固有低功率、低泄漏cmos平台。fdsoi中的晶体管可以提供配置背栅偏置的效用,以抵消阈值电压随温度的变化。该示例平台提供高(1.8v)和低(1v)电压单元,并且还允许对n型和p型晶体管或整个电路块进行单独的背栅控制,这是混合信号电路设计中的一个有用方面,诸如示例控制系统。

42.图3示出了根据一个示例的与快速控制多路复用156相关联的控制系统300的框图。控制系统300可以被用于控制作为控制芯片的一部分并入的电荷锁定和快速门控(clfg)单元360的行为。控制系统300可以包括串行外围接口(spi)接口310、波形存储器320、压控振荡器(vco)330、时钟选择多路复用器(c

sel

)340和有限状态机350。如所示,三个不同的电压电平可以被耦合至单元,包括v

hold

、v

high

和v

low

。c

sel 340被用于选择提供给有限状态机的时钟信号。关于有限状态机和相关寄存器的附加细节稍后被提供。

43.在一个示例中,控制系统300可以被实现为低温cmos控制芯片的一部分。图4示出了根据一个示例的低温cmos控制芯片400的平面图,包括控制系统420(类似于图1的控制系统300)。低温cmos控制芯片400可以包括数字和模拟块。在该示例中,低温cmos控制芯片400可以包括电荷锁定和快速门控(clfg)单元以及对应于控制系统420的组件。在该示例中,低温cmos控制芯片400可以包括逻辑410和clfg单元。在一个示例中,逻辑410可以包括一系列耦合的数字逻辑电路,其经由两个fsm提供芯片的通信、波形存储器和自主操作。逻辑410可以包括控制系统420,该控制系统420可以包括振荡器422、(多个)有限状态机fsm和spi接口

(例如fsm+spi接口)424和存储器426。振荡器422可以被实现为具有可配置长度的环形振荡器和分频器。关于fsm的附加细节稍后被提供。存储器426可以被配置为允许任意脉冲模式被存储的128位寄存器。沿着芯片的左侧和底部边缘平铺可能是重复的模拟电路块“clfg”,它生成控制量子位所需的静态和动态电压。clfg单元可以包括单元432、434、436和438。在此处描述的示例中,虽然clfg单元在单个管芯上实现,但是它们能够在封装在一起或以其他方式互连的多个管芯上形成。虽然图4示出了低温cmos控制芯片400的某个平面图,该芯片可以具有不同的平面图。另外,虽然图4示出了以某种方式布置的一定数量的组件,但低温cmos控制芯片400可以包括不同布置的附加的或更少的组件。

44.图5示出了根据一个示例的clfg单元500。clfg单元500可以被配置为锁定电荷并且提供电压输出。每个clfg单元500可以对应于n数量个单元中的任何一个。clfg单元500可以包括两个部分:用于将静态电压耦合至输出端子(标记为gate《n》)的部分510和用于将动态电压(基于电压v

high

或电压v

low

中的一个电压)耦合至输出端子的部分550。clfg单元500的部分510可以包括开关512,其可以响应于信号g

lock,n

而操作。该信号可以在适当的有限状态机或另一类型的控制逻辑或指令的控制下提供。当开关512闭合时,电压v

hold

可以被耦合至标记为c

pulse,n

的电容器的一个极板,其表示片上电容。clfg单元500的部分550还可以包括开关552和开关554。clfg单元500还可以包括反相器556。clfg单元500可以被配置为使得这些开关(开关552和开关554)中的仅一个开关在某个时间闭合。在该示例中,被标记为

gfg,n

的信号可以控制开关552,并且该信号的反相版本(例如由反相器556反相)可以控制开关554。这样,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至标记为c

pulse,n

的电容器的第二极板,其表示片上电容。

45.继续参照图5,c

p

可能是由于低温cmos控制芯片和(多个)量子位芯片中的布线以及用于将两者互连的引线(或其他互连)而产生的寄生电容的总和。单元可以首先通过片上有限状态机(fsm)选择以进行配置,该片上有限状态机将外部电压源连接至clfg单元500的输入端子(在图5中标记为in),从而将其电位升高到v

hold

。在该示例中,室温数模转换器(dac)的单个通道可以被用作源,并且fsm按顺序将每个clfg单元切换为与该偏压接触,从而为电容器通电,然后将锁定在高阻抗输出处生成静态电压所需的电荷。该电路包含片上电容c

pulse

和寄生电容c

p

,其包括来自量子位芯片上的键合焊盘、键合引线和栅极互连的贡献。在充电之后,开关512被fsm打开(例如通过撤销g

lock,n

信号),使电容器上的电荷和量子位门浮动。即使在clfg单元500被撤销时,该锁定电荷也会保持,从而建立能够被用于配置量子位设备的偏移偏置的静态电压。尽管图5示出了以某种方式布置的一定数量的组件,但是clfg单元500可以包括不同布置的附加的或更少的组件。

46.图6示出了与clfg单元500的操作相关联的示例波形600。针对动态控制,需要电压脉冲来快速改变量子位的栅极电位和能量状态。从量子位平面远程生成这种脉冲需要大量能量,因为发生器必须驱动电缆阻抗,即使功率没有在开放线路的末端耗散。备选地,通过在具有小电容的电路中重新分布局部电荷,相当大的电压脉冲能够用很少的能量生成。在该示例中,这个概念被用于实现clfg单元500的动态操作。在第二fsm的控制下,单元被选择用于脉冲,并且存储在寄存器存储器中的预加载脉冲模式被应用于开关g

fg

。

47.开关552和554以在两个电压源v

high

和v

low

之间拨动电容器c

pulse

的下极板的方式来控制。这些源能够在芯片外部,或者源自本地预充电的电容器。随着c

pulse

的下极板的电位切

换到v

low

或v

high

,电荷被诱导到顶极板上,从而改变相对于接地参考的输出电压v

out

。

48.在该示例中,脉冲的幅度由δv

pulse

=(c

pulse

/(c

p

+c

pulse

))(v

high-v

low

)给出,并且耗散功率p

pulse

由总电容、脉冲频率f和两个电平的电压给出,p

pulse

=((c

p

*c

pulse

)/(c

p

+c

pulse

))(v

high-v

low

)2f。因为c

p

和c

pulse

是(pf)芯片级电容,所以它们需要非常少的功率来充电。

49.图7a和图7b示出了根据一个示例的与低温cmos控制芯片700相关联的各种块。如早前解释的,低温cmos控制芯片700可以包括模拟和数字组件。在该示例中,低温cmos控制芯片可以包括模数转换器(adc)缓冲器702、ad c704、adc sram 706和adc控件708。低温cmos控制芯片700还可以包括时钟驱动器710、波形发生器720以及参考和偏置发生器722。这些组件可以经由各种总线耦合。每个总线可以包括至少一个信号线。如图7a和图7b所示,低温cmos控制芯片700可以接收各种外部信号,包括时钟信号、各种电压和控制信号。如所示,一些时钟是经由与控制芯片相关联的引脚从外部生成和接收的。

50.继续参照图7a,低温cmos控制芯片700还可以包括主控件和寄存器730以及各种杂项块740。主控件和寄存器730可以包括串行外围接口(spi),其可以允许与外部处理器进行通信。杂项块740可以包括采样保持(s&h)块742、比较器744和射频(rf)多路复用器(mux)746。rf mux 746可以允许在两个射频信号(rfin1和rfin2)之间进行选择。在该示例中,存在用于主控件和寄存器730的高级外围块时钟(apbclk)输入以及用于电荷锁定和快速门控块750的单独apbclk输入引脚。如图7b所示,针对电荷锁定和快速门控750,还能够切换到本地振荡器(例如vco 754)。本地振荡器也能够通过配置寄存器下分频。spi时钟(sclk)来自spi主机。在该示例中,来自spi主机的apbclk和sclk之间有一个时钟比要求。在一个示例中,apbclk必须》=4*sclk。为了确保正确计时,时钟域交叉(cdc)逻辑被布置在sclk和apbclk之间,并且另一cdc逻辑被布置在apbclk和分频振荡器时钟之间。

51.图7b示出了电荷锁定和快速门控750的一些方面的图。电荷锁定和快速门控750可以包括主控件和寄存器752、压控振荡器(vco)754和clfg单元阵列760。控件和寄存器752可以包括spi接口。控件和寄存器752可以包括寄存器读/写块,其又可以被耦合至寄存器堆。vco 754可以被配置为提供与电荷锁定和快速门控750的一些方面一起使用的另一时钟信号。clfg单元阵列760可以包括clfg单元762和764,每个clfg单元可以类似于图5的clfg单元500。

52.图8示出了根据一个示例的电荷锁定和快速门控(clfg)800的框图。clfg 800可以包括spi接口810,经由总线(例如apb)被耦合至寄存器读/写接口820,该寄存器读/写接口820又可以被耦合至寄存器830(例如寄存器可以被包括作为寄存器堆的一部分)。clfg 800还可以包括有限状态机840,其可以被配置为接收来自寄存器的输入并且向clfg单元阵列880提供输出信号,该clfg单元阵列880又可以向量子位提供电压。clfg 800还可以包括振荡器850、分频器(fdiv)860和多路复用器870。多路复用器870可以接收apb时钟作为一个输入,并且接收分频器输出作为其他输入。这样,在该示例中,有限状态机能够复印apbclk或来自本地振荡器的时钟信号。时钟控制模块可以被用于将本地振荡器时钟从1到255的整数值下分频,并且多路复用器870可以被用于允许在apbclk和分频振荡器时钟之间切换。分频时钟没有占空比要求。时钟控制模块的时钟输出被称为xclk,并且它被用于为有限状态机计时。

53.下面的表1列出了低温cmos控制芯片的一些信号及其描述。

[0054][0055]

表1

[0056]

表2列出了与低温cmos控制芯片相关联的一些寄存器。由于大多数寄存器的描述是不言自明的,因此仅一些寄存器及其功能性被描述以解释低温cmos控制芯片的操作。

[0057]

[0058]

[0059]

[0060]

[0061]

[0062][0063]

表2

[0064]

虽然表2示出了某些寄存器及其布置,但附加的或更少的寄存器可以被使用。另外,表格中呈现的信息可以经由寄存器以外的其他模态被传递给低温cmos控制芯片。作为示例,特殊指令可以被用于对寄存器中所包括的信息进行编码。表2中描述的寄存器所启用的架构假设有32个电荷锁定快速门控(clfg)单元。在该示例中,每个clfg单元都能够被独立地dc充电,并且能够根据存储在fgsr寄存器中的波形进行快速脉冲。在该实现中,128位能够被存储在四个32位寄存器(例如寄存器fgsr0-3)中,并且任何电荷锁定快速门控单元都能够根据这些寄存器中存储的位模式进行快速脉冲。位模式能够在fsm的控制下连续重复或播放一次。这种实现适合两级脉冲,然而它能够被扩展到多级脉冲。在该示例架构中,表2中描述的reg_ctl1寄存器包括由启动的有限状态机用于发起和完成单元充电的信息。作为示例,该寄存器的第8位控制fgsr选择的计数器何时被启用,并且在xclk时钟的每个时钟周期递增,直到它达到127,然后计数器翻转。作为另一示例,reg_ctl1寄存器的第4位和

第5位控制是否所有32个单元都出现完整的dc电荷序列,或者是否仅在32个单元的子集上出现选择性的dc电荷序列。

[0065]

图9示出了快速门控电路900的示例。如早前描述的,作为表2的一部分,四个32位寄存器可以控制快速门控电路900的输出。快速门控电路900可以包括计数器910、多路复用器920,其可以被耦合以接收计数器910的输出作为一个输入,并且接收对应于寄存器reg_ctl《3》的值作为另一输入。快速门控电路910还可以包括与门930、多路复用器940和门950,它们可以如图9所示彼此耦合。这些逻辑元件还可以接收图9所示的信号。计数器910选择128位值的比特位置以在cl_fg端子上输出。在该示例中,这是128比1的多路复用器。每个时钟周期(例如对应于图9所示的时钟xclk),计数器910被递增1。计数器910回绕到0并且继续计数。存储在reg_ctl[8]中的比特的值启用计数器910。因此,在该示例中,当reg_ctl[8]=0时,计数器保持在0并且不递增。如果电荷锁定状态机不空闲,那么快速门控输出cl_fg为0。在这种情况下,只要reg_ctl[8]=1,计数器就会继续递增。

[0066]

继续参照图9,在一个示例中,更新128位fgsr和启动新的快速门控序列的编程序列如下:(1)清除reg_ctl1[8]以将计数器保持为0,或者设置reg_ctl1[1]以停止xclk,(2)将新值写入四个32位fgsr寄存器,以及(3)设置reg_ctl1[8]以允许计数器递增,或者清除reg_ctl1[1]以恢复xclk。在一个示例中,fg输出也能够被覆盖。当reg_ctl1[2]=1时,cl_fg输出等于reg_ctl1[3]。尽管图9示出了具有以某种方式布置的一定数量的组件的快速门控电路900,但是快速门控电路900可以包括不同布置的附加的或更少的组件。另外,其他信号可以被用于提供附加的或更少的控制。

[0067]

图10示出了根据一个示例的有限状态机1000。在该示例中,有限状态机1000包括两个有限状态机:fsm a和fsm b。有限状态机中的每个有限状态机被配置用于clfg单元(例如clfg单元500)的dc充电。fsm a对应于有限状态机,其被配置为仅对根据cl_en寄存器中的比特启用的那些clfg单元同时充电。fsm b对应于有限状态机,其被配置为对clfg阵列中的所有clfg单元(例如具有32个单元的clfg阵列中的所有32个单元)按顺序充电。在该示例中,存储在寄存器中的比特值(例如与表2中描述的字段begin_chrg相对应的32位寄存器reg_ctl1的第4位和第5位)确定两个有限状态机中的哪个有限状态机是活动的。在该示例中,当begin_chrg字段从00过渡到01时,fsm a被启动;备选地,当begin_chrg字段从00过渡到10时,fsm b被启动。来自fsm a和fsm b的输出信号作为chrg信号提供,该chrg信号被耦合至多路复用器1002的输入中的一个输入。多路复用器1002的其他输入包括存储在reg_ctl《6》中的比特值(在表2中描述)。多路复用器1002的输出是全局dc电荷信号,并且被标记为cl_chrg。第7位的值(例如reg_ctl《7》)确定fsm a和fsm b的输出是否作为dc电荷信号提供,或者dc电荷信号是否被用户选择为表2中描述的reg_ctl寄存器的第6位的值。

[0068]

继续参照图10,在启动时,fsm a从idlea0状态开始,并且过渡到倒计时a状态。作为该过渡的一部分,fsm a维护chrg信号并且开始倒计时,以对已启用的那些clfg单元进行dc充电。在fsm a的整个操作期间,cl_en值保持与用户先前指定的相同。在该示例中,当具体clfg单元的本地使能信号为高电平(例如cl_en《i》=1)时,第i个clfg单元被启用。因此,通过对chrg信号进行门控,本地使能信号确保clfg单元仅在能够充电时才被充电。在充电完成后,fsm a进入空闲状态idlea1。下面的表3示出了fsm a的图10中引用的过渡/状态之间的示例对应关系以及比特和其他信号的示例值。

[0069][0070]

表3

[0071]

仍然参照图10,在启动时,fsm b进入start_chrg状态,并且假设有32个clfg单元,当cl_en《32》位被设置为1并且其他使能位中的每个位被设置为0时,开始为第32个clfg单元充电。作为该过程的一部分,fsm b进入倒计时b状态,并且对clfg单元的顺序充电所需的时钟周期(例如dcsr时钟周期)进行倒计时。除了在状态start_chrg和倒计时b中,在fsm b的整个操作期间,cl_en值保持与用户先前指定的相同。当cl_en《31》位被设置为1,并且其余使能位被设置为0时,第32个clfg单元的dc充电完成,并且第31个clfg单元的dc充电开始。在该示例中,这些步骤被重复,直到所有32个clfg电池都被充电为止。然后,fsm b过渡到空闲状态(例如idleb1状态)。下面的表4示出了fsm b的图10中引用的过渡/状态之间的示例对应关系以及比特和其他信号的示例值。

[0072][0073]

表4

[0074]

虽然图10示出了以某种方式操作的具体有限状态机,但是其他状态机也可以被使用。尽管表3和4涉及两个有限状态机的具体比特和信号以及相应值,但其他比特和信号及其相应值也可以被使用。另外,与状态机相关联的功能性可以使用其他逻辑或指令来实现。

[0075]

图11a和图11b示出了示例系统1100,其可以被用于生成使能信号作为示例低温cmos控制芯片的一部分。早前描述的fsm可以被用于与系统1100接口连接,该系统1100可以被用于生成使能信号,该使能信号被用于选择充电的clfg单元。该示例还假设有1024个clfg单元(布置在包括32行和32列的网格中)需要控制。系统1100可以包括主机逻辑和时钟部分1110、行译码器1120和列译码器1130。主机逻辑和时钟部分1110可以包括被配置为以类似于存储器控制器的方式存储和解释指令或命令的电路和逻辑。行译码器1120可以被配置为从主机逻辑和时钟部分1110接收行地址,并且维护标记为r0到r

31

的一个或多个信号。列译码器1130可以被配置为从主机逻辑和时钟部分1110接收列地址,并且维护标记为c0到c

31

和d0到d

31

的一个或多个信号。

[0076]

现在参照图11b,系统1100还可以包括总线系统,以将由行译码器1120和列译码器1130生成的信号耦合至电路1140。电路1140可以被配置为在其输出端子处生成标记为out

i,fg

的信号。该信号可以被耦合至量子位门1160。电路1140是类似于早前描述的clfg单元的“直接模式”的示例实现。因此,在该示例中,当相应行(rj)信号和相应列(ci)信号分别为高电平并且驱动线(d)信号为高或低电平时,电路1160可以被连接至电压总线v

lfg

或v

hfg

。电路1140也可以被实现为clfg单元阵列(例如如图5所示和早前描述的)。尽管图11将系统

1100示出为具有以某种方式布置的某些组件,但能够有不同布置的更多或更少的组件。

[0077]

图12示出了根据一个示例的clfg单元阵列1200。作为示例,clfg单元阵列1200可以对应于图7的clfg单元阵列760,并且可以被包括作为低温cmos控制芯片的一部分。在该示例中,clfg单元阵列1200可以包括32个clfg单元(例如clfg单元1210、1220、1230、1240和1250)。这些clfg单元中的每个clfg单元可以被配置为生成outcl信号中的一个outcl信号,该outcl信号可以被用于向量子位提供控制或其他类型的电压。每个clfg单元可以接收标记为cl_fg、cl_chrg、vicl、vhfg和vlfg的信号。这些信号将相对于图13和图14更详细地描述。另外,这些信号中的一些信号在早前也已经作为与低温cmos控制芯片相关联的描述的一部分描述。每个clfg单元还可以接收使能信号(例如cl_en《0》、cl_en《1》、cl_en《2》、cl_en《30》或cl_en《31》,如图12所示)。使能信号可以允许选择性或顺序的dc充电,如早前相对于图10中的有限状态机描述解释的。图12所示的clfg单元中的每个clfg单元还可以包括静电放电(esd)电路系统,包括esd电路1212、1222、1232、1242和1252。clfg单元可以仅以电容模式或以双模式操作,包括电容模式和直接模式。作为示例,clfg单元阵列1200可以由32个clfg单元组成—16个clfg单元被配置为在电容模式下操作,并且16个clfg单元被配置为在直接模式下操作。在一个示例中,每种类型的clfg单元的一半还可以包含具有减少的esd保护的自定义模拟焊盘,以进一步最小化通过标准焊盘结构的泄漏。尽管图12将clfg单元阵列1200示出为具有以某种方式布置的某些组件,但能够有不同布置的更多或更少的组件。

[0078]

图13示出了根据一个示例的被配置为以电容模式操作的clfg单元1300的示例。除非另有指示,否则图13中引用的信号具有与早前相对于图5至图7b以及表1和2描述的相同含义。clfg单元1300以与图5的clfg单元500类似的方式配置。clfg单元1300被配置为锁定电荷,并且在与clfg单元相关联的输出端子(out)处提供电压输出。每个clfg单元1300可以对应于n数量个单元中的任何一个。动态电压(基于经由vhfg端子(在图5中称为v

high

)接收的电压或经由vlfg端子(在图5中称为v

low

)接收的电压中的一个电压)可以被耦合至输出端子。clfg单元1300可以包括可以响应于信号cl_en《n》信号而操作的开关1312。该信号可以在适当的有限状态机或另一类型的控制逻辑的控制下提供,如相对于图10描述的。当开关1312闭合时,经由信号线vicl上的输入端子(in)接收到的电压(在图5中称为v

hold

)可以被耦合至标记为c

pulse,n

的电容器的一个极板,它表示片上电容。clfg单元1300还可以包括开关1314和开关1316。clfg单元1300还可以包括反相器1318。clfg单元1300可以被配置为使得这些开关中的仅一个开关在某个时间闭合。在该示例中,被标记为cl_en《n》的信号可以控制开关1314,并且该信号的反相版本(例如由反相器1318反相)可以控制开关1316。这样,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至标记为c

pulse,n

的电容器的第二极板,其表示片上电容。clfg单元1300还可以包括耦合至输出端子(out)的esd 1320。clfg单元1300仅在电容模式下操作,因为供应给量子位门的输出电压是经由图13所示的电容布置提供的。尽管图13示出了以某种方式布置的一定数量的组件,但是clfg单元1300可以包括不同布置的附加的或更少的组件。作为示例,clfg单元1300可以不包括esd 1320。

[0079]

图14示出了根据一个示例的被配置为以双模式(包括电容模式和直接模式)操作的clfg单元1400的示例。除非另有指示,否则图14中引用的信号具有与早前相对于图5至图7b以及表1和2描述的相同含义。clfg单元1400被配置为锁定电荷,并且在与clfg单元相关

联的输出端子(out)处提供电压输出。每个clfg单元1400可以对应于n数量个单元中的任何一个。在电容模式下(通过经由开关1414维护的标记为cl_mode的信号的维护来启用),动态电压(基于经由vhfg端子(在图5中称为v

high

)接收的电压或经由vlfg端子(在图5中称为v

low

)接收的电压中的一个电压)可以被耦合至输出端子。clfg单元1400可以包括可以响应于cl_en《n》信号而操作的开关1416。该信号可以在适当的有限状态机或另一类型的控制逻辑的控制下提供,如相对于图10描述的。当开关1416闭合时,经由信号线vicl上的输入端子(in)接收到的电压(在图5中称为v

hold

)可以被耦合至标记为c

pulse,n

的电容器的一个极板,它表示片上电容。clfg单元1400还可以包括开关1416和开关1418。clfg单元1400还可以包括反相器1420。clfg单元1400可以被配置为使得这些开关(1416和1418)中的仅一个开关在某个时间闭合。在该示例中,被标记为cl_en《n》的信号可以控制开关1416,并且该信号的反相版本(例如由反相器1420反相)可以控制开关1418。这样,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至标记为c

pulse,n

的电容器的第二极板,其表示片上电容。当cl_mode信号被维护时,clfg单元1400以电容模式运行,因为供应给量子位门的输出电压是经由图14所示的电容布置提供的。

[0080]

继续参照图14,当cl_mode信号被撤销时,clfg单元1400可以在直接模式下操作。因此,当cl_mode信号被撤销时,开关1434闭合并且取决于cl_en《n》信号的状态,开关1436或开关1438被闭合。因此,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至相同端子,v

in

电压经由输入端子(in)被耦合至该端子。clfg单元1400还可以包括耦合至输出端子(out)的esd 1450。尽管图14示出了以某种方式布置的一定数量的组件,但是clfg单元1400可以包括不同布置的附加的或更少的组件。作为示例,clfg单元1400可以不包括esd 1450。

[0081]

在clfg单元1300和clfg单元1400的情况下,一旦电容器被充电,低温环境中的低泄漏确保它们需要不太频繁地刷新。clfg单元中的每个clfg单元可以从单个dac接收电压。使用与栅格化显示器类似的技术,单个dac电压可以被用于为所有clfg单元(例如早前描述的示例中的32个clfg单元)充电。因此,在该示例中,dac电压通过闭合dac电压线和电容器之间的路径中的开关来提供给电容器;在电容器被充电后,开关打开,并且dac电压被用于以循环方式为下一电容器充电。通过使用共享dac,控制芯片(包括clfg单元阵列)和室温电子设备之间的输入/输出线的数量被显著减少。如早前描述的,低温cmos控制芯片和量子位平面之间的互连是使用引线键合、倒装芯片键合或其他低阻抗互连技术形成的。

[0082]

图15示出了与clfg单元1300和clfg单元1400的信号相关联的示例波形1500。在该示例中,clfg单元1300和clfg单元1400中的每个clfg单元被示出为关于标记为xclk的时钟操作。cl_chrg信号基于与低温cmos控制芯片相关联的控制寄存器(例如reg_dcsr)中指定的时钟周期(或另一指标)在一段时间内维护。cl_fg控制信号被用于电荷混洗。针对clfg单元1300和clfg单元1400,每当该控制信号为高电平时,outcl端子处的电压在vicl+v

high

电压与v

low

电压之间的差异之间进行脉冲。每当cl_fg控制信号为低电平时,clfg单元1300和clfg单元1400都在dc模式下操作,使得输出电压(由dc模式中标记为outcl的波形表示)被保持在电容器最初被充电到的电压(例如通过cl_chrg信号),并且它在没有刷新的情况下可能会随时间耗散。电容模式中标记为outcl的波形示出了clfg单元1300的输出信号。该相同波形还示出了clfg单元1400在电容模式下操作时的输出。直接模式中标记为outcl的波

形示出了clfg单元1400在直接模式下操作时的输出信号。这些模式中的每种模式都在早前相对于图13和14解释。

[0083]

继续参照图15,在电容模式下使用clfg 1400的快速门控操作周期包括存储电容器的dc充电,随后是一系列脉冲。在一个示例中,dc充电时段由reg_dcsr值确定。脉冲的时段和数量由被设置为128位的cl_fgsr寄存器(早前解释的)的内容确定。在该示例中,该寄存器的内容一次被读取一位(例如由波形发生器),并且作为标记为:cl_fg的控制信号应用。当使用直接驱动模式时,快速门控由一系列脉冲组成,其中输出被直接连接至vlfg或vhfg。在直接驱动模式下,充电周期仍然存在,并且其行为与cl_fgsr上的“0”值相同。这些模式中的每种模式都在早前相对于图13和14解释。

[0084]

图16示出了与电容模式中的clfg单元1400的仿真相关联的示例波形1600。标记为outcl的波形表示在电容模式下操作时clfg单元1400的仿真输出信号。标记为cl_en的波形对应于使能信号,其被用于启用clfg单元进行充电。cl_chrg信号被用于为与clfg单元相关联的电容器(或多个电容器)充电。如早前解释的,cl_chrg信号基于与低温cmos控制芯片相关联的控制寄存器(例如reg_dcsr)中指定的时钟周期(或另一指标)在一段时间内维护。针对clfg单元1400,每当cl_fg控制信号为高电平时,outcl端子处的电压在vicl+v

high

电压与v

low

电压之间的差异之间进行脉冲。vicl电压对应于clfg单元的输入端子处的电压,该电压可以从dac接收(如早前解释的)。v

high

电压是经由vhfg端子接收的,并且波形在图16中也被标记为vhfg。v

low

电压是经由vlfg端子接收的,并且波形在图16中也被标记为vlfg。

[0085]

继续参照图16,outcl波形的部分1602示出了clfg单元中的dc电压(例如1.8伏特)的锁定。outcl波形的部分1604示出了电压的快速门控,以生成能够被用作量子位的控制信号的脉冲。部分1606示出了在脉冲生成之后还原的锁定dc电压。部分1608示出了当锁定dc电压未被刷新或还原时outcl端子处的电压。部分1610示出了锁定与部分1602中锁定的电压电平不同的dc电压电平(例如0.6伏特)。部分1612示出了电压的快速门控以生成具有不同幅度的脉冲,其也能够被用于控制量子位或其他这种设备。虽然图16将outcl波形示出为具有矩形脉冲,但脉冲可以具有不同的形状。虽然图16将outcl波形示出为具有两个不同的幅度,outcl波形的幅度可能有其他变化。类似地,outcl波形的脉冲频率也可以经由早前描述的低温cmos控制芯片来控制。另外,outcl波形可以被用于调制高频信号,例如微波音调,以生成用于量子位门或另一类型的量子位设备的控制信号。

[0086]

图17示出了在电荷锁定测试期间示例量子位设备1700的有源区域的第一视图1710和第二视图1750。量子位设备1700可以是基于砷化镓(gaas)的量子点设备。在该示例中,如视图1710和视图1750所示,多个信号可以被用于控制量子点。早前描述的低温cmos控制芯片可以被用于使用与早前描述的clfg单元相关联的电容模式或直接模式来生成任何控制信号。用于控制量子位的信号可以包括左壁(lw)信号、左柱塞(lp)信号、中心壁(cw)信号、右柱塞(rp)信号和右壁(rw信号)。与感测量子位门中的量子点1730相关的附加信号可以包括感测点顶栅(sd

t

)、感测点柱塞(sd

p

)和感测点底栅(sdb)。在该示例中,如视图1710所示,控制信号lw、lp、cw、rp和rw的电位可以基于编程的有限状态机使用五个clfg单元来锁定。虽然图17示出了具有某些控制信号的量子位设备1700,具有其他控制信号的其他类型的量子位设备也可以承受由早前描述的低温cmos控制芯片生成的电压。

[0087]

图18示出了根据一个示例的与量子点触点(qpc)相关联的电压和电流的变化的视

图1800。曲线图1810示出了qpc电流随时间的变化。曲线图1820示出了作为左壁电压变化的函数的qpc电流变化。曲线图1830示出了低温cmos控制芯片保持电压随时间的变化。

[0088]

图19示出了在测试具有量子点的快速门控操作期间对应于低温cmos控制芯片的示例波形1900。示例波形1910对应于当快速门控以140khz执行时的读出信号。示例波形1920对应于当快速门控以1.26mhz执行时的读出信号。示例波形1930对应于当快速门控以2.45mhz执行时的读出信号。频率能够使用分频器改变。波形不共享公共时间尺度。虽然图19示出了与波形相关联的电压脉冲的特定占空比和振幅,占空比和振幅能够由低温cmos控制芯片改变。这有利地消除了从室温设备控制量子位门的需要。

[0089]

从室温控制量子位门将需要衰减在室温下生成的电压脉冲,导致需要从室温电压脉冲耗散大量热量。另外,不需要来自室温的电压信号来处理一米长(或更长)电缆(例如就电容性负载而言大于200pf的50欧姆传输线)的负载,低温cmos控制芯片只需要处置倒装芯片键的电容以及控制芯片和量子位门之间非常短的互连。该电容可能低至0.1pf。这允许低温cmos控制芯片控制数千个量子位的状态,而无需大量散热。另外,来自快速门控的功耗很小,因此它允许控制芯片有效地管理潜在的数千个量子位。在控制量子位的功率要求方面,在一个示例中,假设读出时钟频率被设置为1mhz,量子位互连具有1pf的电容,那么针对0.1伏特脉冲的每1000个量子位门的功耗为10μw。假设每个量子位有10个门,1mw的功率能够被用于控制1mhz时钟频率下的10,000个量子位或10mhz时钟频率下的1000个量子位。

[0090]

图20示出了在测试低温cmos控制芯片期间与通过量子点的读出信号相对应的示例读出波形2000。当clfg单元电压v

high

和v

low

被用于生成用于控制量子点的脉冲并且感测点柱塞(sd

p

)栅极上的电压被扫描时,波形2000被生成。波形2010示出了v

high

电压的变化,并且波形2020示出了v

low

电压的变化。波形2030示出了施加到clfg单元的脉冲。

[0091]

如早前描述的,在一个示例中,低温cmos控制芯片可以使用完全耗尽的绝缘体上半导体(fdsoi)过程来实现。在一个示例中,基于fdsoi过程的设备可以包括未掺杂的栅极沟道、超薄体、源极、漏极和栅极下方的超薄隐埋氧化物(box)以及与相邻设备的完全介电隔离。如早前描述的,基于fdsoi过程的设备可以包括数字和模拟设备(例如晶体管或其他设备)。图21示出了根据一个示例的fdsoi数字设备2100。fdsoi数字设备2100可以包括衬底2102。在该示例中,衬底2102可以是绝缘体上硅(soi)衬底。通过用n型掺杂剂掺杂衬底,深n阱2104可以在衬底2102中形成。附加阱可以在衬底2102和深n阱2104中形成。作为示例,p阱2106和n阱2108可以被形成。接下来,使用多个光刻步骤,晶体管器件2120和晶体管器件2130可以被形成。在该示例中,晶体管器件2120是p型晶体管,具有形成在块2126上方的栅极沟道2122。晶体管器件2120还可以包括p+型源极/漏极区域以及与源极/漏极的触点s和d。在该示例中,晶体管器件2130是n型晶体管,具有形成在块2136上方的栅极沟道2132。晶体管器件2130还可以包括n+型源极/漏极区域以及与源极/漏极的触点s和d。用于电荷存储的电容器是使用这种晶体管器件实现的。各种类型的设备和区域可以使用浅沟槽隔离(sti)区域来隔离,该浅沟槽隔离(sti)区域是使用电介质形成的。在fdsoi数字设备2100中形成的示例sti区域包括sti 2150、sti 2152、sti 2154、sti 2156、sti 2158和sti 2160。

[0092]

继续参照图21,每个晶体管器件的背栅或体偏置能够被用于动态配置阈值电压,以解决与冷却相关联的影响。因此,在该示例中,fdsoi数字设备2100包括用于n型设备的经由n

bg

端子的背栅偏置和用于p型设备的经由p

bg

端子的背栅偏置。在该示例中,虽然fdsoi数

字设备2100包括改变n型和p型设备的背栅偏置的能力,但n型设备的背栅电压不允许低于p型设备的背栅电压。

[0093]

仍然参照图21,每个晶体管器件的背栅或体偏置能够被用于动态配置阈值电压,以解决与低温环境中的芯片的冷却相关联的影响。晶体管器件和相关控制电路被设计为使得使用背栅偏置控制,尽管晶体管器件的操作温度发生巨大变化,但晶体管器件的阈值电压能够被调谐。低温cmos控制芯片可以包括被分区为赋予公共背栅偏置的域的电路块。具有单独偏置的示例域包括用于n型设备的电路块、用于p型设备的电路块、用于模拟设备的电路块和用于数字设备的电路块。在一些示例中,不同的背栅偏置针对具有不同纵横比的晶体管提供。虽然图21示出了包括一定数量和类型的阱的fdsoi数字设备2100,fdsoi数字设备2100可以包括附加的或更少的其他类型的阱。另外,晶体管器件可以是平面的或非平面的(例如finfet设备)。

[0094]

图22示出了根据一个示例的fdsoi模拟设备2200。与fdsoi数字设备2100不同,fdsoi模拟设备2200包括独立的背栅偏置控制,其中p型设备的背栅电压能够被升高到电压v

dd

以上,而与n型晶体管的背栅电压无关。fdsoi模拟设备2200可以包括衬底2202。在该示例中,衬底2202可以是绝缘体上硅(soi)衬底。通过用n型掺杂剂掺杂衬底,深n阱2204可以在衬底2202中形成。p阱2206可以被形成在深n阱2204中,并且n阱2208可以被形成在衬底2202中。接下来,使用多个光刻步骤,晶体管器件2220和晶体管器件2230可以被形成。在该示例中,晶体管器件2220是p型晶体管,具有形成在块2226上方的栅极沟道2222。晶体管器件2220还可以包括p+型源极/漏极区域以及与源极/漏极的触点s和d。在该示例中,晶体管器件2230是n型晶体管,具有形成在块2236上方的栅极沟道2232。晶体管器件2230还可以包括n+型源极/漏极区域以及与源极/漏极的触点s和d。各种类型的设备和区域可以使用浅沟槽隔离(sti)区域来隔离,该浅沟槽隔离(sti)区域是使用电介质形成的。在fdsoi模拟设备2200中形成的示例sti区域包括sti 2250、sti 2252、sti 2254、sti 2256、sti 2258、sti 2260、sti 2262和sti 2164。

[0095]

继续参照图22,每个晶体管器件的背栅或体偏置能够被用于动态配置阈值电压,以解决与冷却相关联的影响。因此,在该示例中,fdsoi模拟设备2200包括用于n型设备的经由n

bg

端子的背栅偏置和用于p型设备的经由p

bg

端子的背栅偏置。在该示例中,与fdsoi数字设备2100不同,fdsoi模拟设备2200包括独立的背栅偏置控制,其中p型设备的背栅电压能够被升高到电压v

dd

以上,而与n型设备的背栅电压无关。

[0096]

仍然参照图22,每个晶体管器件的背栅或体偏置能够被用于动态配置阈值电压,以解决与低温环境中的芯片的冷却相关联的影响。晶体管器件和相关控制电路被设计为使得使用背栅偏置控制,尽管晶体管器件的操作温度发生巨大变化,但晶体管器件的阈值电压能够被调谐。在一些示例中,不同的背栅偏置针对具有不同纵横比的晶体管提供。虽然图22示出了包括一定数量和类型的阱的fdsoi模拟设备2200,fdsoi模拟设备2200可以包括附加的或更少的其他类型的阱。另外,晶体管器件可以是平面的或非平面的(例如finfet设备)。

[0097]

在一个示例低温cmos控制芯片中,fdsoi数字设备2100可以被用作电路块的一部分,该电路块只需要电压的低值和高值之间的差异并且不涉及中间值。因为fdsoi数字设备2100比fdsoi模拟设备2200占用的面积更小,所以将其用于大多数电路是有利的,只要它们

不太敏感即可。在一个示例中,仅fdsoi模拟设备2200被制造,使得针对n型和p型设备具有独立的背栅偏置控制以及基于这些设备的纵横比的独立背栅偏置控制。如早前描述的,低温cmos控制芯片可以被分区为域,使得每个域包括多个晶体管器件,但共享公共背栅偏置。在一个示例中,基于n型与p型设备的组合以及与每种类型的设备相关联的不同纵横比,可能有八个域。

[0098]

图23示出了对应于与本公开中描述的系统相关联的方法的流程图2300。在一个示例中,一种用于控制量子位门的系统可以包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。作为示例,量子设备可以对应于图1的量子位160。该系统还可以包括被配置为在低温下操作的控制电路,并且其中该控制电路包括多个电荷锁定电路。作为示例,控制电路可以对应于早前描述的低温cmos控制芯片中所包括的电路。多个电荷锁定电路中的每个电荷锁定电路可以经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号,其中多个电荷锁定电路中的每个电荷锁定电路包括用于接收输入电压信号的第一端子和用于选择性地接收第一电压量或第二电压量的第二端子,其中第一电压量大于第二电压量。作为示例,电荷锁定电路可以被包括为clfg单元360的一部分。每个电荷锁定电路可以对应于早前描述的clfg单元500、clfg单元1300或clfg单元1400中的任何一个。

[0099]

步骤2310可以包括在电容模式下操作多个电荷锁定电路的第一子集,使得输出到至少一个量子位门的电压信号包括具有第一受控幅度的脉冲信号,其中第一受控幅度取决于输入电压信号的量以及第一电压量和第二电压量中的每个电压量。在一个示例中,该步骤可以与clfg单元1300的操作相关。如早前描述的,clfg单元1300可以包括可以响应于cl_en《n》信号而操作的开关1312。该信号可以在适当的有限状态机或另一类型的逻辑的控制下提供,如相对于图10描述的。当开关1312闭合时,经由信号线vicl上的输入端子(in)接收到的电压(在图5中称为v

hold

)可以被耦合至标记为c

pulse,n

的电容器的一个极板,它表示片上电容。clfg单元1300还可以包括开关1314和开关1316。clfg单元1300还可以包括反相器1318。clfg单元1300可以被配置为使得这些开关中的仅一个开关在某个时间闭合。在该示例中,被标记为cl_en《n》的信号可以控制开关1314,并且该信号的反相版本(例如由反相器1318反相)可以控制开关1316。这样,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至标记为c

pulse,n

的电容器的第二极板,其表示片上电容。

[0100]

步骤2320可以包括在直接模式下操作多个电荷锁定电路的第二子集,使得输出到至少一个量子位门的电压信号包括具有第二受控幅度的信号,其中第二受控幅度取决于输入电压信号以及第一电压量或第二电压量中的仅一个电压量。在一个示例中,该步骤可以与clfg单元1400的操作相关。如早前描述的,当cl_mode信号被撤销时,clfg单元1400可以在直接模式下操作。因此,当cl_mode信号被撤销时,开关1434闭合并且取决于cl_en《n》信号的状态,开关1436或开关1438被闭合。因此,在某个时间,电压v

high

或电压v

low

可以经由两个开关中的一个开关被耦合至相同端子,v

in

电压经由输入端子(in)被耦合至该端子。

[0101]

总之,在一个方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电

荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括控制电路,该控制电路包括有限状态机,该有限状态机被配置为提供至少一个控制信号,以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路并且选择性地支持将至少一个电压信号提供给多个电荷锁定电路中的一个所选电荷锁定电路。

[0102]

多个电荷锁定电路的子集可以包括电容器,并且其中控制逻辑还被配置为选择性地支持将至少一个电压信号提供给与多个电荷锁定电路的至少一个子集中的一个所选电荷锁定电路相关联的电容器。控制系统还可以包括波形发生器和寄存器,该寄存器用于存储与波形相对应的位模式以用于由波形发生器生成。

[0103]

多个电荷锁定电路中的每个电荷锁定电路可以包括用于接收输入电压信号的输入端子和用于选择性地向至少一个量子位门提供电压信号的输出端子。多个电荷锁定电路中的每个电荷锁定电路还可以包括电容器,该电容器具有用于接收输入电压信号的第一端子和用于选择性地接收第一电压量或第二电压量的第二端子。

[0104]

控制系统还可以包括用于指定时间量的控制寄存器,并且其中有限状态机被配置为在控制寄存器中指定的时间量内选择性地支持将至少一个电压信号提供给电容器,该电容器与多个电荷锁定电路中的一个所选电荷锁定电路相关联。多个电荷锁定电路中的每个电荷锁定电路还可以被配置为生成电压信号作为具有受控幅度的脉冲信号,其中受控幅度至少取决于第一电压量和第二电压量。

[0105]

在另一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,该第一封装设备包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,该第二封装设备包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括控制电路,该控制电路包括控制逻辑,该控制逻辑被配置为提供至少一个控制信号以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路。

[0106]

控制逻辑可以包括有限状态机,该有限状态机被配置为选择性地支持将至少一个电压信号提供给多个电荷锁定电路中的一个所选电荷锁定电路。多个电荷锁定电路的至少一个子集可以包括电容器,并且其中控制逻辑还被配置为选择性地支持将至少一个电压信号提供给与多个电荷锁定电路的至少一个子集中的一个所选电荷锁定电路相关联的电容器。控制系统还可以包括波形发生器和寄存器,该寄存器用于存储与波形相对应的位模式以用于由波形发生器生成。

[0107]

多个电荷锁定电路中的每个电荷锁定电路可以包括用于接收输入电压信号的输入端子和用于选择性地将电压信号提供给至少一个量子位门的输出端子。多个电荷锁定电路中的每个电荷锁定电路还可以包括电容器,该电容器具有用于接收输入电压信号的第一端子以及用于选择性地接收第一电压量或第二电压量的第二端子。控制系统还可以包括用于指定时间量的控制寄存器,并且其中有限状态机被配置为在控制寄存器中指定的时间量

内选择性地支持将至少一个电压信号提供给电容器,该电容器与多个电荷锁定电路中的一个所选电荷锁定电路相关联。多个电荷锁定电路中的每个电荷锁定电路还可以被配置为生成电压信号作为具有受控幅度的脉冲信号,其中受控幅度至少取决于第一电压量和第二电压量。

[0108]

在又一方面中,本公开涉及一种用于控制量子位门的系统。该系统可以包括第一封装设备,包括量子设备,该量子设备包括多个量子位门,其中量子设备被配置为在低温下操作。该系统还可以包括第二封装设备,包括被配置为在低温下操作的控制系统,其中第一封装设备被耦合至第二封装设备。控制系统可以包括多个电荷锁定电路,其中多个电荷锁定电路中的每个电荷锁定电路经由互连被耦合至多个量子位门中的至少一个量子位门,使得多个电荷锁定电路中的每个电荷锁定电路被配置为向至少一个量子位门提供电压信号。控制系统还可以包括数模转换器,用于生成至少一个电压信号。控制系统还可以包括控制电路,该控制电路包括有限状态机,该有限状态机被配置为提供至少一个控制信号,以选择性地启用多个电荷锁定电路中的至少一个电荷锁定电路并且选择性地支持将至少一个电压信号提供给多个电荷锁定电路中的一个所选电荷锁定电路。

[0109]

控制系统还可以包括波形发生器和寄存器,该寄存器用于存储与波形相对应的位模式以用于由波形发生器生成。多个电荷锁定电路中的每个电荷锁定电路可以包括用于接收输入电压信号的输入端子以及用于选择性地将电压信号提供给至少一个量子位门的输出端子,并且其中多个电荷锁定电路中的每个电荷锁定电路还包括电容器,该电容器具有用于接收输入电压信号的第一端子以及用于选择性地接收第一电压量或第二电压量的第二端子。

[0110]

控制系统还可以包括用于指定时间量的控制寄存器,并且其中有限状态机被配置为在控制寄存器中指定的时间量内选择性地支持将至少一个电压信号提供给电容器,该电容器与多个电荷锁定电路中的一个所选电荷锁定电路相关联。多个电荷锁定电路中的每个电荷锁定电路还可以被配置为生成电压信号作为具有受控幅度的脉冲信号,其中受控幅度至少取决于第一电压量和第二电压量。

[0111]

要理解的是,本文描绘的方法、模块和组件仅仅是示例性的。例如但不限于,超导设备的说明性类型可以包括现场可编程门阵列(fpga)、专用集成电路(asic)、专用标准产品(assp)、片上系统(soc)、复杂可编程逻辑设备(cpld)等。

[0112]

另外,在抽象但仍然明确的意义上,实现相同功能性的任何组件布置被有效地“关联”,使得期望的功能性被实现。因此,本文中组合以实现特定功能性的任何两个组件能够被视为彼此“关联”,使得期望的功能性被实现,而与架构或中间组件无关。同样地,如此关联的任何两个组件也能够被视为彼此“可操作地连接”或“耦合”,以实现期望的功能性。

[0113]

此外,本领域技术人员将认识到,上述操作的功能性之间的边界仅仅是说明性的。多个操作的功能向可以被组合为单个操作,和/或单个操作的功能性可以被分布在附加操作中。而且,替代实施例可以包括特定操作的多个实例,并且操作的顺序在各种其他实施例中可以更改。

[0114]

虽然本公开提供了具体示例,但是各种修改和改变能够在不脱离下面的权利要求中陈述的本公开的范围的情况下进行。因此,说明书和附图应被认为是说明性的而非限制性的,并且所有这种修改旨在被包括在本公开的范围内。本文关于具体示例描述的任何益

处、优点或问题的解决方案不旨在被解释为任何或所有权利要求的关键、必需或基本特征或元素。

[0115]

此外,本文使用的术语“一”或“一个”被定义为一个或多于一个。而且,在权利要求中使用诸如“至少一个”和“一个或多个”等介绍性短语不应被解释为意味着,由不定冠词“一”或“一个”介绍另一权利要求元素将包含这种介绍的权利要求元素的任何特定权利要求限制到仅包含一个这种元素的发明,即使同一权利要求包括介绍性短语“一个或多个”或“至少一个”以及不定冠词(诸如“一”或“一个”)时也是如此。这同样适用于定冠词的使用。

[0116]

除非另有规定,否则诸如“第一”和“第二”等术语被用于任意地区分这种术语描述的元素。因此,这些术语不一定旨在指示这种元素的时间或其他优先化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1