基于非易失性存储器的紧凑型混合信号乘法累加引擎的制作方法

基于非易失性存储器的紧凑型混合信号乘法累加引擎

背景技术:

1.本公开整体涉及机器学习加速器,并且更具体地涉及用于提高机器学习操作的效率的混合信号乘法累加引擎。

2.基于非易失性存储器(nvm)的交叉架构提供用于在机器学习算法(特别是神经网络)中执行乘法累加(mac)运算的另选机制。使用nvm位单元的混合信号方法依赖于欧姆定律,以通过利用新兴的nvm技术(例如,相变存储器(pcm)、电阻式随机存取存储器(rram)、关联电子随机存取存储器(ceram)等)的电阻性质来实施乘法运算。跨nvm位单元施加电压偏置生成与nvm元件的电导和跨单元的电压偏置的乘积成比例的电流。

3.接着可并行地添加来自多个此类位单元的电流以实施累加和。因此,欧姆定律和基尔霍夫电流定律的组合并行地实施多个mac运算。当在数字域中使用显式乘法器和加法器实施时,这些可能是能量密集的。

4.根据本公开,提供了改进的nvm交叉架构,这些改进的nvm交叉架构提供模拟计算运算的能量高效加速,同时减少已知方法中固有的伴随的面积和产出影响。

附图说明

5.本公开以举例的方式例示并且不限制在附图中,其中相同的附图标号指示类似的元件,并且在附图中:

6.图1a和图1b描绘神经网络的高级表示;

7.图2是卷积神经网络的单层内的卷积运算的图示;

8.图3是用于使用nvm交叉结构执行卷积运算的架构的描绘;

9.图4是根据本公开的实施方案的用于使用电导以数字方式对权重进行编码的示意性电路;并且

10.图5是根据本公开的实施方案的乘法累加引擎的架构。

具体实施方式

11.现在将关于附图详细描述本公开的具体实施方案。为了说明的简单和清晰,在被视为适当的情况下,可在附图中重复附图标号以指示对应的或类似的元件。另外,阐述了许多具体细节以便提供对本文所述的示例的透彻理解。然而,本领域普通技术人员将理解,本文所述的示例可在没有这些具体细节的情况下实践。在其它情况下,未详细描述熟知的方法、程序和部件以免模糊本文所述的示例。而且,本说明书不应被视为限制本文所述的示例的范围。

12.应当理解,本文所用的示例和对应图仅用于说明性目的。在不脱离本文表达的原理的情况下,可使用不同的配置和术语。例如,在不脱离这些原理的情况下,可以不同的连接添加、删除、修改或布置部件和模块。

13.在本公开的实施方案的以下详细描述中,阐述了许多具体细节以便提供对本公开的更加透彻的理解。然而,对于本领域的技术人员显而易见的是,可在没有这些具体细节的

情况下实践本公开。在其它情况下,未详细描述熟知的特征以避免不必要地使本说明书复杂化。

14.应当理解,本文所用的术语是出于描述根据本公开的各种实施方案的目的,并且不旨在是限制性的。如本文所用,术语“一个(a/an)”被定义为一个或多于一个。如本文所用,术语“多个”被定义为两个或多于两个。如本文所用,术语“另一个”被定义为至少第二个或更多个。如本文所用,术语“包括”和/或“具有”被定义为包括(即,开放式语言)。如本文所用,术语“耦接”被定义为连接,但未必直接地并且未必机械地连接。术语“提供”在本文中以其最广泛的含义定义,例如,整体或者同时或在一定时段内以多个部分开始成为/变为物理存在、变得可用和/或向某人或某物供应。

15.如本文所用,术语“约”、“大约”或“基本上”适用于所有数值,而不管这些数值是否是明确指示的。此类术语通常是指本领域技术人员将认为等效于所叙述值(即,具有相同功能或结果)的数字范围。这些术语可包括四舍五入至最接近的有效数的数字。在该文档中,对术语“纵向”的任何引用应当理解为意指在对应于个人计算装置从一个终端端部到相反终端端部的伸长方向的方向上。

16.图1a和图1b是神经网络的图。图1a示出神经网络100的示例,该神经网络通常包括多个输入神经元1021、1022、

…

、102n(其中“n”是任何合适的数目),隐藏层1041、1042、

…

104n(其中“n”是任何合适的数目)和输出神经元1061、1062、

…

106n(其中“n”是任何合适的数目)。

17.图1b描绘分别由具有对应的权重w1、w2、w

n-1

、

…

、wn的x1、x2、x3、x

n-1

、

…

、xn(其中“n”是任何合适的数目)表示的多个输入激活108(a)、108(b)、108(c)、108(d)、

…

、108(n),该多个输入激活分别对应于图1a所示的每个神经元1021、1022、

…

、102n。对应神经元的激活函数112输出输出激活y,该输出激活可以是(但不限于)阶跃函数h,该阶跃函数的输出y在输入和高于阈值时是恒定值,并且在输入和低于该相同阈值时是零(或不同的恒定值)。

18.图2示出卷积神经网络(cnn)200的单层内的卷积运算。在该示例中,存在多个滤波器“m”2021、2022和202n以及多个输入通道。单个滤波器在不同通道中跨“c”输入特征图2041、2042和204n进行卷积以产生对应于单个滤波器的“m”输出特征图2061、2062和206n。因此,存在各自对应于单独滤波器的多个输出特征图。在图2的图示中,假设滤波器的尺寸为2x2并且输入特征图的尺寸为6x6。因此,对于图2所示的具体图示,总运算次数为2x2xcx(5x5)xm。

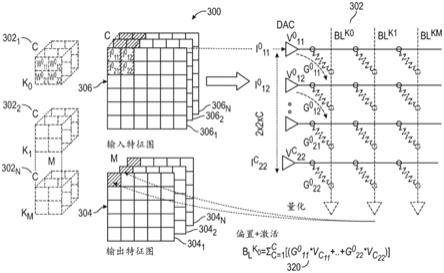

19.图3例示了架构300,该架构示出可如何使用nvm交叉结构302来实施这种运算。根据图2重复标识相同部件的附图标号。

20.在交叉结构302中,卷积滤波器的权重被编程为单独的位单元w

011

、w

012

、w

021

、w

022

(如3021所示)。由于低阻态(lrs)和高阻态(hrs)之间的较宽分离,在单独的位单元内对多个线性分离的电阻级进行编码是有用的。例如,就ceram而言,hrs/lrs的比率为至少2个数量级。因此,对4位(或16级)电阻进行编码是可能的。接着使用数模转换器(dac)302将来自输入特征图3061…n的数字字转换成模拟电压,接着跨nvm单元施加该模拟电压。因此,所得的电流与输入字和权重的点积成比例。接着在位线上并行地累加这些单独的电流。一旦在位线上产生累加的电流信号,就可使用模数转换器(adc)再次将该电流信号数字化,并且可将偏置添加、缩放和激活函数320应用于所得的数字字以获得输出激活。

21.在图3中,例示了利用m滤波器和c输入通道进行的cnn到nvm交叉结构的映射。在已知技术中,可假设权重ω是静止的,即,它们被编程到交叉结构中一次,并且通常在推断运算的过程中不会改变。典型的nvm元件(例如,相变存储器和电阻式ram)具有有限的写入“耐久度”—即,可能写入这些nvm元件有限的次数(例如,大约108次),在这些次数之后,交叉结构可能表现出功能故障。其它nvm元件(诸如磁性ram和ceram)展现出相对较高耐久度的前景(近10

12

),但连续运算仍然会导致有限的使用寿命。因此,此类使用寿命限制对依赖于以每个推断循环更新权重的加速器架构造成显著约束。例如,对于在100mhz下运算的物联网(iot)类加速器,具有108的耐久度的加速器具有1秒的使用寿命,并且具有10

12

的耐久度的加速器具有10,000秒或4天(最坏情况、峰值使用量)的使用寿命。因此,此类权重实际上无法从外部dram流式传输,并且必须是片上固定的。此外,为了执行更新运算,nvm位单元可能遭受高写入功率以及随之而来的昂贵的功率消耗。因此,写入阶段可能存在问题并且花费长时间来完成。

22.此类布置与sram行为不同(该sram行为具有显著更高的写入耐久度),并且不适于在推断期间对权重进行重新编程。因此,整个网络被展开到片上交叉结构中并且在推断期间是固定的。虽然这具有消除dram功率消耗的优点,但是它可能会不期望地限制可进行片上编程的网络的最大大小。此外,这还通常引发面积损失,因为映射较大网络涉及容量为兆位的交叉结构的实例化。由于产出损失,这消耗了较高的面积并且使得更易于出现芯片失效。此外,实例化多个交叉结构涉及多个adc/dac的实例化,所有这些adc/dac都需要被编程、修整和漂移补偿。

23.公开了用于在神经网络中执行乘法累加计算的方法和架构。该架构包括布置在平铺列中的非易失性存储器元件的多个网络。提供了另外控制电路,该另外的控制电路调节该多个网络中的单独网络的等效电导以将每个单独网络的该等效电导映射到神经网络内的单个权重。该神经网络内的第一部分选集的权重被映射到这些平铺列中的这些网络的这些等效电导中,以使得能够通过混合信号计算来计算乘法和累加运算。控制逻辑更新这些映射以选择第二部分选集的权重来计算另外的乘法和累加运算,并且然后重复这些映射和这些计算运算,直到针对该神经网络的期望的计算完成。在一些实施方案中,该神经网络具有可完全映射到非易失性存储器元件的该多个网络的大小。

24.根据另一个实施方案,该乘法累加架构包括多个晶体管和电阻器,该多个晶体管和电阻器可操作来选择该多个权重作为以电导表示的二进制权重。

25.根据又一个实施方案,非易失性存储器电阻可操作来特别地执行计算。

26.根据另一个实施方案,该乘法累加在模拟混合模式域中实施。

27.根据一个实施方案,外部随机存取存储器设置在片外,并且该多个权重从外部随机存取存储器流式传输。

28.根据另一个实施方案,该外部随机存取存储器是动态随机存取存储器和伪静态随机存取存储器中的一者。

29.根据另一个实施方案,提供了一种可操作来多路复用相应平铺列的输出的模数转换器。

30.根据又一个实施方案,神经元由多个平铺列构成。

31.根据再一个实施方案,提供了可操作来执行乘法累加运算的关联电子随机存取存

储器。

32.根据另一个实施方案,提供了一种用于网络中的乘法累加运算的方法。该方法包括在布置在平铺列中的非易失性存储器元件的多个网络中:以数字方式调节该多个网络中的单独网络的等效电导以将每个单独网络的该等效电导映射到神经网络内的单独权重,该神经网络内的第一部分选集的权重被映射到这些平铺列中的这些网络的这些等效电导中,以使得能够通过混合信号计算来计算乘法和累加运算;更新这些映射以选择第二部分选集的权重来计算另外的乘法和累加运算;以及重复该映射和这些计算运算,直到针对该神经网络的所有计算完成。

33.本公开提供了一种用于模拟计算的能量高效加速的方案。具体地说,结合了nvm中的计算运算和存储运算之间的基本分割。根据本公开的实施方案,nvm交叉结构用于计算运算。因此,代替实例化显式mac和累加器,根据本公开的实施方案提供模拟域乘法和累加。由于传统上固定的权重不可使用数字逻辑进行切换,因此这些权重现在可独立于显式重新编程在高频率下交换(和晶体管能够切换的频率一样快)。

34.在数字域中执行权重编码,从而增加对变化问题的鲁棒性。现在参考图4,描绘了示意性电路400的表示,该表示例示了使用电导以数字方式编码的权重。电路400表示为示意图并且包括多个电阻器r1442、r2446、r3450、r4454以及由t1440、t2444、t3448和t4452表示的晶体管。电路400仅仅是说明性的,并且可配置有根据本公开的实施方案的电阻器和晶体管的任何合适的组合。使用电导的等效网络形成每个等效权重。在图4所示的具体示例中,示出了nvm元件的并行网络,其中每个元件具有电导“g”。因此,4位数字总线可在1g、2g、3g和4g电导之间切换,从而实现2位权重。类似地,8个电阻可实现3位权重,并且16个电阻可实现4位权重。

35.另选地,电导本身可被编程为二进制加权的。在权重编码的一个方案中,用于ceram的所产生的导通lrs电阻可独立于重新编程而工作。根据本公开的实施方案,计算阶段和存储阶段被分成不同类别。nvm电阻可用于计算目的。权重存储器从外部存储位置(诸如dram或psram)流式传输。从而通过利用具有自己的选择器装置并且独立于显式乘法器的ceram/nvm元件来以紧凑方式实现mac运算。每个电路400对应于神经网络内的单独网络,如图5中进一步例示。如转让给本技术的受让人的共同未决的美国专利申请序列号15/884,612中所述,该专利申请的公开内容通过引用并入本文,nvm/ceram元件是(完全或部分)由关联电子材料(cem)形成的特定类型的随机存取存储器。ceram可表现出由电子关联而不是固态结构相位变化引起的(例如像由电阻式ram装置中的细丝形成和导电引起的)突然导电或绝缘状态转变。与熔融/固化或细丝形成相比,ceram中的突然导体/绝缘体转变可响应于量子力学现象。

36.ceram在绝缘状态和导电状态之间的量子力学转变可根据莫特转变来理解。在莫特转变中,如果产生莫特转变条件,则材料可从绝缘状态切换到导电状态。当实现临界载流子浓度以使得满足莫特标准时,将发生莫特转变,并且状态将从高电阻/阻抗(或电容)改变为低电阻/阻抗(或电容)。

37.ceram元件的“状态”或“存储器状态”可取决于ceram元件的阻抗状态或导电状态。在该上下文中,“状态”或“存储器状态”意指指示值、符号、参数或条件(仅提供几个示例)的存储器装置的可检测状态。在特定具体实施中,可至少部分地基于在读取操作中在存储器

装置的终端上检测到的信号来检测存储器装置的存储器状态。在另一个具体实施中,存储器装置可处于特定存储器状态以通过在“写入操作”中跨存储器装置的终端施加一个或多个信号来表示或存储特定值、符号或参数。

38.ceram元件可包括夹置在导电终端之间的材料。通过在终端之间施加具体电压和电流,材料可在前述导电状态和绝缘状态之间转变。夹置在导电终端之间的ceram元件的材料可通过跨具有复位电压和处于复位电流密度的复位电流的终端施加第一编程信号而处于绝缘状态,或者通过跨具有设定电压和处于设定电流密度的设定电流的终端施加第二编程信号而处于导电状态。

39.现在参考图5,例示了根据本公开的实施方案的mac引擎的架构500,其中mac计算在模拟混合模式域中特别地执行,并且其它运算在数字域中实施。架构500包括多个网络5011、5012、5013、501n,该多个网络是网络503的一部分,该网络驻留在图1a和图1b的整个神经网络100内。图中示出的5011、5012…

、501n的数目是说明性的。在该实施方案中,不采用交叉架构。相反,如说明性实施方案中所描绘的每个神经元被分成多个平铺列5021和5022。同样,虽然两个平铺列5021和5022为了说明的目的示出,但平铺列可以是任何合适的数目。通过输入dacin0(5201)

…

dacin_n(520n)的数字逻辑耦接到每列数字权重控制逻辑块5041和504n。这些将相应权重配置在形成每个网络的多个混合模式mac引擎中,该多个混合模式mac引擎由块5061、5062、5063和5064表征,每个块对应于图4的电路400。使用已知的模拟/混合信号(mx)方法执行mac运算,并且结果在adc上数字化,并且在量化和偏置块508处生成输出激活。单个adc可进一步用于在各种神经元之间多路复用。架构500的每个列操作为累加器,并且每个选择的ceram等效位单元可操作为mac引擎。根据本公开的实施方案,该架构以数字方式调节多个网络中的单独网络5011、5012、5013、501n的等效电导以将每个单独网络的等效电导映射到神经网络100内的单个权重w,如图1a和图1b所示,其中神经网络300内的第一部分选集的权重被映射到平铺列5021和5022中的网络5011、5012、5013、501n的等效电导中,以使得能够通过混合信号计算来计算乘法和累加运算。更新映射以选择第二部分选集的权重来计算另外的乘法和累加运算,并且重复映射和计算运算,直到针对神经网络的所有期望的计算完成。

40.在上述实施方案的变型中,紧凑型可编程mac引擎还可与较小的完全固定等效物结合提供,其中完全固定等效物被配置为过滤掉dram流量并且操作为常规模拟mac引擎。这适用于大多数网络,因为其不再受片上nvm容量限制。完全可编程的模拟mac引擎也可在较大的神经网络的情况下接通或启用。

41.总之,本公开有利地提供以下功能:

42.代替将所有权重映射到交叉结构,权重从外部dram流式传输,并且交叉结构用于以非常高的效率执行低精度mac计算。因此,本公开的实施方案将“在存储中计算”方法分成仅计算运算。已经发现,通过将电阻器仅用于计算,实现了能量效率的提高。

43.nvm元件仅可操作为电阻器,并且非易失性不是必需的。因此,根据本公开的实施方案可使用多晶硅电阻器、塑料电子器件(其中没有pmos)和上拉电阻器。

44.本文所公开的方案使用选择器晶体管来接入具体权重值。这使得能够独立于对nvm元件本身进行显式重新编程从而显著缩小面积要求来进行数字权重重新编程。通过实现模拟电路的重新使用,它涉及仅实例化少量的adc/dac,从而降低设计的工程复杂性。

45.所公开的重新使用方案使得设计能够缩放到基本上任何网络大小,从而减少对可通过模拟混合信号方法寻址的网络的最大大小的限制。

46.最后,该方法可扩展到基于磁阻随机存取存储器(mram)的交叉结构。

47.说明书中对“一个实施方案”或“一实施方案”的引用意指结合该实施方案描述的特定特征、结构或特性包括在系统的至少一个实施方案中。在说明书中各处出现短语“在一个实施方案中”并不一定全部是指相同的实施方案。

48.在本文中参考根据本公开的实施方案的方法、设备(系统)和计算机程序产品的流程图图解和/或框图来描述本公开的实施方案。应当理解,流程图图解和/或框图的每个框以及流程图图解和/或框图中的框的组合可通过计算机可读程序指令来实施。

49.详细描述的一些部分(如过程)可根据对计算机存储器内的数据位的运算的算法和符号表示来呈现。可通常设想算法是导致期望的结果的步骤。这些步骤是需要物理量的物理转化或操纵的步骤。尽管并非必要,但这些量通常采取能够存储、转移、组合、比较和以其它方式操纵的电信号或磁信号的形式。主要出于常用的原因,有时已经证明将这些信号称为位、值、元素、符号、字符、术语、数字等是方便的。

50.然而,应当考虑到,所有这些和类似的术语将与适当的物理量相关联,并且仅仅是应用于这些量的方便的标签。除非明显通过以下讨论另外特别说明,否则应当理解,在整个说明书中,利用诸如“处理”或“运算”或“计算”或“确定”或“导出”或“显示”等的术语进行的讨论是指计算机系统或类似的电子计算装置的动作和过程,该计算机系统或类似的电子计算装置将表示为计算机系统的寄存器和存储器内的物理(电子)量的数据操纵并转化成类似地表示为计算机系统存储器或寄存器或其它此类信息存储、传输或显示装置内的物理量的其它数据。

51.本文所述的运算可由设备执行。该设备可专门为所需目的构建,或该设备可包括通过存储在计算机中的计算机程序选择性地激活或重新配置的通用计算机。这种计算机程序可存储在计算机可读存储介质中,诸如但不限于任何类型的磁盘、只读存储器(rom)、随机存取存储器(ram)、eprom、eeprom、磁性卡或光学卡,或适于存储电子指令的任何类型的介质。如本文所用,计算机可读存储介质不应被解释为本身是暂时性信号,诸如无线电波或其它自由传播的电磁波、通过波导或其它传输介质传播的电磁波(例如,通过光纤电缆传递的光脉冲)、或通过导线传输的电信号。

52.因此,本公开的实施方案和特征在以下编号的项目中列出:

53.1.一种在神经网络中执行乘法累加运算的方法,包括:在布置在平铺列中的非易失性存储器元件的多个网络中:以数字方式调节该多个网络中的单独网络的等效电导以将每个单独网络的该等效电导映射到该神经网络内的单个权重,该神经网络内的第一部分选集的权重被映射到这些平铺列中的这些网络的这些等效电导中,以使得能够通过混合信号计算来计算乘法和累加运算;更新这些映射以选择第二部分选集的权重来计算另外的乘法和累加运算;以及重复该映射和这些计算运算,直到针对该神经网络的计算完成。

54.2.根据项目1所述的方法,其中权重的该选择是以电导表示的二进制权重。

55.3.根据项目1所述的方法,还包括:使用该非易失性存储器元件在该神经网络中执行该乘法和累加计算,并且将这些权重存储在这些非易失性存储器元件的外部。

56.4.根据项目3所述的方法,其中非易失性存储器电阻能够操作来特别地执行这些

乘法和累加计算。

57.5.根据项目1所述的方法,还包括:在模拟混合模式域中实施该乘法和累加计算。

58.6.根据项目1所述的方法,还包括:从外部存储器流式传输这些权重。

59.7.根据项目6所述的方法,其中该外部存储器是动态随机存取存储器和伪静态随机存取存储器中的一者。

60.8.根据项目1所述的方法,还包括:通过模数转换器多路复用这些相应平铺列的输出。

61.9.根据项目1所述的方法,其中神经元由多个平铺列构成。

62.10.根据项目1所述的方法,其中该乘法累加运算使用关联电子随机存取存储器(ceram)来执行。

63.11.一种用于在神经网络中执行乘法累加计算的架构,包括:非易失性存储器元件的多个网络,这些非易失性存储器元件的多个网络布置在平铺列中;逻辑,该逻辑以数字方式调节该多个网络中的单独网络的等效电导以将每个单独网络的该等效电导映射到该神经网络内的单个权重,该神经网络内的第一部分选集的权重被映射到这些平铺列中的这些网络的这些等效电导中,以使得能够通过混合信号计算来计算乘法和累加运算;以及逻辑,该逻辑更新这些映射以选择第二部分选集的权重来计算另外的乘法和累加运算,并且重复这些映射和这些计算运算,直到针对该神经网络的计算完成。

64.12.根据项目11所述的架构,还包括:多个晶体管和电阻器,该多个晶体管和电阻器能够操作来选择多个权重作为以电导表示的二进制权重。

65.13.根据项目11所述的架构,其中这些权重被存储在这些非易失性存储器元件的外部。

66.14.根据项目13所述的架构,其中非易失性存储器电阻能够操作来特别地执行计算。

67.15.根据项目11所述的架构,其中该乘法累加在模拟混合模式域中实施。

68.16.根据项目11所述的架构,还包括:外部存储器,该外部存储器设置在片外,其中多个权重从该外部存储器进行访问。

69.17.根据项目16所述的架构,其中该外部存储器是动态随机存取存储器和伪静态随机存取存储器中的一者。

70.18.根据项目11所述的架构,还包括:模数转换器,该模数转换器能够操作来多路复用这些相应列的输出。

71.19.根据项目11所述的架构,其中神经元由多个平铺列构成。

72.20.根据项目11所述的架构,还包括:关联电子随机存取存储器(ceram),该ceram能够操作来执行该乘法累加运算。

73.21.根据项目11所述的架构,其中该神经网络具有完全映射到非易失性存储器元件的该多个网络的大小。

74.根据前述内容,公开了一种用于网络中的乘法累加运算的方法和架构。因此,已经详细地并且参考本公开的实施方案描述了本技术的公开内容,将显而易见的是,在不脱离如下所附权利要求书中限定的范围的情况下,修改和变型是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1