乘法累加器的制作方法

乘法累加器

1.相关申请

2.本技术要求下述在先申请的优先权:2019年9月17日提交的发明名称为“multiply-accumulate unit”的美国临时专利申请us62/901,270,其内容作为参考全部纳入本文。

技术领域

3.本发明涉及累加器电路,并且尤其涉及一种利用模拟电路改良的乘法器电路。

背景技术:

4.乘法累加器(multiply-accumulator,mac)电路,其用于对数字信号执行乘法运算,通常相当复杂且庞大。而且,实时(real-time)mac通常需要快速(“on the fly”)程序以根据实时输入数据有效地产生运算输出。另一方面,闪存在集成电路上能为非易失性数据储存装置的有效做法。然而,闪存必需在运行电路前程序化,且闪存于运行mac运算前因其缓慢程序化速度和重新编程的有限利用性而不能更新。因此,储存在闪存的数据于mac运算期间应为静态的。

5.图1为常规mac阵列的简化功能方块图。mac阵列100广泛应用于数字信号处理、通信、网络及神经网络。此种常规全数字化mac包括数字乘法器(digital multiplier)、数字加法器(digital adder)以及数字累加器(digital accumulator)。每个子单元包括结合多个晶体管的多个数字逻辑闸。从数据输入总线d_in_bus馈入数字输入数据以使mac阵列100接收。mac阵列数据输出连接数据输出总线d_out_bus。针对单一mac所涉及的运算,单个操作数(从数据输入总线d_in_bus)的每个数字和其他操作数(从数据输入总线d_in_bus)的每个数字相乘以形成部分乘积;接着相加这些结果。然后,那些相加后乘积依序发送至数字累加器并且由数据输出总线d_out_bus执行。这种常规mac阵列100通常需要相当大量的晶体管,从而于大量晶体管制造在集成电路上期间占用相当多芯片面积,而此种面密度(areal density)并非有效率的。在处理单一mac的操作时,各数字元逻辑信号需要全电压摆幅(full vdd-gnd swing),并且在mac阵列中每条单一导线仅运载单一位(bit)。因此,常规mac阵列无效率地消耗相当大量功率。由于此技术限制,集成电路开发者的目标为找寻实现具有简单且有效率的电路组件之乘法器的方法。

6.图2为用于模拟运算的电子突触(synapse)电路之简化功能方块图。mac阵列200包括以行和列构成矩阵的多个非易失性突触(non-volatile synapse,nv synapse)单元。多条字符线wl2、wl1和wl0电性连接至各行中的每个非易失性突触单元。多条参考线sl2、sl1和sl0电性连接至各行中的每个非易失性突触单元。两对互补式位线bl0/blb0和bl1/blb1各连接至各行中的每个非易失性突触单元。感测电路(sensing circuit)在多条位线中提供一对差动电流至各行中的每个非易失性突触单元。四个晶体管(两对cso/cs1)连接感测电路至多个突触单元,并且允许(enable)或禁用(disable)在各非易失性突触单元和感测电路之间位线差分的电流(i

bl

,i

blb

)。

7.尽管未示出,作为乘法器/累加器电路,各非易失性突触单元配置为接收作为第一操作数x的一个输入且使用作为第二操作数y的储存值(参数)。非易失性突触单元能被执行来使用前述闪存实现以储存第二操作数y。此储存后第二操作数y能表示为结合特定非易失性突触单元的过滤系数或权重参数。各非易失性突触单元从第一操作数x和第二操作数y产生部分乘积,接着所得的部分乘积在对应位线中加总。位于两条互补式位线的末端之感测电路将互补式位线bl0/blb0之模拟输入端之间的微小电压差放大至标准逻辑位准(normal logic level)。假定储存的第二操作数y为静态的,此种架构未能支持其操作数的数值需实时更新的实时mac运算。因此,mac运算仅能从阵列中具有那些预先编程参数值的特定非易失性突触单元取得。

8.如此就将可运用的运算能力限制在给定的非易失性突触单元阵列的尺寸内。举例来说,若mac阵列具有100万个非易失性突触单元,因各非易失性突触单元仅能于当下储存1个参数值,则可用参数总数限制为不超过100万个。因此,在神经网络的应用中,因为可运用的操作数总数由于非易失性突触单元的长编程时间而被限制,这种传统架构对于深层且庞大模型和训练目的并不是有效率的。

技术实现要素:

9.本发明提供了一种累加器电路,尤其是利用模拟电路实现之改良的乘法累加器电路。

10.根据本发明,一种模拟乘法累加器阵列,包括:多个模拟乘法器,设置为以行和列构成矩阵,其中各个所述模拟乘法器包括:一条或一条以上的模拟输入信号线,耦接在阵列的其中一行上的多个模拟乘法器;模拟位准感测电路;具有至少一条的一组位线,各位线电性连接其中一行上的各列的模拟乘法器;模拟累加器,配置为连接位线至模拟位准感测电路,以产生数字输出信号,其中连接到模拟输入信号线的存取晶体管和可变电阻形成模拟乘法器。

11.在一种实施方式中,可变电阻包括:一个或多个闪存,其中至少一个闪存配置为连接第一模拟输入线并且所述存取晶体管具有闸极端连接第二模拟输入线。

12.在另一种实施方式中,可变电阻包括:一个读取晶体管;以及一对耦接晶体管,配置为与所述读取晶体管具有共享浮动闸极,其中耦接晶体管耦接输入线,并且输入线从连接存取晶体管的模拟输入信号线分离。

13.在另一种实施方式中,模拟乘法器进一步包括:切换晶体管,以串联方式连接存取晶体管,所述切换晶体管具有连接到数字输入线的闸极端。

14.在另一种实施方式中,切换晶体管以串联方式连接可变电阻,使得存取晶体管启用或关闭位线中电流导向可变电阻。

15.在另一种实施方式中,可变电阻包括:一个或多个闪存,其中至少一个闪存配置为连接第一模拟输入线并且存取晶体管具有闸极端连接第二模拟输入线。

16.还有,作为另一种实施方式,可变电阻包括:一个读取晶体管;以及一对耦接晶体管,配置为与读取晶体管具有共享浮动闸极,其中耦接晶体管中的一个连接编程字符线,而耦接晶体管中的另一耦接晶体管连接写入字符线。

17.在另一种实施方式中,编程字符线连接耦接晶体管中的一个控制闸极,而写入字

符线连接耦接晶体管中的另一个。

18.在另一种实施方式中,模拟累加器包括:排列成行的mos晶体管阵列,各mos晶体管连接所述一组位线中的一条位线;以及一条控制线,连接mos晶体管的闸极以启动mos晶体管的切换,使得在mos晶体管启动期间,相连的多条位线中流动的电流被汇合在相连的多条位线之一。

19.此外,在另一种实施方式中,模拟累加器包括:排列成行的cmos晶体管阵列,各cmos晶体管连接到位线集合中的位线;以及成对控制线,连接形成cmos晶体管的nmos晶体管的闸极,并且第二源极节点连接形成cmos晶体管的pmos晶体管的闸极,使得在nmos晶体管、pmos晶体管或nmos晶体管和pmos晶体管启动期间,相连的多条位线流动的电流被汇合在相连的多条位线之一。

20.此外,作为另一种实施方式,模拟累加器包括:成行形成电流镜的成对的pmos晶体管阵列,各对pmos晶体管形成电流镜并且包括:成对的第一晶体管和第二晶体管,其具有共享节点以连接一对晶体管的闸极,其中第一晶体管具有汲极端连接共享节点,而第二晶体管具有汲极端根据连接共享节点的位线中流动电流输出放大电流。

21.根据本发明,一种模拟乘法累加器阵列,包括:模拟乘法器,排列成行和列的矩阵,每个乘法器包括:成对模拟输入信号线,耦接到阵列中一行的模拟乘法器;模拟电平检测电路;一组位线,每条位线电连接到行的每列中的模拟乘法器;模拟累加器被配置为将所述组位线连接到用于产生数字输出信号的模拟电平感测电路,其中一对差分晶体管、可变电阻器和开关晶体管形成模拟乘法器。

22.在另一种实施方式中,差动晶体管中的第一个差动晶体管,具有闸极耦接一对模拟输入信号线的第一信号线,第一差动晶体管与一组位线的第一位线相关联;一对差动晶体管的第二差动晶体管,具有闸极耦接一对模拟输入信号线的第二信号线,第二差动晶体管与一组位线的第二位线相关联。

23.在另一种实施方式中,切换晶体管包括一对mos晶体管以串联方式连接一对差动晶体管。

24.在另一种实施方式中,可变电阻包括:一个读取晶体管,其形成模拟乘法器;以及成对耦接晶体管,连接所述读取晶体管,所述耦接晶体管具有共享浮动闸极,其连接所述读取晶体管的闸极端,其中所述差动晶体管的共享源极端连接所述读取晶体管的汲极端。

25.在另一种实施方式中,模拟乘法累加器阵列进一步包括:符号选择单元,具有四个晶体管,配置成使第一和第二晶体管的闸极端连接多条互补式数字输入信号线的其中一条,并且第三和第四晶体管的闸极端连接以接收多条互补式数字输入信号线之其他条,其中成对模拟输入信号线被允许与符号选择单元中的成对第一晶体管和第二晶体管或符号选择单元中的成对第三晶体管和第四晶体管相关联。

26.在另一种实施方式中,模拟累加器包括:成行排列的mos晶体管阵列,各mos晶体管连接一组位线中一条位线;以及控制线,连接mos晶体管的闸极以启动mos晶体管的切换,使得在mos晶体管启动期间,相连的多条位线中流动的电流被汇合在相连的多条位线的其中一条上。

27.在另一种实施方式中,模拟累加器包括:成行排列的cmos晶体管阵列,各cmos晶体管连接一组位线中一条位线;以及成对控制线,连接形成cmos晶体管的nmos晶体管的闸极,

并且第二源极节点连接形成cmos晶体管的pmos晶体管的闸极,使得在nmos晶体管、pmos晶体管或nmos晶体管和pmos晶体管启动期间,相连的多条位线中流动的电流被汇合在相连的多条位线之其中一条上。

28.此外,作为另一种实施方式,模拟累加器包括成行排列的pmos晶体管阵列,各对pmos晶体管形成电流镜且包括:成对的第一晶体管和第二晶体管为,具有共享节点以连接成对晶体管的闸极,其中第一晶体管具有汲极端连接共享节点,而第二晶体管具有汲极端根据连接共享节点的位线中流动电流输出放大电流。

附图说明

29.本发明的特征对于本领域技术人员来说可通过参考附图的描述而显而易知。应当理解,附图只是用来描述本发明的代表性实施方式,而非限制本发明的范围。本发明通过附图进行具体的描述,其中:

30.图1为现有乘法累加器(mac)阵列的简化功能方块图;

31.图2为电子突触电路阵列之简化功能方块图;

32.图3为本发明的一种实施方式的简化功能方块图;

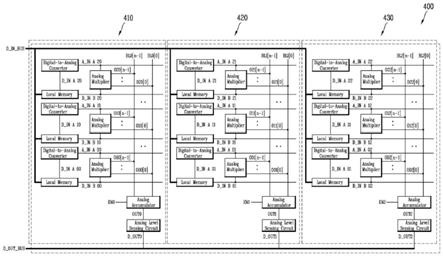

33.图4为本发明的一种实施方式的功能方块图;

34.图5为从图4所示mac阵列取得的另一乘法累加器阵列(mac array);

35.图6和图7为分别从图4和图5所示mac阵列取得的另一乘法累加器阵列(mac array);

36.图8为从图4所示mac阵列取得的另一乘法累加器阵列(mac array);

37.图9为从图8所示mac阵列取得的另一乘法累加器阵列(mac array);

38.图10和图11分别为从图8和图9取得的其他提出的mac阵列;

39.图12根据本发明描述例示性模拟乘法器电路;

40.图13描绘用于图12中所涉及乘法器电路的例示性电压控制可变电阻;

41.图14描绘用于图12中模拟乘法器电路的例示性电压控制可变电阻;

42.图15为根据一种实施方式描述模拟乘法器电路阵列的代表性示意图;

43.图16为根据一种实施方式描述模拟乘法器电路阵列的代表性示意图;

44.图17为根据本发明一种实施方式具有差动电压形可变电阻的模拟乘法器电路的一些示意电路图;

45.图18为根据一种实施方式描述模拟乘法器电路阵列的代表性示意图;

46.图19为根据一种实施方式描述模拟乘法器电路阵列的代表性示意图;

47.图20为根据本发明一种实施方式是具有逻辑兼容闪存的差动模拟乘法器的示意电路图;

48.图21为根据本发明一种实施方式是差动模拟乘法器阵列的代表性示意图;

49.图22为根据本发明一种实施方式是差动模拟乘法器阵列的代表性示意图;

50.图23为根据本发明描述例示性模拟累加器电路;

51.图24为根据本发明描述其他例示性电阻r,可谨慎挑选分压电压以设定晶体管操作模式;以及

52.图25为根据本发明描述含有差动尺度因子的例示性计算。

具体实施方式

53.在下文中,将对本发明的某些实施方式进行描述。为了解释的目的,阐述了具体配置和细节以便提供对实施方式的理解。然而,本领域的技术人员应当能够理解,在没有具体细节的情况下也可以实施本发明。此外,为了不使实施方式的描述产生混淆,通常省略或简化本发明固有的一部分并且对本领域技术人员来说基本的公知特征。下面结合附图描述本发明的进一步细节。

54.图3描述本发明的一种实施方式的简化功能方块图。mac阵列300配置为具有输入/输出(i/o)总线以从数字接口输入或输出数字值。在此阵列中,模拟乘法器(analog multiplier)、模拟加法器(analog adder)以及模拟累加器(analog accumulator)器配置为处理从数据输入总线d_in_bus处理数据并输出处理后数值至数据输出总线d_out_bus。亦即,数字-模拟接口(digital-analog interface)接收数字数据且转换接收的数字数据为模拟信号。在mac阵列300中单位单元(例如,模拟乘法器、模拟加法器和模拟累加器)处理模拟信号。模拟乘法器提供作为第一操作数x之转换后模拟输入和作为第二操作数y之第二数字输入或转换后模拟输入的乘积。第二操作数y能表示为结合特定模拟乘法器的过滤系数或权重参数。模拟乘法器从第一操作数x和第二操作数y产生多个部分乘积。对应的模拟加法器接着加总那些部分乘积。

55.在模拟加法器的末端,模拟累加器累加总计后部分乘积以产生模拟输出。然后,数字-模拟接口转换累加后模拟输出为数字输出。接着借由数据输出总线d_out_bus输出或反馈这些转换后数字输出作为下一层人工神经网络系统的输入之一。针对单一mac运作,一个操作数(从数据输入总线d_in_bus)的每个数字和其他操作数(也从数据输入总线d_in_bus)的每个数字相乘以形成部分乘积,模拟加法器相加这些结果(其为前述的部分乘积),接着模拟累加器累加这些结果并将其转换为数字输出后透过数据输出总线d_out_bus完成。那些模拟电路不必需要全电压摆幅作为关键运算。它们能够在单一导线携带多位信息,可适用在近似可计算应用程序上,例如视觉、语言处理以及信道编码支持的模拟前端,以修正数据路径错误。

56.图4描述本发明的一种实施方式的功能方块图。然而,本发明不限定于此种特定配置。于此,乘法累加器阵列400包括分别单行组成的多个mac电路组410、420和430,各mac电路组410、420和430包括多个mac单元以行和列构成矩阵。各mac电路组410、420和430包括模拟累加器(analog accumulator)以及与之互相连接的模拟位准感测电路(analog level sensing circuit)。虽然所示为mac单元以三行和三列组成在mac阵列400中,应理解的是能形成mac单元之各式各样组合的行数和列数,其仅可被特定芯片架构所限制。

57.所述三个mac电路组410、420和430透过数据输入总线d_in_bus和数据输出总线d_out_bus一起连接,使得各mac电路组410、420和430具备从输入总线d_in_bus之相同数字输入并于数据输出总线d_out_bus相加各部分数字乘积。在各mac电路组410、420和430中,三个mac单元排列于三行一列,并且能借由电性连接模拟累加器(analog accumulator)的一条或多条位线(bl[0]、bl[1]、bl[2]等)互相连接。各mac单元包括(1)区域内存(local memory),(2)数字/模拟转换器(digital-to-analog converter,dac),以及(3)模拟乘法器(analog multiplier)。区域内存配置为储存区域乘法器数字输入向量的数字值,其为数字输入电压d_ina和d_inb。区域内存可为静态随机存取内存(sram)、只读存储器(rom)、一次

性可编程内存(otp)、单聚可抹式闪存(single-poly based eflash)、磁阻式随机存取存储器(mram)等。在系统启动程序当中,可在区域内存中编程数字输入电压d_inb的默认值,使得当数字输入电压d_ina为可用时能尽快实时执行。

[0058]

数字/模拟转换器产生对应其数字值的模拟电压位准。举例来说,数字/模拟转换器转换数字输入电压d_ina为模拟电压输入a_ina。在mac单元中各模拟乘法器接收模拟电压输入a_ina在模拟域(位准:从接地电压(gnd)至工作电压(vdd))及数字输入电压d_inb在数字域(位准:gnd或vdd)的两个电压输入,并在模拟域(亦即电流或电荷)中输入的乘积结果之对应的位线bl[n-1]~bl[0]中产生输出。然后借由对应的位元线加总部分乘积结果,用作模拟加法器。

[0059]

如图4所示,在二维的乘法累加器阵列400中,第一列的第一位线bl0[0]电性连接在三行和第1列的第一条线中多个模拟乘法器。第一列的第二位线bl0[1]可电性连接在三行和第1列的第二条线中多个模拟乘法器。同样地,第一列的第(n-1)位线bl0[n-1]可电性连接在三行和第1列的第n条线中多个模拟乘法器。在各mac组中那些位线组在阵列的边缘连接耦接模拟感测电路之对应的模拟累加器,使得累加后模拟输出转换为相应的二进制位,其透过数据输出总线d_out_bus接着输出。

[0060]

各模拟输出(o00,o10,o20等)标示为从对应乘法器来的部分乘积。模拟输出o00[0]标示为从第一行和第一列中的模拟乘法器传至(reaching)在第一组mac中bl0[0]的部分乘积。同样地,模拟输出o20[n-1]标示为从第三列和第一行中的模拟乘法器传至在第一组mac中bl0[n-1]的部分乘积。模拟乘法器的多个模拟输出(o2x~o0x)可累加在位线blx[n-1]~blx[0]上。举例来说,在第一组mac的第一位线bl0[0]中加总部分乘积o00[0]、o10[0]和o20[0]。在第一组mac的第n位线bl0[n-1]中加总部分乘积o00[n-1]、o10[n-1]和o20[n-1]。

[0061]

当模拟累加器透过启动信号en启动时,模拟累加器在输出线(out0~out2)进行累加运算。然后,馈入此结果至连接数据输出总线d_out_bus的模拟位准感测电路以产生数字输出d_out0~d_out2。借由快速提供新向量至模拟电压输入a_ina和数字输入电压d_inb,无须重新编程模拟乘法器即可实时运算两个向量的任何组合。作为实例,根据本案所提出的mac阵列,当模拟电压输入a_ina20、数字输入电压d_inb20、模拟电压输入a_ina10、数字输入电压d_inb10、模拟电压输入a_ina00、数字输入电压d_inb00具有对应数值为7、3、2、9、4、3的输入向量,然后乘法器之输出向量o20[n-1:0]、o10[n-1:0]、o00[n-1:0]具有其值为21=7

×

3、18=2

×

9、12=4

×

3的结果值,接着在输出线out0累加o20+o10+o00=21+18+12=51。一旦接收到此累加值,模拟位准感测电路转换此累加值为相应的二进制位,其接着由数据输出总线d_out_bus运载(carried)。

[0062]

图5描绘从图4所示mac阵列取得的另一乘法累加器阵列(mac array)的功能方块图。亦即,mac阵列500中三个mac电路组510、520和530的各mac单元进一步配置数字/模拟转换器(digital-to-analog converter,dac)以连接区域内存(local memory)和模拟乘法器(analog multiplier)。因此,模拟乘法器能接收一对从第一数字/模拟转换器dac来的模拟电压输入a_ina和第二数字/模拟转换器dac来的模拟电压输入a_inb,并使两个模拟域的输入相乘而在对应的位线bl产生乘积。

[0063]

图6描绘从图4所示mac阵列取得的另一乘法累加器阵列(mac array)的功能方块

sensing circuit)以产生数字输出d_out0~d_out2。

[0068]

图10和图11分别显示从图8和图9取得的其他mac阵列。在图10和图11中,位于同行的三个模拟乘法器(analog multiplier)接收共同的模拟差动输入电压a_ina_p和a_ina_n。更精确地,在第一行中模拟乘法器接收共同的模拟操作数的模拟差动输入电压a_ina_n0和a_ina_p0。在第二行中模拟乘法器接收共同的模拟操作数的模拟差动输入电压a_ina_n1和a_ina_p1。在第三行中模拟乘法器接收共同的模拟操作数的模拟差动输入电压a_ina_n2和a_ina_p2。于此,图8和图9中分开的同行数字/模拟转换器(模拟输入源)以共同的模拟输入源替换。因此,mac阵列可配置较少数目的数字/模拟转换器(digital-to-analog converter,dac),因而可减少dac的整体空间。能共有相同模拟电压位准的模拟差动输入电压a_ina_n0~2、a_ina_p0~2且其透过多行驱动。因为共有相同dac,减少整个区域内存规格所需的dac面积。在图11中,位于同行的三个模拟乘法器接收共同的模拟差动输入电压a_ina_nx和a_ina_px。

[0069]

图12根据本发明描述例示性模拟乘法器电路。模拟乘法器电路配置为透过处理与接收的数字输入信号相结合的模拟输入信号产生数字输出信号。具体而言,电路配置为在位线(bl)节点产生输出电流(out)以对应接收模拟电压输入a_ina和1位数字输入电压d_inb。各模拟乘法器电路包括(1)存取晶体管,用以从供应节点接收模拟电压输入a_ina,(2)可变电阻,用以储存以其电导(conductance)状态为基础的数据,以及(3)切换晶体管,具有闸极端以接收数字输入电压d_inb以控制输出电流位准。

[0070]

可变电阻r也为非易失性,所以其无须持续电能(power)即可保留储存数据。作为一种实施方式,因为可变电阻r于电路主动操作期间不能设定或修改其数值,可变电阻r于操作模拟乘法器电路前被配置为编程具有特定值。进一步的可变电阻r细节,将如图13和图14中所述。

[0071]

切换晶体管配置为根据数字元元输入电压(d_inb)而启动,以开启或停止模拟电压输入a_ina和可变电阻r编程后电导值的乘积结果。于运行电路期间,数字输入电压(d_inb)的量值动态改变(快速选择)切换晶体管的状态。更精确地,当数字输入电压d_inb为高电位(high)时则导通切换晶体管,在位线bl节点中电流输出量(out)可与模拟电压输入a_ina和默认的可变电阻r的电阻值倒数或其电导值的乘积结果成比例。另一方面,当数字输入电压d_inb变为低电位(low)时则关闭切换晶体管,电流输出量(out)可能降低至一般位准(trivial level)。亦即,当数字输入电压d_inb的低电位降低至一般位准,则确定保持切换晶体管在非导通状态。

[0072]

在图12(a)中,模拟乘法器电路1210配有电压控制可变电阻,其包括可变电阻r以及切换晶体管1214以根据施加其闸极端的数字输入电压d_inb控制位线bl上的输出电流。连接模拟电压输入a_ina之存取晶体管1212的源极区耦接可变电阻r的一端,可变电阻r的另一端耦接切换晶体管1214的汲极区。在图12(b)中,配置的模拟乘法器电路1220呈现出可变电阻r以及切换晶体管1224的配置,使得存取晶体管1222的源极区连接切换晶体管1224的汲极区和切换晶体管1224的源极区连接可变电阻r的一端。在图12(c)中,配置的模拟乘法器电路1230呈现出模拟乘法器电路1230配有电压控制可变电阻,其包括(1)一个切换晶体管1232根据施加切换晶体管1232的闸极端的数字输入电压(d_inb)来控制位线bl上的输出电流,(2)一个存取晶体管1234可操作来响应模拟电压输入a_ina,以及(3)可变电阻r。可

变电阻r配置为储存其电阻值的状态。

[0073]

图13根据一种实施方式描绘模拟乘法器电路的例示性记忆电阻。如图13所示(多闸闪存的电压控制可变电阻,voltage controlled variable resistor by multi-gate flash),图12中电压控制可变电阻可由一组闪存单元来配置。那些闪存单元相连地编排以透过其单元临界电压储存状态。各闪存单元可为浮动闸极内存晶体管,其具有耦接多条字符线(wl1,wl2,wl3等)之一的控制闸极。

[0074]

图13(a)显示图12所示的可变电阻r的部分。作为i型电压控制可变电阻(type i voltage controlled variable resistor)的一种实施方式,模拟乘法器电路1310包括电压控制可变电阻,其中闪存单元的源极端(未示出)连接切换晶体管s1的汲极端。再者,闪存单元1312的汲极端连接存取晶体管a1的源极端及闪存单元1312的源极端连接另一闪存单元的汲极端(未示出)。含括闪存单元1312之闪存单元的数量未明确描述,但应理解的是一个或多个闪存单元(浮动闸极晶体管)可如此串联编排。

[0075]

作为i型电压控制可变电阻(type i voltage controlled variable resistor)的另一种实施方式,模拟乘法器电路1320包括电压控制可变电阻,其中切换晶体管s2的源极端连接闪存单元1322的汲极端。再者,存取晶体管a2的源极端连接切换晶体管s2的汲极端及闪存单元的源极端(未示出)透过导线或另一串联连接的晶体管连接共享源极线(common source line)csl。

[0076]

作为ii型电压控制可变电阻(type ii voltage controlled variable resistor)的一种实施方式,模拟乘法器电路1330具有电压控制可变电阻,其包括(1)一个切换晶体管s3(2)一个存取晶体管a3,以及(3)至少一个闪存单元1332。亦即,切换晶体管s3的源极端连接存取晶体管a3的汲极端及存取晶体管a3的源极端连接闪存单元1332的汲极端。

[0077]

给定前述这些电路设计,当数字输入电压d_inb为高电位导通切换晶体管,在位线bl节点中电流输出量(out)可与模拟电压输入a_ina和默认的可变电阻r之电阻值倒数的乘积结果成比例。另一方面,当数字输入电压d_inb变为低电位而关闭切换晶体管,电流输出量(out)可能降低至一般位准。换句话说,当切换晶体管所接收之数字输入电压d_inb的低数值降低至一般位准,则确定保持切换晶体管在非导通状态。

[0078]

在图13(b)中,作为i型(type i)电压控制可变电阻的另一种实施方式,模拟乘法器电路1340包括由一个闪存单元1342组成的电压控制可变电阻。亦即,闪存单元1342具有闸极端来接收模拟电压输入a_inb(亦即,模拟电压输入位准于接地电压(gnd)和工作电压(vdd)之间)。在此状态中,模拟电压输入a_inb的位准能从图5、图7、图9和图11的模拟转换器dac驱动。位线(bl)的电流表示(1)仔细选择的模拟电压输入(a_ina或a_inb)和(2)可变电阻r的编程后电阻值之乘积结果。

[0079]

图14描绘用于图12中模拟乘法器电路的例示性内存电阻(逻辑闪存的电压控制可变电阻,voltage controlled variable resistor by logic flash)。于此,可变电阻r包括一个或多个读取(标准逻辑)晶体管,各读取晶体管透过作为充电储存节点的浮动闸极(fg)节点连接一对耦接晶体管。在图14(a)中,作为一种实施方式,模拟乘法器电路1410包括电压控制可变电阻,其包括一个读取(标准逻辑)晶体管1414配置为形成作为一对耦接晶体管1416和1417之充电储存节点的浮动闸极fg。亦即,第一晶体管1416连接编程字符线pwl

以提供编程电压至浮动闸极fg。第二晶体管1417连接写入字符线wwl以操作数据写入。虽然仅描述一个读取晶体管1414,应理解的是一个以上读取晶体管能串联编排以形成可变电阻r。当一个以上读取晶体管形成可变电阻r,第一读取晶体管维持第一对字符线(编程字符线pwl和写入字符线wwl),其从连接第二读取晶体管(未示出)的第二对字符线(未示出)分离。

[0080]

浮动闸极(fg)的节点电压可编程为目标特定值。因此,当数字输入电压d_inb为高电位“导通”选定的晶体管,在位线bl节点中电流输出量(out)可与默认的模拟电压输入a_ina和默认的可变电阻r之电导(其等同于可变电阻r之电阻值倒数)的乘积结果成比例。另一方面,当数字输入电压d_inb变为低电位(low)而关闭选定的晶体管,电流输出量(out)可能降低至一般位准。虽然展示读取晶体管或选定的晶体管的特定数目,应理解的是可串联连接读取晶体管及/或选定的晶体管的任何数目。

[0081]

读取晶体管1414具有(1)汲极端以连接存取晶体管1412的源极端来接收模拟电压输入a_ina以及(2)源极端以透过导线或多个读取晶体管(未示出)连接切换晶体管1418的汲极端来接收数字输入电压d_inb(二进制数字输入0和1)。切换晶体管1418配置为根据施加于切换晶体管1418的闸极端之数字输入电压(d_inb)启用或关闭位线中电流。

[0082]

作为i型电压控制可变电阻(type i voltage controlled variable resistor)的另一实施方式,模拟乘法器电路1420展示电压控制可变电阻,其中切换晶体管1424的源极端(未示出)连接读取晶体管1426的汲极端。再者,存取晶体管1422的源极端连接切换晶体管1424的汲极端及最后一个读取晶体管(未示出)的源极端透过导线或另一串联连接的晶体管(未示出)连接共享源极线csl。

[0083]

作为ii型电压控制可变电阻(type ii voltage controlled variable resistor)的一种实施方式,模拟乘法器电路1430具有电压控制可变电阻,其包括(1)一个切换晶体管1432(2)一个存取晶体管1434,以及(3)至少一个电压控制可变电阻。亦即,切换晶体管1432的源极端连接存取晶体管1434的汲极端及存取晶体管1434的源极端连接读取晶体管1436的汲极端。

[0084]

给定前述电路设计,当数字输入电压d_inb为高电位导通切换晶体管,在位线bl节点电流输出量(out)可与模拟电压输入a_ina和默认的可变电阻r之电阻值倒数的乘积结果成比例。另外,当数字输入电压d_inb变为低电位而关闭切换晶体管,电流输出量(out)可能降低至一般位准。换言之,当切换晶体管所接收数字输入电压d_inb的低数值降低至一般位准,则确保切换晶体管在非导通状态。

[0085]

在图14(b)中,作为i型电压控制可变电阻的另一种实施方式,模拟乘法器电路1440具有由一个或一个以上读取(标准逻辑)晶体管1444组成的电压控制可变电阻。亦即,第一晶体管1446和第二晶体管1447具有共享基极来接收模拟电压输入a_inb(亦即,模拟电压输入位准于接地电压(gnd)和工作电压(vdd)之间)。模拟电压输入a_inb的位准能从图5、图7、图9和图11的模拟转换器dac驱动。位线(bl)的电流表示(1)仔细选择的模拟电压输入(a_ina或a_inb)和(2)可变电阻r的编程后电阻值倒数之乘积结果(虚线中的方块)。

[0086]

图15根据一种实施方式描述模拟乘法器电路阵列的代表性示意图(“虚线方块”的电压控制可变电阻,voltage controlled variable resistor by)。图15描述三个(types i-iii)例示性阵列1510、1520和1530,其中一群4个模拟乘法器电路沿着单一电压源节点而联系。群中的各乘法器描述于图12中。各阵列中4个模拟乘法器配置为根据模拟电压输入a_

ina和4个数字输入电压d_inb[3]~d_inb[0]在4条位线(bl[3]~bl[0])中产生4个输出电流(o3~o0)。在阵列中的4条位线bl[3]、bl[2]、bl[1]和bl[0]设计为使得数字输入电压d_inb[3]为最高有效位(most significant bit,msb)及数字输入电压d_inb[0]为最低有效位(least significant bit,lsb)。

[0087]

在各阵列中切换晶体管s3、s2、s1和s0配置为启用(activate)或关闭(deactivate)输出电流,根据分别施加于切换晶体管s3、s2、s1和s0的闸极区而所接收的4个数字输入电压d_inb[3]~d_inb[0]而在4条位线(bl[3]~bl[0])中流动。可变电阻r3、r2、r1和r0可于运行电路前编程。再者,当尺度因子k(亦即,k=1,2,3等整数)被指定时,已编程电阻值能具有其数值以识别输出电流的来源(位线)。

[0088]

位线bl中输出电流可透过仔细选择的模拟电压输入a_ina(操作数x)和可变电阻r(操作数y)之电阻值倒数之乘积结果而决定。因此,一群可变电阻(r3、r2、r1和r0)能蓄意设定以识别位线(数字位置)中的输出电流。换言之,输出电流o1、o2和o3的量值可参考输出电流o0的量值来比例缩放。当尺度因子k参考输出电流o0所具有的量值1而设定为2,输出电流o0、o1、o2和o3的量值将达到1、2、4和8。设定尺度因子k是为了是为了准确区分位线上的其他输出电流。当对应的数字输入电压d_inb的位为高电位,输出电流o0~o3与仔细选择的模拟电压输入(a_ina或a_inb)和(2)可变电阻r的编程后电阻值倒数之乘积结果成比例。另外,当“低”数字信号(数字输入电压d_inb)使各切换晶体管s3、s2、s1和s0不启动,由位线(bl)流出输出电流o0~o3的量降低至一般位准。

[0089]

一对位线bl[3]、bl[2]、bl[1]和bl[0]中输出电流o0、o1、o2和o3借由模拟电压输入a_ina分别和数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]的特定组合而决定。因此,可连续地改变根据模拟电压输入和可变电阻r之编程后静态电阻的乘积输出(数据)。再者,透过提供新向量至模拟电压输入a_ina和数字输入电压d_inb,可实时运算两个向量的任何组合而无限制给定阵列中可变电阻总数的神经网络模型之可用乘积组合。

[0090]

图16根据一种实施方式描述模拟乘法器电路阵列的代表性示意图(i型逻辑闪存的电压控制可变电阻,type i voltage controlled variable resistor by logic flash)。在模拟乘法器电路阵列1600中,编程字符线pwl电性连接一对耦接晶体管的第一晶体管以施加编程电压至多个浮动闸极fg3、fg2、fg1和fg0。写入字符线wwl电性连接一对耦接晶体管的第二晶体管以操作数据写入。电路接收模拟电压输入a_ina和4个数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0],其中数字输入电压d_inb[3]为最高有效位及数字输入电压d_inb[0]为最低有效位,产生分别流动于位线bl[3]、bl[2]、bl[1]和bl[0]之作为结果的输出电流o3、o2、o1和o0。

[0091]

这是图14所示多位数字输入电压d_inb的执行。浮动闸极fg3、fg2、fg1和fg0的节点电压于操作前被编程特定值,使得输出电流o3~o0具有o3=k

×

o2、o2=k

×

o1和o1=k

×

o0(即k=1,2,3,等整数)的关系,并且当对应数字输入电压d_inb为高电位时,他们(输出电流o0~o3)与仔细选择的模拟电压输入a_ina和连接浮动闸极节点的nmos装置之有效电阻值的倒数之乘积结果成比例。另外,当“低电位”的各数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]分别使切换晶体管s3、s2、s1和s0不启动,如此流进位线bl[3]、bl[2]、bl[1]和bl[0]的输出电流的量降低至一般位准。

[0092]

图17根据本发明一种实施方式描述具有差动电压形可变电阻的模拟乘法器电路

的一些示意电路图。在图17中,各模拟乘法器电路1720、1740和1760包括连接可变电阻r的一对差动对n通道mos晶体管以及一个或多个切换晶体管。模拟乘法器配置为接收模拟差动输入电压(a_ina_p和a_ina_n)和数字输入电压d_inb,并分别在一对位线(bl和blb)中产生一对差动输出电流(o_p和o_n)。

[0093]

差动对n通道mos晶体管的第一mos晶体管具有闸极端来接收第一模拟差动输入电压a_ina_p。第一mos晶体管配置为根据第一模拟差动输入电压a_ina_p和数字输入电压d_inb的结合来产生在位线bl中流动的输出电流。差动对n通道mos晶体管的第二mos晶体管具有闸极端来接收第二模拟差动输入电压a_ina_n。第二mos晶体管配置为根据第二模拟差动输入电压a_ina_n和数字输入电压d_inb的结合来产生在位线bl中流动的输出电流。

[0094]

可变电阻r于操作乘法器前被编程为特定值。因此,当数字输入电压d_inb为高电位而导通切换晶体管时,作为一对位线(bl和blb)中两道电流之间差异的差动输出电流可与模拟电压输入a_ina和默认的可变电阻r的电阻值倒数或其电导值的乘积结果成比例。另一方面,当数字输入电压d_inb变为低电位而关闭切换晶体管,差动输出电流o_p和o_n可能降低至一般位准。亦即,当切换晶体管所接收之数字输入电压d_inb的低电位降低至一般位准,则确定保持切换晶体管在非导通状态。

[0095]

图17(a)描述一对mos晶体管d1和d2具有共享源极端连接可变电阻r的第一端。第一晶体管d1连接位线bl和可变电阻r的第一端。第二晶体管d2连接位线blb和可变电阻r的第一端。可变电阻r的第二端连接切换晶体管s1的汲极端。切换晶体管s1具有闸极端以接收数字输入电压d_inb和源极端连接共享源极线csl。切换晶体管s1配置为根据数字元元输入电压d_inb启用或关闭一对位线(bl和blb)中输出电流(o_p,o_n)。

[0096]

图17(b)描述差动模拟乘法器电路1740具有一对mos晶体管d3和d4,其具有共享源极端连接切换晶体管s2的汲极端。切换晶体管s2连接第一晶体管d3和第二晶体管d4和可变电阻r,使得切换晶体管s2根据施加于切换晶体管s2的闸极区而所接收的数字输入电压d_inb来启用或关闭一对位线中输出电流。可变电阻r连接切换晶体管s2和共享源极线csl。

[0097]

图17(c)描述差动模拟乘法器电路1760配置为串级配置。在图17(c)中,差动模拟乘法器电路1760包括一对mos晶体管d5和d6分别连接对应的切换晶体管s3和s4。亦即,第一晶体管d5和第二晶体管d6的汲极端分别连接切换晶体管s3和s4的源极端。切换晶体管s3和s4的闸极端被系在一起并配置为接收数字元元输入电压d_inb。一对mos晶体管d5和d6的共享源极端连接可变电阻r的一端。第一晶体管d5的闸极端配置为接收来自第一模拟电压源节点的模拟差动输入电压a_ina_p。第二晶体管d6的闸极端配置为接收来自第二模拟电压源节点的模拟差动输入电压a_ina_n。位线bl串联连接切换晶体管s3和第一晶体管d5,而位线blb串联连接切换晶体管s4和第二晶体管d6。切换晶体管s3和s4的各源极端和第一晶体管d5和第二晶体管d6的各汲极端一起结合以形成共同源极/汲极区。切换晶体管s3和s4具有闸极端以接收数字输入电压d_inb,并根据施加于切换晶体管s3和s4的闸极区而所接收的数字输入电压d_inb来使切换晶体管s3和s4启用或关闭一对位线bl和blb中输出电流。

[0098]

图18为根据一种实施方式之模拟乘法器电路阵列的代表性示意图。图18(a)描述模拟乘法器电路阵列1820包括4对模拟乘法器电路c0、c1、c2和c3,各对模拟乘法器电路c0、c1、c2和c3连接一对电压源节点以接收模拟差动输入电压a_ina_p和a_ina_n。各对模拟乘法器电路c0、c1、c2和c3包括一对差动对mos晶体管。一组差动对mos晶体管中第一晶体管

d1、d3、d5和d7配置为在其闸极端分别接收模拟差动输入电压a_ina_p。一组差动对mos晶体管中第二晶体管d2、d4、d6和d8配置为在其闸极端分别接收模拟差动输入电压a_ina_n。

[0099]

各个电路c0、c1、c2和c3的成对mos晶体管具有共享源极端以连接与切换晶体管连接的可变电阻r。四个可变电阻r3、r2、r1和r0分别连接成对mos晶体管d1/d2、d3/d4、d5/d6及d7/d8至4个切换晶体管s3、s2、s1和s0。各可变电阻r3、r2、r1和r0分别已编程为目标特定值。分别耦接可变电阻r3、r2、r1和r0的切换晶体管s3、s2、s1和s0,根据在切换晶体管s3、s2、s1和s0的闸极端分别接收的无符号数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]来启用或关闭流进4对位线bl[3]/blb[3]、bl[2]/blb[2]、bl[1]/blb[1]和bl[0]/blb[0]中输出电流。模拟乘法器电路c0、c1、c2和c3可使用在数字输入电压d_inb[3]表示最高有效位和数字输入电压d_inb[0]表示最低有效位。

[0100]

一旦被启动,各对模拟乘法器电路c0、c1、c2和c3就允许在位线bl和blb的节点中成对电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)。根据在位线bl的电流和在位线blb的电流之差计算差动输出电流。当切换晶体管s3、s2、s1和s0导通时,各位线bl的节点中电流量为模拟电压输入(操作数x)和预编程后对应的可变电阻r(操作数y)之电阻值倒数之乘积结果。四个切换晶体管s3、s2、s1和s0配置为根据在切换晶体管s3、s2、s1和s0的闸极端分别接收的无符号数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]启用或关闭流进4对位线bl[3]/blb[3]、bl[2]/blb[2]、bl[1]/blb[1]和bl[0]/blb[0]中输出电流(o3~o0)。

[0101]

四道差动输出电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)可参考第一差动输出电流(o_p0-o_n0)来比例缩放。当尺度因子k作为整数并参考第一差动输出电流(o_p0-o_n0)的量值1而设定为2,其余差动输出电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)的量值将达到8、4、2和1。设定尺度因子k是为了从位在线其他输出电流精确识别一道输出电流。因此,当4个数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]为高电位以导通选定的晶体管,在模拟乘法器电路阵列1820阵列的各对模拟乘法器电路c0、c1、c2和c3中差动输出电流(o_p-o_n)与目标默认差动输入电压(a_ina_p和a_ina_n)和可变电阻r3~r0的电阻导数值之乘积结果成比例。另一方面,当“低电位”数字输入电压(d_inb[3]、d_inb[2]、d_inb[1]、d_inb[0])使各切换晶体管(c3、c2、c1和c0)不启动时,差动输出电流o_p3~0和o_n3~0可能降低至一般位准。

[0102]

图18(b)描述模拟乘法器电路阵列1840包括4对模拟乘法器电路e3、e2、e1和e0,各对模拟乘法器电路e3、e2、e1和e0连接一对电压源节点以接收模拟差动输入电压a_ina_p和a_ina_n,其中各对模拟乘法器电路e3、e2、e1和e0如图17(b)所示。切换晶体管s3、s2、s1和s0连接差动放大器电路和4个可变电阻r3、r2、r1和r0,使得切换晶体管s3、s2、s1和s0根据在切换晶体管s3、s2、s1和s0的闸极端分别接收的无符号数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]来启用或关闭流进4对位线bl[3]/blb[3]、bl[2]/blb[2]、bl[1]/blb[1]和bl[0]/blb[0]中输出电流。

[0103]

图18(c)描述模拟乘法器电路阵列1860包括4对模拟乘法器电路f3、f2、f1和f0,各对模拟乘法器电路f3、f2、f1和f0连接一对电压源节点以接收模拟差动输入电压(a_ina_p和a_ina_n),其中各对模拟乘法器电路f3、f2、f1和f0如图17(c)所示。如图17(c)所述,各对模拟乘法器电路f3、f2、f1和f0配置为串级配置。亦即,模拟乘法器电路f3包括连接对应的

切换晶体管s1和s2之mos晶体管d1和d2。切换晶体管s1和s2也为mos晶体管来连接对应的mos晶体管d1和d2。具体而言,mos晶体管d1和d2的汲极端连接相应的切换晶体管s1和s2的源极端。切换晶体管s1和s2的闸极端被系在一起并配置为接收数字元元输入电压d_inb[3]。

[0104]

图18(c)描述模拟乘法器电路阵列1860包括4对模拟乘法器电路f3、f2、f1和f0,其各对连接一对电压源节点以接收模拟差动输入电压(a_ina_p和a_ina_n),其中各对模拟乘法器电路f3、f2、f1和f0如图17(c)所示。如图17(c)所示,各对模拟乘法器电路f3、f2、f1和f0配置为串级配置。亦即模拟乘法器电路f3包括连接对应的切换晶体管s1和s2之mos晶体管d1和d2。

[0105]

切换晶体管s1和s2也为mos晶体管来连接对应的mos晶体管d1和d2。亦即,mos晶体管d1和d2的汲极端连接相应的切换晶体管s1和s2的源极端。切换晶体管s1和s2的闸极端被系在一起并配置为接收数字元元输入电压d_inb[3]。一对mos晶体管d1和d2的共享源极端连接可变电阻r的一端。第一晶体管d1的闸极端配置为接收来自第一模拟电压源节点的模拟差动输入电压a_ina_p。第二晶体管d2的闸极端配置为接收来自第二模拟电压源节点的模拟差动输入电压a_ina_n。位线bl[3]串联连接切换晶体管s1和第一晶体管d1,而位线blb[3]串联连接切换晶体管s2和第二晶体管d2。切换晶体管s1和s2的各源极端和第一mos晶体管d1和第二mos晶体管d2的各汲极端一起结合以形成共同源极/汲极区。各切换晶体管s1和s2具有闸极端以接收数字输入电压d_inb[3],使得切换晶体管s1和s2分别根据施加于切换晶体管s1和s2的闸极区而所接收的数字输入电压d_inb[3]来启用或关闭位线bl[3]和blb[3]输出电流。其他模拟乘法器电路f2、f1和f0具有等同于模拟乘法器电路f3的架构,并且他们接收不同的数字输入电压d_inb[2]、d_inb[1]和d_inb[0]。

[0106]

图19根据一种实施方式为模拟乘法器电路阵列的代表性示意图。于此,模拟乘法器电路阵列配置多个mos晶体管。各模拟乘法器电路阵列1920、1940和1960包括1个符号选择单元和3个模拟乘法器单元。在各模拟乘法器电路阵列1920、1940和1960中模拟乘法器单元产生多个对电流o_p2/o_n2,o_p1/o_n1和o_p0/o_n0以分别流进多个对位线bl2/blb2,bl1/blb1和bl0/blb0。符号选择单元su包括第一对mos晶体管s1和s2和第二对mos晶体管s3和s4。

[0107]

在图19(a)中,符号选择单元(sign selection unit或sign selection block,su)包括4个mos晶体管s1、s2、s3和s4,其中各mos晶体管s1和s2的闸极配置为接收数字元元控制信号s及各mos晶体管s3和s4的闸极配置为接收与数字元元控制信号s互补的数字控制信号sb。在符号选择单元su中,配置两对mos晶体管s1/s2和s3/s4为运行,使得(1)启动后第一对晶体管s1/s2能供应第一的模拟差动输入电压a_ina_p至各组差动对两个晶体管的第一晶体管m1、m3和m5及第二模拟差动输入电压a_ina_n供应至各组差动对两个晶体管的第二晶体管m2、m4和m6,或使得(2)启动后第二对晶体管s3/s4能供应第一的模拟差动输入电压a_ina_p至各组差动对两个晶体管的第二晶体管m2、m4和m6及第二模拟差动输入电压a_ina_n供应至各组差动对两个晶体管的第一晶体管m1、m3和m5,其取决于数字控制信号s和数字控制信号sb之互补信号的状态。在位线bl/blb中流动的电流差异量值与施加于各晶体管(m1~m6)的差动输入电压成比例。

[0108]

在符号选择单元su中第一对mos晶体管s1和s2配置为透过在其闸极端接收数字控

制信号s而启动。在符号选择单元su中第二对mos晶体管s3和s4配置为透过在其闸极端接收数字控制信号sb而启动。数字控制信号s和数字控制信号sb彼此互相关联,使得(1)当数字控制信号s为高数字电位,则数字控制信号sb为低数字电位及(2)当数字控制信号sb为高数字电位,则数字控制信号s为低数字电位。因此,在各模拟乘法器电路中一对mos晶体管透过符号选择单元su中2对mos晶体管而驱动模拟差动输入电压a_ina_p或a_ina_n输入。

[0109]

当数字控制信号s为高数字电位,而数字控制信号sb为低数字电位,数字控制信号s(1)导通mos晶体管s1而使模拟差动输入电压a_ina_p启动第一晶体管m1、m3和m5,使得差动输出电流o_p2、o_p1和o_p0分别流进位线bl[2]、bl[1]和bl[0],并且数字控制信号s(2)导通mos晶体管s2使模拟差动输入电压a_ina_n启动第二晶体管m2、m4和m6,使得差动输出电流o_n2、o_n1和o_n0分别流进位线blb[2]、blb[1]和blb[0]。同样地,当数字控制信号sb为高数字电位,而数字控制信号s为低数字电位,数字控制信号sb(1)导通mos晶体管s3而使模拟差动输入电压a_ina_p启动第二晶体管m2、m4和m6,使得差动输出电流o_n2、o_n1和o_n0分别流进位线blb[2]、blb[1]和blb[0],并且数字控制信号s(2)导通mos晶体管s4使模拟差动输入电压a_ina_n启动第一晶体管m1、m3和m5,使得差动输出电流o_p2、o_p1和o_p0分别流进位线bl[2]、bl[1]和bl[0]。各模拟乘法器中晶体管对m1/m2、m3/m4和m5/m6所产生的差动输出电流借由从位线bl[2]、bl[1]和bl[0]中电流量分别减去位线blb[2]、blb[1]和blb[0]中电流量而决定。

[0110]

另一方面,当“低电位”数字输入电压d_inb[2]、d_inb[1]和d_inb[0]不启动切换晶体管sw2、sw1和sw0,对应位线(bl[2]~bl[0]和blb[2]~bl[0])中差动输出电流量(o_p2~o_p0和o_n2~o_n0)可能降低至一般位准。

[0111]

可变电阻r2、r1和r0于运行电路前编程为特定值。3道差动输出电流(o_p2-o_n2)、(o_p1-o_n1)、(o_p0-o_n0)可参考第一的差动输出电流(o_p0-o_n0)来比例缩放。当尺度因子k作为整数并参考第一差动输出电流(o_p0-o_n0)的量值1而设定为2,其余差动输出电流(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)的量值将达到4、2和1。设定尺度因子k是为了从位在线其他输出电流精确识别一道输出电流。因此,当数字控制信号s变为高电位以导通选定的晶体管,在阵列中各模拟乘法器电路中差动输出电流(o_p-o_n)与目标默认差动输入电压(a_ina_p和a_ina_n)和可变电阻r2~r0的电阻导数值之乘积结果成比例。另一方面,当“低电位”数字输入电压(d_inb[2]、d_inb[1]、d_inb[0])使各切换晶体管sw2、sw1和sw0不启动时,差动输出电流(o_p2~0和o_n2~0)可能降低至一般位准。

[0112]

图19(b)描述模拟乘法器电路阵列1940包括如图19(a)所示的符号选择单元su和3对模拟乘法器电路e2、e1和e0,其各对连接一对电压源节点以提供模拟差动输入电压a_ina_p和a_ina_n,其中模拟乘法器如图17(b)所示。切换晶体管sw2、sw1和sw0连接差动放大器电路和3个可变电阻r2、r1和r0,使得切换晶体管sw2、sw1和sw0根据在切换晶体管sw2、sw1和sw0的闸极端分别接收的无符号数字输入电压d_inb[2]、d_inb[1]和d_inb[0]来启用或关闭流进3对位线bl[2]/blb[2]、bl[1]/blb[1]和bl[0]/blb[0]中输出电流。图19(c)描述模拟乘法器电路阵列1960包括如图19(a)所示的符号选择单元su和3对模拟乘法器电路f2、f1和f0,各对模拟乘法器电路f2、f1和f0连接一对电压源节点以提供模拟差动输入电压a_ina_p和a_ina_n,其中模拟乘法器如图17(c)所示。

[0113]

图20根据本发明一种实施方式是具有逻辑兼容闪存的差动模拟乘法器的示意电

路图。在图20中,模拟乘法器电路2000配置为接收一对模拟差动输入电压a_ina_p和a_ina_n及1位数字输入电压d_inb,并产生作为结果的差动输出电流对o_p和o_n至一对位线bl和blb。此乘法器为图17中一对差动mos晶体管的结合而可变电阻r为图14中所示。差动对mos晶体管包括一对mos晶体管m10、m12共有连接读取晶体管2020的汲极端的共享源极端,读取晶体管2020具有控制闸极端连接一对耦接晶体管c1和c2并透过浮动闸极(fg)作为电荷储存节点。一对mos晶体管m10、m12分别接收一对模拟差动输入电压a_ina_p和a_ina_n。

[0114]

读取晶体管2020具有控制闸极端连接一对耦接晶体管c1和c2并透过浮动闸极fg作为电荷储存节点。耦接晶体管c1连接编程字符线pwl以提供编程电压至浮动闸极fg。耦接晶体管c2连接写入字符线wwl以操作数据写入。切换晶体管2040的汲极端连接读取晶体管2020的源极端,而切换晶体管2040的源极端连接共享源极线csl。切换晶体管2040配置为根据施加于切换晶体管2040的闸极区而所接收的数字输入电压d_inb来启用或关闭位线中电流。

[0115]

浮动闸极fg节点电压可编程为目标特定值,并且当数字输入电压d_inb为高电位来“导通”选定的晶体管,差动输出电流对的电流量(o_p和o_n)可与默认的差动输入电压(a_ina_p和a_ina_n)和逻辑兼容闪存的读取晶体管2020的电导的乘积结果成比例。另一方面,当数字输入电压d_inb变为低电位而关闭选定的晶体管,电流输出量(o_p和o_n)可能降低至一般位准。虽然展示读取晶体管或选定的晶体管的特定数目,应理解的是可串联连接读取晶体管及/或选定的晶体管的任何数目。

[0116]

图21为根据本发明一种实施方式差动模拟乘法器阵列的代表性示意图。在图21中,提供差动输入电压a_ina_p和a_ina_n的一对差动输入信号源线连接4个差动模拟乘法器。在阵列中具有逻辑兼容闪存的各差动模拟乘法器如前述图20所描述。提供编程电压至编程字符线pwl的浮动闸极fg3、fg2、fg1和fg0连接各逻辑兼容闪存中第一耦接晶体管。操作数据写入的写入字符线wwl连接各逻辑兼容闪存中第二耦接晶体管。切换晶体管s3、s2、s1和s0配置为根据数字元元输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]启用或关闭位线bl[3]/blb[3]、bl[2]/blb[2]、bl[1]/blb[1]和bl[0]/blb[0]中流动的4对差动输出电流。浮动闸极fg3、fg2、fg1和fg0已编程为特定值。换句话说,差动输出电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)的量值可参考差动输出电流(o_p0-o_n0)的量值来比例缩放。

[0117]

尺度因子k作为整数,当尺度因子k参考差动输出电流(o_p0-o_n0)所具有的量值1而设定为2,差动输出电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)的量值将达到8、4、2和1。设定尺度因子k是为了从位在线其他输出电流精确识别一道输出电流。位线的电流为默认输入电压信号(操作数x)和读取晶体管的电导(操作数y)之乘积结果。因此,当4个数字输入电压d_inb[3]、d_inb[2]、d_inb[1]和d_inb[0]为高电位以导通选定的晶体管,在模拟乘法器电路阵列2100的各对模拟乘法器电路e0、e1、e2和e3中差动输出电流(o_p3-o_n3)、(o_p2-o_n2)、(o_p1-o_n1)和(o_p0-o_n0)与目标默认差动输入电压(a_ina_p和a_ina_n)和连接浮动闸极fg3、fg2、fg1和fg0之nmos装置的电导之乘积结果成比例。另一方面,当数字输入电压(d_inb[3]、d_inb[2]、d_inb[1]、d_inb[0])之任一变为低电位关闭对应的切换晶体管(s3~s0)时,差动输出电流(o_p3~0和o_n3~0)可能降低至一般位准。亦即,当数字输入电压d_inb[3]、d_inb[2]、d_inb[1]或d_inb[0]为低电位,则确定保持

切换晶体管在非导通状态,并且对应位线中电流量可降低至一般位准。

[0118]

图22为根据本发明一种实施方式差动模拟乘法器阵列的代表性示意图。模拟乘法器电路阵列2200包括1个符号选择单元和3个模拟乘法器单元。符号选择单元如图19所描述,而模拟乘法器电路如图20所描述。模拟乘法器电路阵列2200中3对模拟乘法器电路f2、f1和f0在多个对位线(bl2/blb2~bl0/blb0)中分别产生多个对差动输出电流(o_p2/o_n2~o_p0/o_n0)。符号选择单元su包括第一对mos晶体管s1和s2和第二对mos晶体管s3和s4。

[0119]

在位线(bl2/blb2~bl0/blb0)中流动的差动输出电流(o_p2/o_n2~o_p0/o_n0)量值与施加于第一对mos晶体管s1和s2和第二对mos晶体管s3和s4的差动输入电压a_ina_p和a_ina_n成比例。当数字控制信号s为高电位时,响应差动输入电压a_ina_p而产生的差动输出电流(o_p2~0)流动在位线(bl2~0),而响应差动输入电压a_ina_n而产生的差动输出电流(o_n2~0)流动在位线(blb2~0)。当数字控制信号s为低电位时,响应差动输入电压a_ina_n而产生的差动输出电流(o_p2~0)流动在位线(bl2~0),而响应差动输入电压a_ina_p而产生的差动输出电流(o_n2~0)流动在位线(blb2~0)。各模拟乘法器f2、f1和f0中晶体管对(m10/m20、m30/m40、m50/m60)所产生的差动输出电流(o_p2/o_n2~o_p0/o_n0)借由从位线bl2~0中电流量分别减去位线blb2~0中电流量而决定。

[0120]

在符号选择单元su中第一对mos晶体管s1和s2配置为透过在其闸极接收数字控制信号s而启动。在符号选择单元su中第二对mos晶体管s3和s4配置为透过在其闸极接收数字控制信号sb而启动。数字控制信号s和数字控制信号sb彼此互相关联,使得(1)当数字控制信号s为高数字电位,则数字控制信号sb为低数字电位及(2)当数字控制信号sb为高数字电位,则数字控制信号s为低数字电位。因此,在各模拟乘法器电路f3~f0中一对mos晶体管透过符号选择单元su中su的两对mos晶体管而驱动模拟差动输入电压a_ina_p或a_ina_n输入。

[0121]

当第一对mos晶体管s1和s2随着高数字电位的数字控制信号s而启动,模拟差动输入电压(a_ina_p)连接3个模拟乘法器电路f3~f0的上部输入线,而其他模拟差动输入电压(a_ina_n)连接3个模拟乘法器电路f3~f0的下部输入线。同样地,当第二对mos晶体管(s3和s4)随着高数字电位的数字控制信号sb而启动,模拟差动输入电压(a_ina_p)连接3个模拟乘法器电路f3~f0的下部输入线,而其他模拟差动输入电压(a_ina_n)连接3个模拟乘法器电路f3~f0的上部输入线。

[0122]

因此,当数字控制信号s为高电位及数字控制信号sb为低电位,然后启动后nmos晶体管透过上部输入线和下部输入线供应模拟差动输入电压a_ina_p和a_ina_n至对应对nmos晶体管的闸极。因此,成对晶体管分别启用差动输出电流o_p2~0和o_n2~0。当数字控制信号s为低电位及数字控制信号sb为高电位,然后启动后nmos晶体管透过上部输入线和下部输入线供应模拟差动输入电压a_ina_p和a_ina_n至对应对nmos晶体管的闸极。另一方面,当数字输入电压d_inb[2]、d_inb[1]、d_inb[0]之任一变为低电位关闭对应的切换晶体管时,差动输出电流o_p2~0和o_n2~0可能降低至一般位准。亦即,当数字输入电压d_inb[2]、d_inb[1]或d_inb[0]为低电位,则确定保持切换晶体管在非导通状态,并且对应位线中电流量可能降低至一般位准。

[0123]

图23根据本发明描述例示性模拟累加器电路。图23(a)描述例示性电流累加器(current accumulator)电路2320包括多个nmos晶体管。各nmos晶体管(2322、2324等)借由

其控制端连接内部启动节点en,并透过其源极端和汲极端连接位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]。因此,nmos晶体管(2322、2324等)可根据从内部启动节点en接收的高电位信号而在输出线out节点累加各位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]的电流。同样地,nmos晶体管(2322、2324等)可根据从内部启动节点en接收的低电位信号而在输出线out节点关闭各位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]的电流。

[0124]

图23(b)描述例示性电流累加器(current accumulator)电路2340包括多个pmos晶体管。各pmos晶体管(2342、2344等)借由其控制端连接内部启动节点enb,并透过其源极端和汲极端连接位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]。因此,pmos晶体管(2342、2344等)可根据从内部启动节点enb接收的低电位信号而在输出线out节点累加各位线bl[n-2]、bl[n-3]

…

bl[0]的电流。同样地,pmos晶体管(2342、2344等)可根据从内部启动节点enb接收的高电位信号而在输出线out节点关闭各位线bl[n-2]、bl[n-3]

…

bl[0]的电流。

[0125]

图23(c)描述一种例示性电流累加器电路2360,其包括多个cmos晶体管。多个cmos晶体管(2362、2364等)的第一控制闸极连接内部启动节点en。多个cmos晶体管(2362、2364等)的第二控制闸极连接内部启动节点enb。多个cmos晶体管(2362、2364等)的闸极端和汲极端连接多条位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]。因此,经由内部启动节点en的高电位信号和内部启动节点enb的低电位信号启动的多个cmos晶体管(2362、2364等)在输出线out节点累加位线bl[n-2]、bl[n-3]

…

bl[0]的电流。同样地,经由内部启动节点en的低电位信号和内部启动节点enb的高电位信号启动的多个cmos晶体管(2362、2364等)关闭在输出线out节点中位线bl[n-2]、bl[n-3]

…

bl[0]的电流。

[0126]

图23(d)描述一种例示性电流累加器电路具有多个电流镜电路2382、2384、2386和2388,各电流镜电路2382、2384、2386和2388具有多个对pmos晶体管。各电流镜电路2382、2384、2386和2388已配置为接收位线bl[n-1]、bl[n-2]、bl[n-3]和bl[0]的镜像电流1,并且提供放大后镜像电流m

n-1

、m

n-2

、m

n-3

和镜像电流1至其他分支及在输出线out节点累加这些镜像电流。在如图所示的配置中,各电流镜电路2382、2384、2386和2388包括一对pmos晶体管。在各电流镜电路2382、2384、2386和2388中成对晶体管的闸极端透过晶体管的共享闸极接点连接。在各电流镜电路2382、2384、2386和2388中,共享闸极接点连接晶体管的汲极和位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]之一。

[0127]

在各位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]中电流镜像至具有特定累加器尺度因子m(即m=1,2,3等整数)的晶体管之源极端和汲极端之间的通道。然后,一旦电流镜电路2382、2384、2386和2388启动,放大后镜像电流在输出线节点累加。举例来说,当电阻尺度因子k设定为1,累加器尺度因子m针对模拟累加器之最高有效位~最低有效位的位置而相应地可为2来比例缩放位线bl[n-1]、bl[n-2]、bl[n-3]

…

bl[0]的电流。在此状态中,电压控制可变电阻r可用于模拟累加器之最高有效位~最低有效位的位置。因为闪存的电阻值可于制造后调变,闪存或其他多级内存单元技术优于其他单位原内存,例如静态随机存取内存(static random access memory,sram)、只读存储器(read-only memory,rom)、一次性可编程内存(one-time programmable,otp)或磁阻式随机存取内存(magnetoresistive random access memory,mram)。

[0128]

图24描述根据本发明其他例示性电阻r。可谨慎挑选分压电压以设定晶体管操作模式。可使用二极管连接形式的nmos或pmos装置来移除分压电压。也可使用多二极管连接

形式的nmos或pmos装置来串联连接。仔细设定晶体管尺寸(transistor sizing),使得目标电阻值可透过晶体管表示。晶体管w/l的比值可针对不同位位置而相应地比例缩放。相似地,可交替使用长导线、多晶闸极来使电阻(resistant)装置针对从最高有效位至最低有效位的不同位位置适当地比例缩放。

[0129]

图25描述本发明含有尺度因子k和m的例示性操作计算。于此,产生输出的操作步骤概括如下:

[0130]

(1)接收模拟输入和数字输入数据;

[0131]

(2)根据等式计算部分输出:

[0132]on

=xk

(n-1)

,其中x为模拟输入,k为第一编程尺度因子,而n为具有单位元或多位数字;

[0133]

(3)借由以二进制元元形式相乘各部分乘积和二位元元输入数据来产生结合乘积;

[0134]

(4)施加第二放大因子(pn)于结合乘积,其中pn=mon,其中p是部分乘积,m是第二尺度因子;

[0135]

(5)相加多个部分乘积值以在定义的行形成部分总和;

[0136]

(6)针对其他定义行重复步骤(2)至(5);以及

[0137]

(7)从所有子值(sub-values)产生总值来提供模拟累加器(analog accumulator)。

[0138]

在图25(a)中,进行产生(7x3)+(2x6)+(4x1)之输出的操作步骤如图所示。于此,在步骤1,作为操作数x,数字7、2和4为模拟输入(a1、a2和a3)。作为操作数y,数字3、6和1(d1、d2和d3)转换为一组二进制数(011、110、001)来相乘。操作数x和操作数y的计算在单行中完成,因此,操作数x和操作数y之组件的3个计算透过三行(row 1、row 2和row 3)完成。

[0139]

作为操作数x,数字7、2和4为模拟输入(a1、a2和a3)。作为操作数y,数字3、6和1(d1、d2和d3)转为一组二进制数(011、110、001)来相乘。操作数x和操作数y的计算在单行中完成,因此,操作数x和操作数y之组件的三个计算透过三行(row 1、row 2和row 3)完成。

[0140]

在步骤2,透过施加放大因子(4,2,1)至第一输入7产生一组第一放大输出{28,14,7}。以参考单位元或多位的位置之尺度因子2为基础决定放大因子。因此,第一位取1、第二位取2和第三位取4作为放大因子。在步骤3,一组结合乘积{0,14,7}透过相乘第一组二进制数{0,1,1}和第一组放大乘积{28,14,7}而产生。在步骤4,第二组放大乘积{0,14,7}透过相乘第二因子(m=1)和第一放大乘积{0,14,7}而产生,其维持相同。在步骤5,第一部分乘积21透过相加第一结合乘积{0,14,7}的各元素而得出。

[0141]

根据步骤6,于步骤2,透过施加放大因子(4,2,1)至第二输入2产生第一组放大输出{8,4,2}。在步骤3,一组结合乘积{8,4,0}透过相乘第二组二进制数{1,1,0}和第一组放大乘积{8,4,2}而产生。在步骤4,第二组放大乘积{8,4,0}透过相乘第二因子(m=1)和一组结合乘积{8,4,0}而产生,其维持相同。在步骤5,第二部分乘积12透过相加第二结合乘积{8,4,0}的各元素而得出。

[0142]

根据步骤6,在步骤3,第一组放大输出{16,8,4}透过施加放大因子(4,2,1)至于第三输入4而产生。在步骤3,一组第一结合乘积{0,0,4}透过相乘第三组二进制数{0,0,1}和第三组放大乘积{16,8,4}而产生。在步骤4,第二组放大乘积{0,0,4}透过相乘第二因子(m

=1)和一组结合乘积{0,0,4}而产生。在步骤5,第三部分乘积4透过相加第三结合乘积{0,0,4}的各元素而产生。在步骤6,一旦前进至步骤7,执行整个三行(row1,row2,row3)的计算。在步骤7,总值37透过加总第一部分乘积21、第二部分乘积12和第三部分乘积4而作为(7x3)+(2x6)+(4x1)的输出。

[0143]

图25(b)描述实际进行相同操作步骤以产生如图24(a)所描述(7x 3)+(2x6)+(4x1)的输出。在步骤1,作为操作数x,数字7、2和4为模拟输入(a1、a2和a3)。作为操作数y,数字3、6和1(d1、d2和d3)转换为一组二进制数(011、110、001)来相乘。操作数x和操作数y的计算在单行中完成,因此,操作数x和操作数y之组件的3个计算透过三行(row1、row2和row3)完成。

[0144]

在步骤2,透过施加放大因子(1,1,1)至第一输入7产生一组第一放大输出{7,7,7}。以参考单位元或多位的位置之尺度因子1为基础决定放大因子。因此,第一位取1、第二位取1和第三位取1作为放大因子。在步骤3,一组结合乘积{0,7,7}透过相乘第一组二进制数{0,1,1}和第一组放大乘积{7,7,7}而产生。在步骤4,第二组放大乘积{0,14,7}透过相乘第二放大因子(4,2,1)和第一放大输出{0,7,7}而产生,其维持相同。在步骤5,第一部分乘积21透过相加第一结合乘积{0,14,7}的各元素而得出。

[0145]

根据步骤6,于步骤2,透过施加放大因子(1,1,1)至第二输入2产生第一组放大输出{2,2,2}。在步骤3,一组结合乘积{2,2,0}透过相乘第二组二进制数{1,1,0}和第一组放大乘积{2,2,2}而产生。在步骤4,第二组放大乘积{8,4,0}透过相乘第二因子(4,2,1)和一组结合乘积{2,2,0}而产生,其维持相同。在步骤5,第二部分乘积12透过相加第二结合乘积{8,4,0}的各元素而得出。

[0146]

根据步骤6,在步骤3,第一组放大输出{4,4,4}透过施加放大因子(1,1,1)至于第三输入4而产生。在步骤3,一组第一结合乘积{0,0,4}透过相乘第三组二进制数{0,0,1}和第三组放大乘积{4,4,4}而产生。在步骤4,第二组放大乘积{0,0,4}透过相乘第二因子(4,2,1)和一组结合乘积{0,0,4}而产生。在步骤5,第三部分乘积4透过相加第三结合乘积{0,0,4}的各元素而产生。在步骤7,总值37透过加总第一部分乘积21、第二部分乘积12和第三部分乘积4而作为(7x3)+(2x6)+(4x1)的输出。

[0147]

图25(c)描述实际进行相同操作步骤以产生如图24(a)所描述(7x 3)+(2x6)+(4x1)的输出,除了累加器整合于具有隐涵尺度因子m=1(未示出)的各行而无分离的累加器在末端之外。作为操作数x,数字7、2和4为模拟输入(a1、a2和a3)。作为操作数y,数字3、6和1(d1、d2和d3)转换为一组二进制数(011、110、001)来相乘。操作数x和操作数y的计算在单行中完成,因此,操作数x和操作数y之组件的3个计算透过三行(row1、row2和row3)完成。

[0148]

在步骤2,透过施加放大因子(4,2,1)至第一输入7产生一组第一放大输出{28,14,7}。以参考单位元或多位的位置之尺度因子2为基础决定放大因子。因此,第一位取1、第二位取2和第三位取4作为放大因子。在步骤3,一组结合乘积{0,14,7}透过相乘第一组二进制数{0,1,1}和第一组放大乘积{28,14,7}而产生。在步骤4,第一部分乘积21透过相加第一结合乘积{0,14,7}的各元素而得出。

[0149]

根据步骤6,于步骤2,透过施加放大因子(4,2,1)至第二输入2产生第一组放大输出{8,4,2}。在步骤3,一组结合乘积{8,4,0}透过相乘第二组二进制数{1,1,0}和第一组放大乘积{8,4,2}而产生。在步骤4,第二部分乘积12透过相加第二结合乘积{8,4,0}的各元素

而得出。

[0150]

根据步骤6,在步骤3,第一组放大输出{16,8,4}透过施加放大因子(4,2,1)至于第三输入4而产生。在步骤3,一组第一结合乘积{0,0,4}透过相乘第三组二进制数{0,0,1}和第三组放大乘积{16,8,4}而产生。在步骤4,第三部分乘积4透过相加第三结合乘积{0,0,4}的各元素而产生。

[0151]

在步骤6,一旦前进至步骤7,执行整个三行(row1,row2,row3)的计算。在步骤7,总值37透过加总第一部分乘积21、第二部分乘积12和第三部分乘积4而作为(7x3)+(2x6)+(4x1)的输出。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1