一种内存寻址切分方法及装置与流程

1.本发明涉及芯片设计领域,尤其涉及一种能够兼容不同大小内存的指令处理方法。

背景技术:

2.现有技术中针对存储芯片,通常是使用内存控制器控制不同的内存颗粒。以内存控制器为32位宽为例,32个io通常接8*4组不同的颗粒,而其中每个颗粒使用一个dqs(输入输出同步时钟),若需要降低成本,也有采用4个dq的内存颗粒的做法,一般情况下,就需要内存控制器的dqs同时连接到两个颗粒的dqs上。在读操作时,不同厂家的4dq内存共用一条dqs会遇到信号质量问题。

技术实现要素:

3.为此,需要提供一种能够兼容不同大小内存模块的应用方法;

4.为实现上述目的,发明人提供了一种内存寻址切分方法,包括如下步骤,在总线对内存控制器的访问指令输出到内存控制器之前,寻址单元依照对应的映射关系对访问指令中第一地址信息进行无效位填充,得到第二地址信息,将第二地址信息传输给内存控制器。

5.具体地,寻址单元依照对应的映射关系对访问指令中第一地址信息的首位进行无效位填充,得到调用指令,将调用指令传输给内存控制器。

6.具体地,所述第一地址信息包括行、列、区块或片选。

7.进一步地,所述内存控制器与不同大小的存储模块连接。

8.具体地,所述内存控制器采用针对其连接的最大容量的存储模块的寻址切分规则。

9.一种内存寻址切分装置,包括寻址单元、内存控制器、存储模块,所述寻址单元用于连接在内存控制器与总线之间,所述寻址单元用于总线对内存控制器的访问指令输出到内存控制器之前,寻址单元依照对应的映射关系对访问指令中第一地址信息进行无效位填充,得到第二地址信息,将第二地址信息传输给内存控制器。

10.具体地,寻址单元具体用于依照对应的映射关系对访问指令中第一地址信息的首位进行无效位填充,得到调用指令,将调用指令传输给内存控制器。

11.具体地,所述第一地址信息包括行、列、区块或片选。

12.进一步地,所述内存控制器与不同大小的存储模块连接。

13.进一步地,所述内存控制器采用针对其连接的最大容量的存储模块的寻址切分规则。

14.通过上述方案,内存控制器不需要获知自己连接的内存的具体大小,只需要根据寻址单元来的第二地址信息输入内存的内容进行查找即可。有助于实现内存的低成本制造。

附图说明

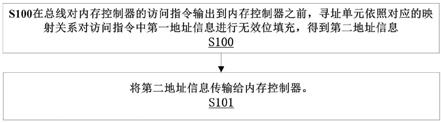

15.图1为本发明一实施方式所述的内存寻址切分方法流程图;

16.图2为本发明一实施方式所述的内存寻址切分装置模块图。

具体实施方式

17.为详细说明技术方案的技术内容、构造特征、所实现目的及效果,以下结合具体实施例并配合附图详予说明。

18.本文将介绍一种内存寻址切分方法,包括如下步骤,s100在总线对内存控制器的访问指令输出到内存控制器之前,寻址单元依照对应的映射关系对访问指令中第一地址信息进行无效位填充,得到第二地址信息,将第二地址信息传输给内存控制器。访问指令中可能包括包头、包尾、密钥等内容,具体地,还具备其需要访问的内存中的一个颗粒在整个内存中的位置,可以称为第一地址信息,所述第一地址信息具体可以包括行row、列col、区块bank或片选cs。在需要兼容不同大小的内存的实施例中,通常做法是两个不同大小的内存,小的内存的行或列的数目是大的内存数的一半,体现在第一地址信息中,便是行或列的数位少了一位。内存控制器通过相同的地址切分方式,用以确定行row、列col、区块bank或片选cs信息就会出错。这是由于地址切分方式都是从低位开始,向高位进行的。对此,解决方案是在接入不同大小的内存时对寻址单元进行相应的配置,例如寻址单元记录小内存相对应的列地址字符是10bit,大内存相对应的列地址字符是11bit,在接收到总线发送的对相对较小的内存控制器的访问指令输出到内存控制器之前,寻址单元依照对应的映射关系对访问指令中第一地址信息即列地址字符部分进行无效位填充,得到第二地址信息,该第二地址信息中的列地址字符为11bit,兼容了内存控制器对于其连接的最大容量的存储模块的寻址需求,由于第二地址信息的字符数位长度正常,内存控制器能够将行row、列col、区块bank或片选cs信息正确切分,再向内存寻址。对于修改后的列地址字符来说,虽然向小的内存进行寻址,由于其被填充的字符在首位,并不会影响数据的正常调用。从而我们通过上述方案,达到了在不改变内存控制器配置的情况下兼容不同大小的内存/存储模块的技术效果。

19.下面用实际应用例来进行相关的说明,例如cs0是2gbx32的存储模块(假定row=15位,bk=3位,col=11位,bw=2位)。cs1是1gbx32的存储模块(假定row=15位,bk=3位,col=11位,bw=2位)。常见的物理地址到dram时,row/bk/col的映射关系如下:其中s代表cs,r代表row,b代表bank,c代表col,w代表bw。可见在表示cs0的地址的时候字符串为:

20.srrr rrrr rrrr rrrr bbbc cccc cccc ccww

21.在表示cs1的地址的时候字符串为:

22.srr rrrr rrrr rrrr rbbb cccc cccc ccww

23.使用这样的映射关系的话,由于cs0有11个col位,所以总线看到的cs0地址空间是连续的,但是cs1只有10个col位。会导致在内存控制器处理的时候分割地址出现错误。当寻址单元进行无效位的填充就可以解决上面的问题。而更加举一反三地,在大小不同的存储模块连接到内存控制器上的时候,根据其编码规则的不同,可以事先地设置好在访问指令中的行或列或区块具体哪种地址的具体哪个数位有不同,需要在寻址的时候进行填充,能够获得正确的切分结果,在这一实施例中,则不要求补充的数位在第一地址信息的首位,更

好地解决了兼容不同大小的存储模块的问题。

24.在另一些具体的实施例中,寻址单元并不参与第一地址信息的切分处理,具体进行步骤,寻址单元依照对应的映射关系对访问指令中第一地址信息的首位进行无效位填充,得到调用指令,这里的调用指令仍然是一个指令包,将调用指令传输给内存控制器。由内存控制器进行具体地址的切分工作。

25.一种内存寻址切分装置,包括寻址单元10、内存控制器20、存储模块30,所述寻址单元用于连接在内存控制器与总线40之间,所述寻址单元用于总线对内存控制器的访问指令输出到内存控制器之前,寻址单元依照对应的映射关系对访问指令中第一地址信息进行无效位填充,得到第二地址信息,将第二地址信息传输给内存控制器。

26.具体地,寻址单元具体用于依照对应的映射关系对访问指令中第一地址信息的首位进行无效位填充,得到调用指令,将调用指令传输给内存控制器。

27.具体地,所述第一地址信息包括行、列、区块或片选。

28.进一步地,所述内存控制器与不同大小的存储模块连接。

29.进一步地,所述内存控制器采用针对其连接的最大容量的存储模块的寻址切分规则。

30.需要说明的是,尽管在本文中已经对上述各实施例进行了描述,但并非因此限制本发明的专利保护范围。因此,基于本发明的创新理念,对本文所述实施例进行的变更和修改,或利用本发明说明书及附图内容所作的等效结构或等效流程变换,直接或间接地将以上技术方案运用在其他相关的技术领域,均包括在本发明的专利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1