一种可动态配置的多核处理器容错系统

1.本发明涉及处理器技术领域,具体涉及一种可动态配置的多核处理器容错系统。

背景技术:

2.集成电路几十年的发展成果不仅给国家经济繁荣、社会进步和国家安全等方面提供了基本保障,并且也改变了人们的生产生活和思维方式。这跟数字soc(system on chip)芯片向小型化、轻量化、高性能和低功耗等特性发展密不可分,同时这些技术的发展也带来的更高的芯片处理器故障率。除了生活中的消费类电子产品中以外,工业生产中也更加依赖其发挥出的优势。相比消费类芯片,工业级芯片所处的环境更加恶劣,并且对可靠性的要求更高,出错代价更大。随着现代化应用场景对soc性能要求的提高,由于半导体工艺以及功耗的限制, 仅仅依靠提升单个核的频率难以继续维持摩尔定律, 因此同构多核处理器应运而生。同构多核处理器芯片汇集多个地位对等,结构相同的通用处理器核, 以最小的代价满足了提高系统性能,负载均衡,处理器容错的需要。

3.各种处理器故障类型中,软错误是导致处理器失效的主要原因,软错误主要来源于宇宙中的辐射和封装材料中的α粒子。对于处理器软错误的容错,从不同的抽象层次分成器件级、电路级和系统级。基于国内外相关容错研究,针对双模冗余的出错无法检测到出错处理器和三模冗余的占用资源过大的缺点,如何提高处理器冗余方式的灵活度和可配置性,是值得探究的一个主要问题。

技术实现要素:

4.为了解决现有技术中存在的上述技术问题,主要针对可靠性等级多样的芯片应用场景,针对双模冗余的出错无法检测到出错处理器和三模冗余的占用资源过大的缺点,为提高处理器冗余方式的灵活度和可配置性,本发明提供了一种可动态配置的多核处理器容错系统,其具体技术方案如下。

5.一种可动态配置的多核处理器容错系统,所述多核处理器为可重配置的三个处理器,该多核处理器容错系统通过三个处理器的配置静态配置为常规容错模式、可靠容错模式或性能模式,然后根据模式切换寄存器的模式切换命令使得多核处理器容错系统在常规容错模式、可靠容错模式性能模式之间相互切换,最后根据所要切换的模式对三个处理器进行相应的配置。

6.进一步的,当多核处理器容错系统切换至常规容错模式时,将三个处理器设置为双模锁步架构和单核独立运行的组合;当多核处理器容错系统切换至可靠容错模式时,将三个处理器设置组成为三模冗余;当多核处理器容错系统切换至性能模式时,将三个处理器设置为三核独立运行。

7.进一步的,所述常规容错模式采用双核锁步容错方法,将三个处理器设置为双模锁步架构和单核独立运行的组合,基于checkpoint的方法,双模锁步架构的两个处理器以主从模式运行,形成自监控对,从处理器接收与主处理器相同的输入数据流,执行相同的操

作,同时从处理器作为检查器,检查主处理器输出数据流的正确性并在主从处理器lockstep模块内进行比较后输出,同时对检查得到的正确状态进行实时的状态保存,当出现故障时,对主处理器和从处理器进行复位和状态加载。

8.进一步的,所述可靠容错模式即三模冗余模式,三模冗余的三个处理器都有相同的主处理器输入数据流,该输入数据流经过奇偶校验编码进行容错,每1bit数据流输出经过三模多数投票表决后给到主处理器的对外输出信号。

9.进一步的,当进行三模冗余模式时,当检测到有一个处理器的输出与其他两个处理器的输出不一致时,记录下当前出错处理器的出错次数,即出错计数器在每次记录到出错后加1,当计数器计数到一个可配置的值时,推测此处理器已经与其他两个处理器失步运行,通过复位重新加载正确状态完成再同步。

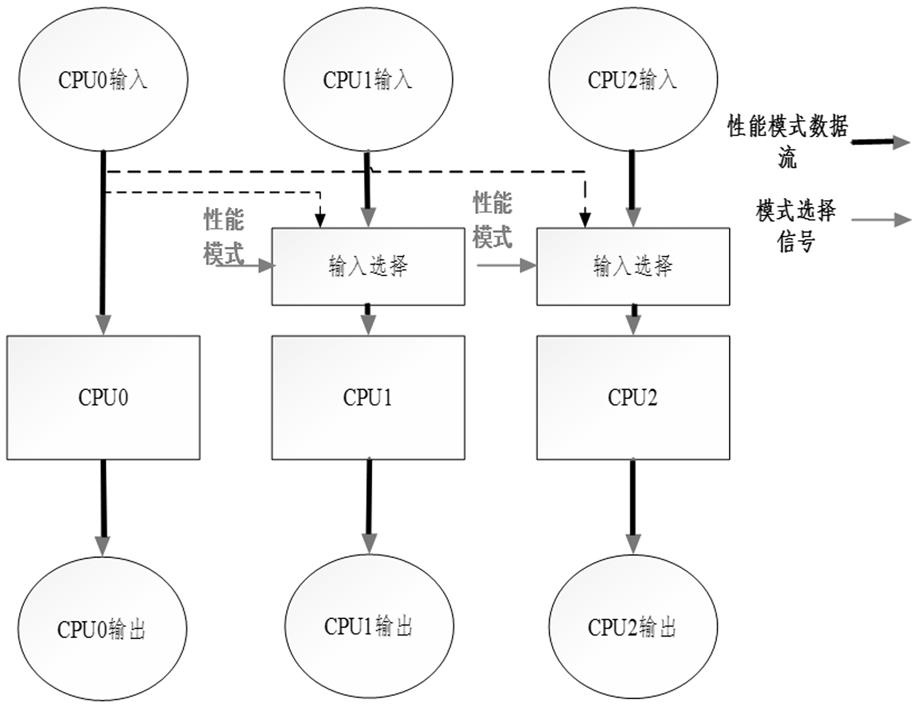

10.进一步的,所述性能模式下三个处理器独立工作,所述三个处理器的数据流的输入端选择每个处理器独立的输入,输出端每个处理器独立输出。

11.进一步的,性能模式与常规容错模式切换具体为:设系统开始时刻t0,三个处理器分别为cpu0、cpu1和cpu2,cpu0和cpu1独立运行代码,t1时刻对各自的运行状态进行checkpoint保存,cpu0保存状态checkpoint a1,cpu1保存状态checkpoint b1,用于后续的状态切换或者恢复;在t1~t2之间,cpu0和cpu1收到了双模冗余模式切换命令,但该命令在此时刻并没有生效,在t2时刻,cpu0执行了checkpointa2,a3的操作,cpu1执行了checkpointb2,b3的操作;t3时刻模式切换命令生效,将cpu1的输入信号切换成cpu0的输入,输出与cpu0进行错误监控对,对cpu0和cpu1同时进行复位,并且加载主核cpu0在发起模式转换命令之前保存的checkpointa1状态,cpu0和cpu1在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行常规容错模式。

12.进一步的,性能模式与可靠容错模式切换具体为:设系统开始时刻t0,三个处理器分别为cpu0、cpu1和cpu2独立运行代码,t1时刻对各自的运行状态进行checkpoint保存,cpu0保存状态checkpoint a1,cpu1保存状态checkpoint b1,cpu1保存状态checkpoint c1,用于后续的状态切换或者恢复;在t1~t2之间,3个处理器收到了可靠容错模式切换命令,但该命令在此时刻并没有生效,在t2时刻,cpu0执行了checkpointa2,a3的操作,cpu1执行了checkpointb2,b3的操作,cpu2执行了checkpointc2,c3的操作;t3时刻模式切换命令生效,将cpu1,cpu2的输入信号切换成cpu0的输入,三个处理器的输出经过多数投票表决后输出,对三个处理器同时进行复位,并且加载主核cpu0在发起模式转换命令之前保存的checkpointa1状态,cpu0、cpu1和cpu2在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行可靠容错模式。

13.进一步的,常规容错模式与可靠容错模式切换具体为:设系统开始时刻t0,三个处理器分别为cpu0、cpu1和cpu2,cpu0和cpu1以双模冗余方式运行代码,cpu2独立运行代码,t1时刻对各自的运行状态进行checkpoint保存,双模冗余模式保存状态checkpoint a1,cpu1保存状态checkpoint c1,用于后续的状态切换或者恢复;在t1~t2之间,3个cpu收到了三模冗余可靠容错模式切换命令,但该命令在此时刻并没有生效,在t2时刻,双模冗余模式执行了checkpointa2,a3的操作,cpu2执行了checkpointc2,c3的操作;t3时刻模式切换命令生效,将cpu2的输入信号切换成双模冗余模式的输入,三个处理器的输出经过多数投票表决后输出,对三个处理器同时进行复位,并且加载双模冗余模式在发起模式转换命令之

前保存的checkpointa1状态,cpu0、cpu1和cpu2在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行可靠容错模式。

附图说明

14.图1是本发明的可配置的三核工作模式状态示意图;图2是本发明的基于chenckpoint的dcls故障检测与恢复过程示意图;图3是本发明的常规容错模式下处理器的数据流流向示意图;图4是本发明的可靠容错模式下处理器的数据流流向示意图;图5是本发明的性能模式下处理器的数据流流向示意图;图6是本发明的性能模式与常规容错模式动态切换流程示意图;图7是本发明的性能模式与可靠容错模式动态切换流程示意图;图8是本发明的常规容错模式与可靠容错模式动态切换流程示意图。

具体实施方式

15.为了使本发明的目的、技术方案和技术效果更加清楚明白,以下结合说明书附图和实施例,对本发明做进一步详细说明。

16.为了满足数字芯片针对性能和可靠性需求的不同应用,达到资源可配置和高效率的要求,如图1所示,本发明提出的一种可动态配置的多核处理器容错系统允许在三种模式之间切换:对于可靠性至关重要的应用,本发明定义系统切换的此模式为可靠容错模式,即三模冗余模式,在该模式中,系统以经典的三模冗余,输出以多数投票表决的方式进行配置,同时该模式配备异步检测机制,防止处理器三模冗余系统中存在的失步问题;在性能模式下,三个处理器可以独立的进行工作,像常规的三核处理器一样实现独立执行代码,实现高性能处理功能;另外,本发明还提出了一种处于可靠容错模式和性能模式中间的常规容错模式,即其中处理器之间形成基于检查点的双模冗余模式,另外一个处理器可以独立工作,保证主核有一定容错能力的基础上,也保证了两个处理器系统的计算能力的性能;三种模式之间的切换是在软件控制下进行,通过配置特殊的模式切换寄存器的模式切换命令来触发三种模式之间的切换。除了可以静态配置3种特定的运行模式以外,还可以实现运行过程中的动态切换。其中,容错模块主要由两部分组成:故障检测和故障隔离与恢复,故障检测模块用于实时比较主从处理器的运行状态,并检测潜在的故障。

17.如图2

‑

3所示,所述常规容错模式采用双核锁步容错方法,即:系统为常规容错模式时,三个处理器设置为双模锁步架构和单核独立运行的组合。

18.具体的,基于checkpoint的方法,系统中双模锁步架构的两个处理器以主从模式运行,形成自监控对,主处理器cpu0直接控制外围设备,例如内存或外设模块。从处理器cpu1接收与主处理器cpu0相同的输入,因此常规容错模式下主从处理器对执行相同的操作。其中,所述从处理器cpu1作为检查器,输出未连接至外围组件,而是用于检查主处理器cpu0输出的正确性,进行实时的对比。

19.常规容错模式下三个处理器的输入输出数据流流向过程中,模式选择信号选择dmr,即双模冗余模式使能,则主处理器cpu0和从处理器cpu1的输入数据流都来自主处理器cpu0,输出在主从处理器lockstep模块内进行比较后输出,同时进行实时的状态保存,当出

现故障时,对cpu0和cpu1进行复位和状态加载,完成高效的故障恢复。

20.所述可靠容错模式为容错能力最高的模式,即三模冗余模式,三模冗余tmr具有保护时序电路和组合电路的能力,属于前向容错类型,不需要处理器返回之前的状态,三模冗余tmr对错误直接进行屏蔽,继续执行软件代码。三模冗余tmr更有效地实现主要集中在电路敏感逻辑中,例如处理器或者内存单元。它的主要目的是从电路中消除所有单点故障。三模冗余电路的每一组都有相同的一组输入,该输入经过奇偶校验编码进行容错,以避免由于错误输入的传播而发生错误。每1bit数据流输出经过三模多数投票表决逻辑实现,对于所有的单点故障能够达到自动检错的功能。

21.三模冗余的输入输出数据流流向如图4所示,选择工作模式为可靠容错模式,三个cpu的输入均来自主核cpu0,输出经过多数表决投票电路后给到主核的对外输出信号。

22.相比与双模冗余的容错存在无法对比获取具体出错处理器信息的局限性,三模冗余的在容错方面的一个重要优势是能够定位到出现故障的处理器,当进行三模冗余模式时,当检测到有一个cpu的输出与其他两个cpu的输出不一致时,此时系统记录下当前出错cpu的出错次数,即出错计数器在每次记录到出错后加1。如果计数器计数到一个可配置的较大的值,如连续16次投票均为处理器1与其他两个处理器的输出不一致,大概率推测此cpu已经与其他两个cpu失步运行,此时通过复位重新加载正确状态完成再同步。

23.所述性能模式下三个cpu独立工作,此时系统为正常的三核处理器系统,三个cpu拥有独立的系统总线,数据和指令存储。性能模式下三个cpu的输入输出数据流流向如图5所示,输入端选择每个cpu独立的输入,输出端每个cpu独立输出,三个cpu可以执行不同的代码,软件层面可以实现性能最大化,但是性能模式下cpu没有容错机制,一旦出现有效错误的产生并传播,可能会导致系统奔溃。

24.所述可相互切换的常规容错模式、可靠容错模式和性能模式,包括:当性能模式与常规容错模式切换时,具体为:性能模式下三个处理器cpu独立运行代码,常规容错模式下的cpu0和cpu1形成双模冗余dmr容错,cpu2还是独立运行代码。因此性能模式与常规容错模式切换主要考虑cpu0和cpu1的独立运行和形成dmr容错对的动态切换。切换流程如图6所示,假设系统开始时刻t0,cpu0和cpu1独立运行代码,t1时刻对各自的运行状态进行checkpoint保存,cpu0保存状态checkpoint a1,cpu1保存状态checkpoint b1,用于后续的状态切换或者恢复;在t1~t2之间,cpu0和cpu1收到了dmr模式切换命令,但该命令在此时刻并没有生效。在t2时刻,cpu0执行了checkpointa2,a3的操作,cpu1执行了checkpointb2,b3的操作;t3时刻模式切换命令生效,将cpu1的输入信号切换成cpu0的输入,输出与cpu0进行错误监控对,对cpu0和cpu1同时进行复位,并且加载主核cpu0在发起模式转换命令之前保存的checkpointa1状态,cpu0和cpu1在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行常规容错模式。

25.当性能模式与可靠容错模式时,具体为:性能模式下三个cpu独立运行代码,可靠容错模式下cpu0、cpu1和cpu2形成tmr前向容错,出错后继续向前执行,不会回退。因此性能模式与可靠容错模式切换主要考虑将cpu1和cpu2的独立运行同步到主核cpu0的运行状态,形成tmr容错的动态切换。切换流程如图7所示,假设系统开始时刻t0,cpu0、cpu1和cpu2独立运行代码,t1时刻对各自的运行状态

进行checkpoint保存,cpu0保存状态checkpoint a1,cpu1保存状态checkpoint b1,cpu1保存状态checkpoint c1,用于后续的状态切换或者恢复;在t1~t2之间,3个cpu收到了tmr可靠容错模式切换命令,但该命令在此时刻并没有生效。在t2时刻,cpu0执行了checkpointa2,a3的操作,cpu1执行了checkpointb2,b3的操作,cpu2执行了checkpointc2,c3的操作;t3时刻模式切换命令生效,将cpu1,cpu2的输入信号切换成cpu0的输入,三个cpu的输出经过多数投票表决后输出,对三个cpu同时进行复位,并且加载主核cpu0在发起模式转换命令之前保存的checkpointa1状态,cpu0、cpu1和cpu2在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行可靠容错模式。

26.当常规容错模式与可靠容错模式切换时,具体为:常规容错模式下cpu0和cpu1形成dmr容错,cpu2独立运行代码。因此常规容错模式与可靠容错模式切换主要考虑将cpu2的独立运行同步到cpu0和cpu1的dmr运行状态,形成tmr容错的动态切换。切换流程如图8所示,假设系统开始时刻t0,cpu0和cpu1以dmr方式运行代码,cpu2独立运行代码,t1时刻对各自的运行状态进行checkpoint保存,dmr保存状态checkpoint a1,cpu1保存状态checkpoint c1,用于后续的状态切换或者恢复;在t1~t2之间,3个cpu收到了tmr可靠容错模式切换命令,但该命令在此时刻并没有生效。在t2时刻,dmr执行了checkpointa2,a3的操作,cpu2执行了checkpointc2,c3的操作;t3时刻模式切换命令生效,将cpu2的输入信号切换成dmr的输入,三个cpu的输出经过多数投票表决后输出,对三个cpu同时进行复位,并且加载dmr在发起模式转换命令之前保存的checkpointa1状态,cpu0、cpu1和cpu2在复位后从0x0地址取回checkpointa1保存的下一个指令的地址,完成模式切换,运行可靠容错模式。

27.更具体的,由于checkpoint状态保存暂用的寄存器资源相对较多,并且动态切换的使用通常并不频繁,本发明的系统只对主核cpu0的寄存器进行硬件状态保存操作,对于cpu1和cpu2的checkpoint状态保存操作,采用软件的方式保存到片内sram,通常动态的操作对软件可以做到透明,因此只需要在收到模式切换信号的时候,软件执行checkpoint状态保存,在恢复的时候进行读取。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1