用于存储装置的编程方法与流程

1.本公开属于存储技术领域,涉及一种用于存储装置的编程方法,更特别是一种用于三维(3-dimentional)存储装置的编程方法。

背景技术:

2.随着集成电路中元件的关键尺寸逐渐缩小至工艺技术的极限,设计者已经开始寻找可达成更大存储器密度的技术,由此达成较低的位成本(costs per bit)。然而,随着技术趋势朝向缩小存储单元的尺寸与间距的方向发展,在存储单元进行编程操作期间的编程干扰问题变得越来越严重。

3.因此,降低存储装置被编程时的编程干扰(program disturbance)问题是相当重要的。

技术实现要素:

4.本公开有关于一种用于存储装置的编程(program)方法。

5.根据本公开的一方面,提供一种用于存储装置的编程方法。存储装置包含多个存储单元、一位线与多条字线。当存储装置处于一编程操作时,多个存储单元包含一选择存储单元与多个未选择存储单元。编程方法包含:进行多个预充电步骤、进行多个编程步骤以及在预充电步骤和编程步骤后,对选择存储单元进行验证步骤。每一预充电步骤包含对用以驱动未选择存储单元的位线施加预充电电压。每一编程步骤包含对多条字线中用以驱动选择存储单元的字线施加编程电压。

6.根据本公开的另一方面,提供一种用于存储装置的编程方法。存储装置包含多个存储单元、一位线与多条字线,当存储装置处于一编程操作时,多个存储单元包含一选择存储单元与多个未选择存储单元。编程方法包含:进行一第一预充电步骤、进行一第一编程步骤、进行多个第二预充电步骤以及进行多个第二编程步骤。第一预充电步骤包含对用以驱动未选择存储单元的位线施加预充电电压。第一编程步骤包含对多条字线中用以驱动选择存储单元的字线施加第一编程电压。每一第二预充电步骤包含对用以驱动未选择存储单元的位线施加预充电电压。每一第二编程步骤包含对多条字线中用以驱动选择存储单元的字线施加第二编程电压。第二编程电压和第一编程电压不同。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下。

附图说明

8.图1绘示存储装置;

9.图2a绘示根据一实施例的用于存储装置的编程方法;

10.图2b绘示根据一实施例的用于存储装置的编程方法的电压时序图;

11.图3绘示根据一实施例的用于存储装置的编程方法;

12.图4绘示以一实施例的编程方法编程的存储单元的测试结果;

13.图5绘示以一实施例的编程方法编程的存储单元的测试结果;

14.图6绘示根据一实施例的用于存储装置的编程方法;及

15.图7绘示根据一实施例的用于存储装置的编程方法。

16.【符号说明】

17.101:第一存储器串行

18.102:第二存储器串行

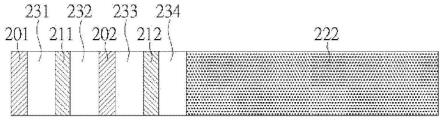

19.201,202,301~303,604,609,613,618,622,626:预充电步骤

20.211,212,311~313,601,606,611,615,620,624,628:编程步骤

21.231~234,331~336,602,605,607,610,612,614,616,619,621,623,625,627,629:处理步骤

22.222,322,603,608,617,630:验证步骤

23.bl_1,bl_2:位线

24.csl:共同源极线

25.dwlb0,dwlb1,dwlt0,dwlt1:虚置字线

26.gsl:接地选择线

27.mc_01,mc_11,mc_231,mc_241,mc_251,mc_461,mc_471,mc_02,mc_12,mc_232,mc_242,mc_252,mc_462,mc_472:存储单元

28.s1,s1_1,s2,s2_1,s3,s3_1,s4,s4_1:编程阶段

29.ssl 1,ssl 2:串行选择线

30.t1~t8:时间点

[0031]va

:脉冲电压

[0032]vdmy1

,v

dmy2

:虚置电压

[0033]vpass

:通过电压

[0034]vpgm

,v

pgm

1,v

pgm

2,v

pgm

3,v

pgm

4:编程电压

[0035]vpgm

1_1,v

pgm

2_1,v

pgm

3_1,v

pgm

4_1:编程电压

[0036]vpre

:预充电电压

[0037]

wl0~wl47:字线

具体实施方式

[0038]

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

[0039]

在本公开的实施例中,提出一种用于存储装置的编程方法,其可减少存储装置的编程干扰。编程方法可用于三维存储装置,例如三维与非门(nand)闪存存储器。

[0040]

须注意的是,本公开并非显示出所有可能的实施例,未于本公开提出的其他实施例也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本公开保护范围之用。另外,实施例中的叙述,例如细节结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本公开欲保护的范围做限缩。实施例的步骤和结构各的细节可在不脱离本公开的精神和范围内根据实际应

用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

[0041]

再者,说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等用词,是为了修饰权利要求的元件或步骤,其本身并不意含及代表该所请元件或步骤有任何之前的序数,也不代表某一所请元件或步骤与另一所请元件或步骤的顺序、或是施行上的顺序,这些序数的使用,仅是用来使具有某命名的一描述元件或步骤得以和另一具有相同命名的描述元件或步骤能作出清楚区分。

[0042]

适用于进行本公开的编程方法的存储装置可包含多个存储器串行(memory strings)、多条位线(bit lines)、多条串行选择线(string selectionlines)、多条字线(word lines)、多条接地选择线(ground selection lines)与多条共同源极线(common source lines)。为了便于说明,图1仅示例性地显示两个存储器串行。

[0043]

图1绘示存储装置。存储装置包含第一存储器串行101、第二存储器串行102、多条位线bl、多条串行选择线ssl、多条字线wl、接地选择线gsl与共同源极线csl。第一存储器串行101不同于第二存储器串行102,第一存储器串行101相邻于第二存储器串行102。

[0044]

第一存储器串行101包含多个存储单元mc(mc_01,mc_11

…

mc_231,mc_241,mc_251

…

mc_461,mc_471)。第二存储器串行102包含多个存储单元mc(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)。多条字线wl包含用以驱动存储单元mc_01与存储单元mc_02的字线wl0、用以驱动存储单元mc_471与存储单元mc_472的字线wl47、以及依序配置于字线wl0和字线wl47之间的多条字线wl1-wl46,存储单元mc_01与存储单元mc_02分别设置于第一存储器串行101与第二存储器串行102的下端,存储单元mc_471与存储单元mc_472分别设置于第一存储器串行101与第二存储器串行102的上端。字线wl1-wl46中的每一个分别用以驱动第一存储器串行101的存储单元mc_11

…

mc_231,mc_241,mc_251

…

mc_461中的每一个。字线wl1-wl46中的每一个分别用以驱动第二存储器串行102的存储单元mc_12

…

mc_232,mc_242,mc_252

…

mc_462中的每一个。此处所述的用以驱动存储单元的字线可代表,当施加于任一字线wl的电压值改变,作用于被此字线wl驱动的存储单元mc的电场值可随之改变。例如,当施加于字线wl0的电压值改变,作用于存储单元mc_01与存储单元mc_02的电场值可随之改变。

[0045]

第一存储器串行101电性连接于位线bl_1与共同源极线csl之间。第二存储器串行102电性连接于位线bl_2与共同源极线csl之间。具体而言,第一存储器串行101的通道线电性连接于位线bl_1与共同源极线csl之间,第二存储器串行102的通道线电性连接于位线bl_2与共同源极线csl之间。位线bl_1可用以驱动第一存储器串行101中的多个存储单元mc(mc_01,mc_11

…

mc_231,mc_241,mc_251

…

mc_461,mc_471)。位线bl_2可用以驱动第二存储器串行102中的多个存储单元mc(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)。在一实施例中,第一存储器串行101与第二存储器串行可电性连接于相同位线。此处所述的用以驱动存储单元的位线可代表,当施加于任一位线bl的电压值改变,作用于被此位线bl驱动的存储单元mc的电场值可随之改变。例如,当施加于位线bl_2的电压值改变,作用于第二存储器串行102的存储单元mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472的电场值可随之改变。

[0046]

串行选择线ssl_1与接地选择线gsl耦接于第一存储器串行101的相对两端。串行

选择线ssl_2与接地选择线gsl耦接于第二存储器串行102的相对两端。具体而言,串行选择线ssl_1耦接于位线bl_1与第一存储器串行101的存储单元mc_471之间;串行选择线ssl_2耦接于位线bl_2与第二存储器串行102的存储单元mc_472之间;接地选择线gsl耦接于共同源极线csl与第一存储器串行101的存储单元mc_01之间且耦接于共同源极线csl与第二存储器串行102的存储单元mc_02之间。在一实施例中,存储装置可包含多条串行选择线ssl耦接于位线bl_1与存储单元mc_471之间、和/或耦接于位线bl_2与存储单元mc_472之间。存储装置可还包含设置于字线wl47与位线bl之间的虚置字线dwlt0,dwlt1、以及设置于字线wl0与共同源极线csl之间的虚置字线dwlb0,dwlb1。

[0047]

当图1所示的存储装置处于编程操作期间时,多个存储单元mc的一个被选择以进行编程,且其他存储单元mc可被理解为未选择存储单元。例如,存储单元mc_241被选择且可被理解为选择存储单元,其他存储单元(即存储单元mc_01,mc_11

…

mc_231,mc_251

…

mc_461,mc_471和mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)可被理解为未选择存储单元,包含选择存储单元(mc_241)的第一存储器串行101可被理解为选择存储器串行,且包含未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的第二存储器串行102可被理解为未选择存储器串行。

[0048]

在编程操作期间,本公开的编程方法包含对第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)进行一个以上的预充电步骤,以关闭第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472),且抑制第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的编程。在编程操作期间,编程方法还包含对第一存储器串行101的选择存储单元(mc_241)进行一个以上的编程步骤,以编程选择存储单元(mc_241)。每一预充电步骤分别进行于每一编程步骤之前。在编程操作期间,编程方法还包含在预充电步骤和编程步骤后,对选择存储单元(mc_241)进行验证步骤,以验证选择存储单元(mc_241)是否被适当地编程。

[0049]

请同时参照图1、图2a与图2b图。图2a绘示根据一实施例的用于存储装置的编程方法。图2b图绘示图2a所示的用于存储装置的编程方法的电压(或偏压)时序图。图2b的纵轴表示提供至用以驱动选择存储单元(mc_241)的字线wl24、用以驱动未选择存储单元(mc_01,mc_11

…

mc_231,mc_251

…

mc_461,mc_471和mc_02,mc_12

…

mc_232,mc_252

…

mc_462,mc_472)的字线wl0-wl23,wl25-wl47、虚置字线dwlt0,dwlt1,dwlb0,dwlb1、耦接至第二存储器串行102中的未选择存储单元的串行选择线ssl_2、以及位线bl_2的电压(或偏压)。图2b的横轴表示时间,可依序包括时间点t1、时间点t2

…

至时间点t8。

[0050]

用于存储装置的编程方法包含在编程操作期间,进行多个预充电步骤201,202、进行多个编程步骤211,212、以及在多个预充电步骤201,202和多个编程步骤211,212后进行验证步骤222。编程方法可还包含在编程操作期间,进行于预充电步骤201和编程步骤211之间的处理步骤231、进行于编程步骤211和预充电步骤202之间的处理步骤232、进行于预充电步骤202和编程步骤212之间的处理步骤233、以及进行于编程步骤212和验证步骤222之间的处理步骤234。具体而言,预充电步骤201、处理步骤231、编程步骤211、处理步骤232、预充电步骤202、处理步骤233、编程步骤212、处理步骤234、以及验证步骤222可依序进行。

[0051]

例如,预充电步骤201可包含在时间点t1至时间点t2的时段期间(第一预充电期

间),对用以驱动第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的位线bl_2施加预充电电压v

pre

,以提升第二存储器串行102的通道电压,且在时间点t1至时间点t2的时段期间对串行选择线ssl_2施加脉冲电压va,以使第二存储器串行102连接位线bl_2。在预充电步骤201中,字线wl0-wl47与虚置字线dwlt0,dwlt1,dwlb0,dwlb1可为0伏特(v)。编程步骤211可包含在时间点t3至时间点t4的时段期间(第一编程期间),对用以驱动选择存储单元(mc_241)的字线wl24施加编程电压v

pgm

,以编程选择存储单元(mc_241),且在时间点t3至时间点t4的时段期间对字线wl0-wl23,wl25-wl47施加通过电压v

pass

。在一实施例中,通过电压v

pass

小于编程电压v

pgm

。在编程步骤211中,对虚置字线dwlt0,dwlb1施加虚置电压v

dmy1

,且对虚置字线dwlt1,dwlb0施加虚置电压v

dmy2

。在编程步骤211中,串行选择线ssl_2与位线bl_2可为0伏特。

[0052]

预充电步骤202可包含在时间点t5至时间点t6的时段期间(第二预充电期间),对用以驱动第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的位线bl_2施加预充电电压v

pre

,以提升第二存储器串行102的通道电压,且在时间点t5至时间点t6的时段期间对串行选择线ssl_2施加脉冲电压va,以使第二存储器串行102连接位线bl_2。在预充电步骤202中,字线wl0-wl47与虚置字线dwlt0,dwlt1,dwlb0,dwlb1可为0伏特。编程步骤212可包含在时间点t7至时间点t8的时段期间(第二编程期间),对用以驱动选择存储单元(mc_241)的字线wl24施加编程电压v

pgm

,以编程选择存储单元(mc_241),且在时间点t7至时间点t8的时段期间对字线wl0-wl23,wl25-wl47施加通过电压v

pass

。在编程步骤212中,对虚置字线dwlt0,dwlb1施加虚置电压v

dmy1

,且对虚置字线dwlt1,dwlb0施加虚置电压v

dmy2

。在编程步骤212中,串行选择线ssl_2与位线bl_2可为0伏特。虚置电压v

dmy1

可大于虚置电压v

dmy2

。虚置电压v

dmy1

与虚置电压v

dmy2

的值可介于脉冲电压va的值与通过电压v

pass

的值之间。

[0053]

处理步骤231可进行于时间点t2至时间点t3的时段期间。处理步骤232可进行于时间点t4至时间点t5的时段期间。处理步骤233可进行于时间点t6至时间点t7的时段期间。处理步骤234可进行于时间点t8之后。验证步骤222可进行于时间点t8之后且于处理步骤234之后。

[0054]

在一实施例中,预充电电压v

pre

可为4v,脉冲电压va可为3v,编程电压v

pgm

可为24v,通过电压v

pass

可为8v,虚置电压v

dmy1

与虚置电压v

dmy2

可介于3v至8v。第一预充电期间可等于第二预充电期间,例如,第一预充电期间与第二预充电期间可为6微秒(μs)。第一预充电期间可不同于第二预充电期间,例如,第一预充电期间可为7微秒,第二预充电期间可为5微秒。在一实施例中,用于不同预充电步骤的预充电电压v

pre

可为定值。

[0055]

图2a与图2b显示在编程操作期间,在一验证步骤之前包含两个预充电步骤与两个编程步骤的编程方法,然而,编程方法可包含更多验证步骤与更多编程步骤。例如,编程方法可包含n个预充电步骤与n个编程步骤,n个预充电步骤中的每一个分别进行于n个编程步骤中的每一个之前,且n大于1。在一实施例中,n个预充电步骤中的每一个可包含在一预充电期间对位线bl_2施加预充电电压v

pre

,n个编程步骤中的每一个可包含在一编程期间对用以驱动选择存储单元(mc_241)的字线wl24施加编程电压v

pgm

。预充电期间随着n值增加而减少,且编程期间随着n值增加而减少。在一实施例中,预充电期间和n值成反比,且编程期间和n值成反比。例如,当n值等于2,预充电期间可为6微秒,编程期间可为6微秒;当n值等于3,

预充电期间可为4微秒,编程期间可为4微秒;当n值等于6,预充电期间可为2微秒,编程期间可为2微秒。本公开不以此为限。在一实施例中,n个预充电步骤之间可不包含任何验证步骤,和/或n个编程步骤之间可不包含任何验证步骤。例如,预充电步骤201与预充电步骤202之间不包含任何验证步骤,和/或编程步骤211与编程步骤212之间不包含任何验证步骤。

[0056]

图3绘示根据另一实施例的用于存储装置的编程方法。编程方法可包含,在编程操作期间,在验证步骤322之前进行三个预充电步骤301,302,303与三个编程步骤311,312,313(n=3)。在图3所示的编程方法中,预充电步骤301、处理步骤331、编程步骤311、处理步骤332、预充电步骤302、处理步骤333、编程步骤312、处理步骤334、预充电步骤303、处理步骤335、编程步骤313、处理步骤336、以及验证步骤322可依序进行。预充电步骤301,302,303可相似于图2a与图2b所示的预充电步骤201,202,除了预充电期间不同。编程步骤311,312,313可相似于图2a与图2b所示的编程步骤211,212,除了编程期间不同。在一实施例中,预充电步骤301,302,303可进行于4微秒的预充电期间,编程步骤311,312,313可进行于4微秒的编程期间。

[0057]

图4绘示以一实施例的编程方法编程的存储单元的测试结果。在比较例中,在编程操作期间,编程方法仅包含一个预充电步骤(n=1),此预充电步骤进行于一验证步骤之前,且预充电步骤以12微秒的预充电期间进行。在实施例1中,在编程操作期间,编程方法包含两个预充电步骤(n=2),两个预充电步骤进行于一验证步骤之前,且每一预充电步骤以6微秒的预充电期间进行。在实施例2中,在编程操作期间,编程方法包含三个预充电步骤(n=3),三个预充电步骤进行于一验证步骤之前,且每一预充电步骤以4微秒的预充电期间进行。在实施例3中,在编程操作期间,编程方法包含六个预充电步骤(n=6),六个预充电步骤进行于一验证步骤之前,且每一预充电步骤以2微秒的预充电期间进行。如图4所示,相较于比较例,实施例1至实施例3的编程干扰抑制较佳。具体而言,实施例3的编程干扰抑制优于实施例2的编程干扰抑制,实施例2的编程干扰抑制优于实施例1的编程干扰抑制。

[0058]

图5绘示以比较例和实施例1至实施例3的编程方法编程的存储单元的测试结果。如图5所示,比较例和实施例1至实施例3的编程能力(program capabilities)是相似的。也就是说,本公开提供的编程方法可提升编程干扰的抑制效果,且仍维持编程能力。

[0059]

请同时参照图1与图6。图6绘示根据另一实施例的用于存储装置的编程方法。当图1所示的存储装置处于编程操作期间时,多个存储单元mc的一个被选择以进行编程,且其他存储单元mc可被理解为未选择存储单元。例如,存储单元mc_241被选择且可被理解为选择存储单元,其他存储单元(即存储单元mc_01,mc_11

…

mc_231,mc_251

…

mc_461,mc_471和mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)可被理解为未选择存储单元,包含选择存储单元(mc_241)的第一存储器串行101可被理解为选择存储器串行,且包含未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的第二存储器串行102可被理解为未选择存储器串行。

[0060]

编程方法可包含在编程操作期间,施加一系列渐增的编程电压,以编程选择存储单元(mc_241)。在一系列的编程电压中,编程电压可能(但不限于)逐步增加;也就是编程电压可能以固定的差值增加。编程方法可包含多个编程阶段。每一编程阶段对应于一系列编程电压中的一编程电压。每一编程阶段包含对选择存储单元(mc_241)进行验证步骤、以及早于验证步骤的至少一个编程步骤,编程步骤包含对用以驱动选择存储单元(mc_241)的字

线wl24施加对应的编程电压。为了便于说明,图6仅示例性地显示四个编程阶段。

[0061]

在图6中,编程方法包含依序进行的编程阶段s1,s2,s3,s4。每一编程阶段s1,s2,s3,s4分别对应于每一编程电压v

pgm

1,v

pgm

2,v

pgm

3,v

pgm

4。在此实施例中,编程电压可以x伏特的差值渐增(x大于0),换言之,编程电压v

pgm

2可理解为v

pgm

1+x,编程电压v

pgm

3可理解为v

pgm

1+2x,编程电压v

pgm

4可理解为v

pgm

1+3x。

[0062]

编程阶段s1包含进行编程步骤601、以及在编程步骤601之后进行验证步骤603。编程阶段s1可还包含处理步骤602,进行于编程步骤601与验证步骤603之间。编程步骤601可包含对用以驱动选择存储单元(mc_241)的字线wl24施加编程电压v

pgm

1,以编程选择存储单元(mc_241)。对选择存储单元(mc_241)进行验证步骤603,以验证选择存储单元(mc_241)是否被适当地编程。

[0063]

若编程阶段s1的验证步骤603失败(代表选择存储单元没有被成功编程),编程阶段s2会接着进行,且编程阶段s2包含增加的编程电压v

pgm

2与一预充电步骤。编程阶段s2可包含依序进行预充电步骤604、处理步骤605、编程步骤606、处理步骤607与验证步骤608。预充电步骤604可包含对用以驱动第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的位线bl_2施加预充电电压v

pre

,以关闭第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472),且抑制第二存储器串行102的未选择存储单元(mc_02,mc_12

…

mc_232,mc_242,mc_252

…

mc_462,mc_472)的编程。编程步骤606可包含对字线wl24施加编程电压v

pgm

2,以编程选择存储单元(mc_241)。对选择存储单元(mc_241)进行验证步骤608,以验证选择存储单元(mc_241)是否被适当地编程。

[0064]

若编程阶段s2的验证步骤608失败(代表选择存储单元没有被成功编程),编程阶段s3会接着进行,且编程阶段s3包含,相较于编程阶段s2,更增加的编程电压v

pgm

3与更多预充电步骤。编程阶段s3可包含依序进行预充电步骤609、处理步骤610、编程步骤611、处理步骤612、预充电步骤613、处理步骤614、编程步骤615、处理步骤616与验证步骤617。预充电步骤609可包含对位线bl_2施加预充电电压v

pre

。编程步骤611可包含对字线wl24施加编程电压v

pgm

3。预充电步骤615可相似于预充电步骤609。编程步骤615可相似于编程步骤611。对选择存储单元(mc_241)进行验证步骤617,以验证选择存储单元(mc_241)是否被适当地编程。编程阶段s3可能相似于图2a与图2b图所示的操作方式。

[0065]

若编程阶段s3的验证步骤617失败(代表选择存储单元没有被成功编程),编程阶段s4会接着进行,且编程阶段s4包含,相较于编程阶段s3,更增加的编程电压v

pgm

4与更多预充电步骤。编程阶段s4可包含依序进行预充电步骤618、处理步骤619、编程步骤620、处理步骤621、预充电步骤622、处理步骤623、编程步骤624、处理步骤625、预充电步骤626、处理步骤627、编程步骤628、处理步骤629与验证步骤630。每一预充电步骤618,622,626可包含对位线bl_2施加预充电电压v

pre

。每一编程步骤620,624,628可包含对字线wl24施加编程电压v

pgm

4。对选择存储单元(mc_241)进行验证步骤630,以验证选择存储单元(mc_241)是否被适当地编程。编程阶段s4可能相似于图3所示的操作方式。

[0066]

在图6中,编程方法包含四个编程阶段,然而,编程方法可能包含多于四个编程阶段或少于四个编程阶段。在一实施例中,编程方法可包含在编程阶段s4之后进行更多编程阶段,且使用更增加的编程电压。编程电压v

pgm

可以上述方式递增地增加,直到选择存储单

元(mc_241)被适当地编程,或者直到选择存储单元(mc_241)达到预定的阈值电压(threshold voltage)。在一实施例中,在一编程阶段中,预充电步骤之间可不包含任何验证步骤,和/或编程步骤之间可不包含任何验证步骤。在另一实施例中,一个编程阶段包含仅一个验证步骤,该验证步骤在所有该编程阶段的编程步骤完成后才进行。

[0067]

在图6中,预充电步骤604可包含在第一预充电期间对位线bl_2施加预充电电压v

pre

,每一预充电步骤609,613可包含在第二预充电期间对位线bl_2施加预充电电压v

pre

,每一预充电步骤618,622,626可包含在第三预充电期间对位线bl_2施加预充电电压v

pre

。第一预充电期间可大于第二预充电期间,第二预充电期间可大于第三预充电期间。在一实施例中,第一预充电期间可为12微秒,第二预充电期间可为6微秒,第三预充电期间可为4微秒。在一实施例中,在一编程阶段,预充电期间取决于预充电步骤的数量。具体而言,预充电期间随着预充电步骤的数量增加而减少。在一实施例中,用于不同编程阶段的预充电电压v

pre

可为定值。

[0068]

在图6中,编程步骤606可包含在第一编程期间对字线wl24施加编程电压v

pgm

2,每一编程步骤611,615可包含在第二编程期间对字线wl24施加编程电压v

pgm

3,每一编程步骤620,624,628可包含在第三编程期间对字线wl24施加编程电压v

pgm

4。第一编程期间可大于第二编程期间,第二编程期间可大于第三编程期间。在一实施例中,第一编程期间可为12微秒,第二编程期间可为6微秒,第三编程期间可为4微秒。在一实施例中,在一编程阶段,编程期间取决于编程步骤的数量。具体而言,编程期间随着编程步骤的数量增加而减少。

[0069]

当编程电压低的时候,编程干扰可能是轻微的。因此,当编程电压低的时候,预充电步骤可能是非必要的。例如,在图6中,编程阶段s1不包含预充电步骤,由于编程电压v

pgm

1是低的。

[0070]

在一实施例中,每一编程阶段中编程步骤的数量可随着编程电压v

pgm

增加而增加,且每一编程阶段中编程期间可随着编程电压v

pgm

增加而减少。在一实施例中,每一编程阶段中预充电步骤的数量可随着编程电压v

pgm

增加而增加,且每一编程阶段中预充电期间可随着编程电压v

pgm

增加而减少。预充电步骤的数量可等于编程步骤的数量。

[0071]

图7绘示根据一实施例的用于存储装置的编程方法。图7所示的编程方法和图6所示的编程方法的差异在于,图7所示的编程方法可在编程阶段s1,s2,s3,s4之间包含更多编程阶段。例如,图7所示的编程方法可包含编程阶段s11介于编程阶段s1与编程阶段s2之间。除了用于编程阶段s1_1的编程电压v

pgm

1_1和用于编程阶段s1的编程电压v

pgm

1不同之外,编程阶段s1_1相似于编程阶段s1。编程电压v

pgm

1_1大于用于编程阶段s1的编程电压v

pgm

1,且小于用于编程阶段s2的编程电压v

pgm

2。编程方法可包含编程阶段s2_1介于编程阶段s2与编程阶段s3之间。除了用于编程阶段s2_1的编程电压v

pgm

2_1和用于编程阶段s2的编程电压v

pgm

2不同之外,编程阶段s2_1相似于编程阶段s2。编程电压v

pgm

2_1大于用于编程阶段s2的编程电压v

pgm

2,且小于用于编程阶段s3的编程电压v

pgm

3。编程方法可包含编程阶段s3_1介于编程阶段s3与编程阶段s4之间。除了用于编程阶段s3_1的编程电压v

pgm

3_1和用于编程阶段s3的编程电压v

pgm

3不同之外,编程阶段s3_1相似于编程阶段s3。编程电压v

pgm

3_1大于用于编程阶段s3的编程电压v

pgm

3,且小于用于编程阶段s4的编程电压v

pgm

4。编程方法可包含编程阶段s4_1在编程阶段s4之后。除了用于编程阶段s4_1的编程电压v

pgm

4_1和用于编程阶段s4的编程电压v

pgm

4不同之外,编程阶段s4_1相似于编程阶段s4。编程电压v

pgm

4_1大于用

于编程阶段s4的编程电压v

pgm

4。

[0072]

在一实施例中,编程方法可在编程阶段s1与编程阶段s2之间、和/或编程阶段s2与编程阶段s3之间、和/或编程阶段s3与编程阶段s4之间、和/或编程阶段s4之后包含多于一个编程阶段。用于多个编程阶段的编程电压v

pgm

随着每个编程阶段而增加。

[0073]

在一实施例中,每个编程阶段中的预充电步骤的数量可对应于编程电压范围,也就是说,当用于一编程阶段的编程电压v

pgm

落在编程电压范围内时,该编程阶段中的预充电步骤的数量可为定值。换言之,当用于一编程阶段的编程电压v

pgm

增加至特定电压值时,该编程阶段中的预充电步骤的数量才会增加。例如,如图7所示,在达到编程电压v

pgm

2之前,编程阶段s1,s1_1

…

中的每一个的预充电步骤的数量维持于0;当达到编程电压v

pgm

2,编程阶段s2中的预充电步骤的数量增加为1。例如,如图7所示,在达到编程电压v

pgm

3之前,编程阶段s2,s2_1

…

中的每一个的预充电步骤的数量维持于1;当达到编程电压v

pgm

3,编程阶段s3中的预充电步骤的数量增加为2。

[0074]

在此实施例中,每个编程阶段中的编程步骤的数量可对应于编程电压范围,也就是说,当用于一编程阶段的编程电压v

pgm

落在编程电压范围内时,该编程阶段中的编程步骤的数量可为定值。换言之,当用于一编程阶段的编程电压v

pgm

增加至特定电压值时,该编程阶段中的编程步骤的数量才会增加。例如,如图7所示,在达到编程电压v

pgm

3之前,编程阶段s2,s21

…

中的每一个的编程步骤的数量维持于1;当达到编程电压v

pgm

3,编程阶段s3中的编程步骤的数量增加为2。预充电步骤的数量可等于编程步骤的数量。

[0075]

在一比较例中,编程方法包含仅一个预充电步骤与仅一个编程步骤,由于未选择存储单元之间的电位差可能诱发带间泄漏(band to band leakage),使得发生于未选择存储器串行中的未选择存储单元的通道中的局部自升压现象(local self-boosting)可能会在编程步骤崩溃。此外,随着编程步骤的编程期间增加,局部自升压现象的崩溃会更加严重。局部自升压现象的崩溃可能降低未选择存储单元的控制栅极与通道之间的电位差(control gate-to-channel potential differences),从而导致严重的编程干扰。相较于此,本公开提供的编程方法包含多于一个预充电步骤,在一编程操作中进行多于一个预充电步骤有益于建立稳定的局部自升压现象,且可降低或避免局部自升压现象的崩溃,从而可降低或抑制编程干扰。而且,相较于包含仅一个预充电步骤与仅一个编程步骤的编程方法比较例,本公开的编程方法的预充电步骤以短的预充电期间来进行,且本公开的编程方法的编程步骤以短的编程期间来进行。在一编程操作中,数量较多的预充电步骤、以及以短的预充电期间来进行每一预充电步骤,有益于有效率地建立局部自升压现象,且使未选择存储单元处于强的关闭状态。短的编程期间亦有益于建立局部自升压现象且可降低或抑制编程干扰。因此,通过本公开的编程方法,可提升存储装置的编程干扰抑制效果,且可增加编程窗口(program window),同时维持存储装置的编程能力。

[0076]

根据本公开的概念亦可延伸应用至其它变化情况。

[0077]

存储器串行可为垂直通道结构,或者可使用单一栅极垂直通道结构、或垂直栅极结构等等。存储单元可为浮栅存储单元或氮化物俘获型存储单元等等。存储单元可为单阶存储单元、多阶存储单元、或三阶存储单元等等。

[0078]

综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中具有公知常识的技术人员,在不脱离本发明的精神和范围内,当可作各种的

改动与润饰。因此,本发明的保护范围当以的权利要求所界定的范围为准。

[0079]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1