用于多系统日志存取管理的方法、集成电路及可读介质与流程

1.本发明系有关于一集成电路(integrated circuit,ic)上的跨系统(cross-system)管理,尤指一种用来进行多系统(multi-system)日志(log)存取管理的方法、相关的系统单芯片(system on chip,可简称soc)集成电路(integrated circuit,可简称ic)以及非瞬时计算机可读介质(non-transitory computer-readable medium)。

背景技术:

2.一soc ic可包含多个处理器以供实现不同的功能(例如系统控制、声音相关功能等)。在该soc ic的各种阶段(phase)中,记录该多个处理器的各自的日志可能是需要的。例如,在该soc ic的设计时间、实验室试运行(pilot run)阶段及量产(production)试运行阶段中,可能需要大量的日志,以供进行系统效能分析以及侦错(debug)。在该soc ic的量产阶段中,可能也需要日志,以供找出系统当机(crash)的原因。由于该soc ic可具备各种不同的功能,该soc ic中的这些处理器可分别运行不同的系统。然而,可能发生某些问题。例如,该soc ic可能仅仅保留这些处理器中的单处理器的日志或仅仅保留这些系统中的单一系统的日志,且因此缺乏通用的架构,以供获取跨系统及多处理器的日志。又例如,这些处理器可能分别输出日志至同一个控制面板(console),其中同时操作同一个控制台可能需要加上锁定机制,这可造成这些处理器互相等待,且因此拖慢了这些处理器的速度。再例如,在该soc ic没有接到控制台、或者该soc ic接到控制面板但一控制面板端主机故障的情况下,无法对该soc ic进行相关分析。因此,需要一种新颖的方法及相关架构,以在没有副作用或较不可能带来副作用的状况下实现具有可靠的日志处理机制的soc ic。

技术实现要素:

3.本发明的一目的在于提供一种用来进行多系统(multi-system)日志(log)存取管理的方法、相关的系统单芯片(system on chip,soc)集成电路以及非瞬时计算机可读介质,以解决上述问题。

4.本发明的另一目的在于提供一种用来进行多系统日志存取管理的方法、相关的系统单芯片集成电路以及非瞬时计算机可读介质,以确保多个系统的日志信息的记录的完整性(completeness)、正确性及可用性(availability)。

5.本发明的至少一实施例提供一种用来进行多系统日志存取管理的方法,其中该方法是可应用于(applicable to)一系统单芯片集成电路。该方法可包含:利用该系统单芯片集成电路中的至少一处理器运行多个系统以控制该系统单芯片集成电路的操作,其中该至少一处理器包含多个局部电路,且该多个局部电路分别运行该多个系统;利用该多个局部电路中的一第一局部电路执行至少一第一日志管理程序,以将该系统单芯片集成电路中的至少一存储器配置成分别对应于该多个局部电路的多个环缓冲器、于该多个环缓冲器中的一第一环缓冲器中记录运行于该第一局部电路的一第一系统的一组第一日志,且将该多个环缓冲器所分别储存的多组日志写入一文件系统以成为至少一日志文件以供存取,其中该

多个系统包含该第一系统,而该多组日志包含该组第一日志;以及利用该多个局部电路中的至少一第二局部电路执行至少一第二日志管理程序,以于该多个环缓冲器中的至少一第二环缓冲器中记录运行于该至少一第二局部电路的至少一第二系统的至少一组第二日志,其中该多个系统包含该至少一第二系统,而该多组日志包含该至少一组第二日志。

6.本发明的至少一实施例提供一种系统单芯片集成电路,其中该系统单芯片集成电路是可应用于多系统日志存取管理。该系统单芯片集成电路可包含:至少一处理器,该至少一处理器包含多个局部电路;以及至少一存储器,耦接至该至少一处理器。该多个局部电路可用来分别运行多个系统以控制该系统单芯片集成电路的操作,而该至少一存储器可用来为该系统单芯片集成电路储存信息。例如:该多个局部电路中的一第一局部电路执行至少一第一日志管理程序,以将该至少一存储器配置成分别对应于该多个局部电路的多个环缓冲器、于该多个环缓冲器中的一第一环缓冲器中记录运行于该第一局部电路的一第一系统的一组第一日志、且将该多个环缓冲器所分别储存的多组日志写入一文件系统以成为至少一日志文件,以供进一步使用,其中该多个系统包含该第一系统,而该多组日志包含该组第一日志;以及该多个局部电路中的至少一第二局部电路执行至少一第二日志管理程序,以于该多个环缓冲器中的至少一第二环缓冲器中记录运行于该至少一第二局部电路的至少一第二系统的至少一组第二日志,其中该多个系统包含该至少一第二系统,而该多组日志包含该至少一组第二日志。

7.本发明的至少一实施例提供一种非瞬时计算机可读介质,其储存有程序代码使得一系统单芯片集成电路于执行所述程序代码时进行一多系统日志存取管理程序,该系统单芯片集成电路中的至少一处理器运行多个系统以控制该系统单芯片集成电路的操作,该至少一处理器包含多个局部电路,该多个局部电路分别运行该多个系统,该多系统日志存取管理程序包含:利用该多个局部电路中的一第一局部电路执行至少一第一日志管理程序,以将该系统单芯片集成电路中的至少一存储器配置成分别对应于该多个局部电路的多个环缓冲器、于该多个环缓冲器中的一第一环缓冲器中记录运行于该第一局部电路的一第一系统的一组第一日志,且将该多个环缓冲器所分别储存的多组日志写入一文件系统以成为至少一日志文件以供存取,其中该多个系统包含该第一系统,而该多组日志包含该组第一日志;以及利用该多个局部电路中的至少一第二局部电路执行至少一第二日志管理程序,以于该多个环缓冲器中的至少一第二环缓冲器中记录运行于该至少一第二局部电路的至少一第二系统的至少一组第二日志,其中该多个系统包含该至少一第二系统,而该多组日志包含该至少一组第二日志。

8.依据某些实施例,在该至少一处理器代表多个处理器/处理器核心的情况下,该多个局部电路可代表该多个处理器/处理器核心。例如,该多个处理器/处理器核心可通过多个中央处理单元(central processing unit,可简称cpu)或多个cpu核心等方式来实施。

9.本发明的好处之一是,通过仔细设计的日志处理机制,本发明能使多系统架构(architecture)诸如多核异构(multi-core heterogeneous)cpu架构具备跨系统日志处理能力,尤其能提升整体日志处理效能,且能避免相关技术的问题诸如频繁操作控制台、加上锁定机制所致的等待而造成系统效能降低等。

附图说明

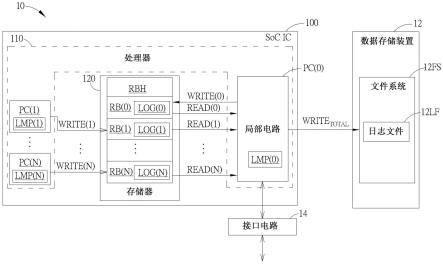

10.图1为依据本发明一实施例的一种系统单芯片(system on chip,可简称soc)集成电路(integrated circuit,可简称ic)的示意图。

11.图2依据本发明一实施例示出图1所示的系统单芯片集成电路的实施细节。

12.图3依据本发明另一实施例示出图1所示的系统单芯片集成电路的实施细节。

13.图4依据本发明一实施例示出一种用来进行多系统(multi-system)日志(log)存取管理的方法的一局部(partial)日志处理控制方案。

14.图5依据本发明一实施例示出该方法的一全局(global)日志处理控制方案。

15.图6依据本发明一实施例示出该方法所涉及的一种非瞬时计算机可读介质。

具体实施方式

16.图1为依据本发明一实施例的一种系统单芯片(system on chip,简称soc)集成电路(integrated circuit,简称ic)100的示意图,其中soc ic 100可位于一电子装置10中,尤其,可被安装(mount)于电子装置10的一主电路板(例如印刷电路板)上,但本发明不限于此。如图1所示,除了soc ic 100,电子装置10可包含一数据储存装置12及一接口电路14,而数据储存装置12可包含一文件系统12fs。另外,soc ic 100可包含至少一处理器(例如一或多个处理器),统称为处理器110,且可还包含耦接至处理器110的至少一存储器(例如一或多个存储器),统称为存储器120,其中处理器110可包含多个局部电路{pc}诸如(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n),以供分别运行多个系统诸如系统#0、#1、

…

及#n,其中符号{}可代表集合。这些局部电路{pc}诸如该(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n)可独立地操作且可分别视为多个局部处理电路诸如(n+1)个局部处理电路,尤其,可为soc ic 100分别执行系统#0、#1、

…

及#n。为了便于理解,系统#0、#1、

…

及#n可分别代表多个操作系统(operating system,os)。

17.在运行于处理器110上的至少一程序模块(例如一或多个程序模块)的控制下,处理器110可将存储器120(例如其多个储存区)配置成多个环缓冲器(ring buffer){rb}诸如(n+1)个环缓冲器rb(0)、rb(1)、

…

及rb(n)以及一环缓冲器头区rbh以及进行多个日志存取操作。例如,这些日志存取操作可包含:

18.(1)局部电路pc(0)、pc(1)、

…

及pc(n)分别对环缓冲器rb(0)、rb(1)、

…

及rb(n)所进行的写入操作写入write(0)、write(1)、

…

及write(n),其中这些写入操作可为日志写入操作;

19.(2)局部电路pc(0)分别对环缓冲器rb(0)、rb(1)、

…

及rb(n)所进行的读取操作read(0)、read(1)、

…

及read(n),其中这些读取操作可为日志读取操作;以及

20.(3)局部电路pc(0)对数据储存装置12中的文件系统12fs的写入操作write

total

,其中这个写入操作也可为日志写入操作,且因为被写入文件系统12fs而可为文件写入操作,诸如日志文件写入操作;但本发明不限于此。

21.基于图1所示架构,soc ic 100可进行多系统日志存取管理。该多个局部电路{pc}诸如该(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n)可分别运行系统#0、#1、

…

及#n以控制soc ic 100的操作,而上述至少一存储器诸如存储器120可用来为soc ic 100储存信息,其中系统#0、#1、

…

及#n中的至少两个系统典型地(typically)彼此不同,尤其,分别属于不同类型

的系统。例如,系统#0、#1、

…

及#n可分别对应于电子装置10的多个功能诸如功能#0、#1、

…

及#n,其中功能#0可包含系统控制,而功能#1、

…

及#n可包含声音处理、视频处理、通信处理、定位处理等,但不以此为限。

22.该多个局部电路{pc}中的一第一局部电路,诸如局部电路pc(0),可被配置成主要(main)局部电路,以进行该多系统日志存取管理的整体控制。尤其,局部电路pc(0)可执行至少一第一日志管理程序诸如日志管理程序lmp(0),以进行下列操作:

23.(1)将存储器120配置成分别对应于该(n+1)个局部电路pc(0)、pc

24.(1)、

…

及pc(n)的该(n+1)个环缓冲器rb(0)、rb(1)、

…

及rb(n);

25.(2)于该(n+1)个环缓冲器rb(0)、rb(1)、

…

及rb(n)中的一第一环缓冲器诸如环缓冲器rb(0)中,记录运行于该第一局部电路上的一第一系统(其中系统#0、#1、

…

及#n包含该第一系统,例如系统#0)的一组第一日志,诸如运行于局部电路pc(0)的系统#0上的一组日志log(0);以及

26.(3)将该(n+1)个环缓冲器所分别储存的(n+1)组日志log(0)、log(1)、

…

及log(n)写入文件系统12fs以成为至少一日志文件12lf,以供进一步使用(例如由使用者/其它处理器根据至少一指令存取并显示于显示器上,令使用者/其它处理器可根据各日志的内容对该多个局部电路{pc}进行控制/优化/重设/除错

…

等程序),其中该(n+1)组日志log(0)、log(1)、

…

及log(n)包含该组第一日志诸如该组日志log(0)。

27.另外,该多个局部电路{pc}中的至少一第二局部电路,诸如局部电路pc(n)(例如:符号“n”可代表区间[1,n]中的任一正整数),可执行至少一第二日志管理程序诸如日志管理程序lmp(n),以于该(n+1)个环缓冲器rb(0)、rb(1)、

…

及rb(n)中的至少一第二环缓冲器诸如环缓冲器rb(n)中,记录运行于该至少一第二局部电路(例如局部电路pc(n))的至少一第二系统(其中该至少一第二系统包含于系统#0、#1、

…

及#n中,例如系统#n)的至少一组第二日志(例如一组日志log(n)),而该(n+1)组日志log(0)、log(1)、

…

及log(n)包含该至少一组第二日志诸如该组日志log(n)。举例来说,n个局部电路pc(1)、

…

及pc(n)可分别执行n个日志管理程序lmp(1)、

…

及lmp(n),以分别于n个环缓冲器rb(1)、

…

及rb(n)中记录运行于n个局部电路pc(1)、

…

及pc(n)的n个系统#1、

…

及#n的n组日志log(1)、

…

及log(n)。

[0028]

为了便于理解,该多个局部电路{pc}诸如该(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n)可通过处理器/处理器核心诸如中央处理单元(central processing unit,下简称cpu)/cpu核心等方式来实施。此情况下,上述至少一处理器诸如处理器110可包含多个处理器/处理器核心诸如多个cpu/cpu核心。

[0029]

图2依据本发明一实施例示出图1所示的soc ic 100的实施细节。于本实施例中,图1所示的该(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n)可分别被实施成(n+1)个cpu诸如cpu(0)、cpu(1)、

…

及cpu(n),其中上列cpu中的某一个cpu诸如cpu(0)可为这些cpu中的主要cpu。为了简明起见,于本实施例中类似的内容在此不重复赘述。

[0030]

图3依据本发明另一实施例示出图1所示的soc ic 100的实施细节。于本实施例中,图1所示的该(n+1)个局部电路pc(0)、pc(1)、

…

及pc(n)可分别被实施成(n+1)个cpu核心诸如core(0)、core(1)、

…

及core(n),其中上列cpu核心中的某一个cpu核心诸如core(0)可为这些cpu核心中的主要cpu核心。为了简明起见,于本实施例中类似的内容在此不重复赘述。

[0031]

基于图1所示架构,电子装置10(例如其内的soc ic 100、数据储存装置12等)可依据一种用来进行该多系统日志存取管理的方法来操作,其中该方法是可应用于(applicable to)电子装置10,尤其,其内的soc ic 100、数据储存装置12等。该方法可包含:利用处理器110运行系统#0、

…

及#n(例如:“n”代表正整数)以控制soc ic 100的操作;利用该第一局部电路诸如局部电路pc(0)(可实施为图2的cpu cpu(0)或图3的cpu核心core(0))执行该至少一第一日志管理程序诸如日志管理程序lmp(0),以将存储器120配置成分别对应于该(n+1)个局部电路pc(0)、

…

及pc(n)(可实施为图2的cpu cpu(0)、

…

及cpu(n)或图3的cpu核心core(0)、

…

及core(n))的该(n+1)个环缓冲器rb(0)、

…

及rb(n),且于环缓冲器rb(0)中记录运行于局部电路pc(0)的系统#0的该组日志log(0),并且将该(n+1)个环缓冲器所分别储存的该(n+1)组日志log(0)、

…

及log(n)写入文件系统12fs以成为日志文件12lf,以供进一步使用;以及利用该至少一第二局部电路诸如一或多个局部电路{pc(n)}(可实施为图2的cpu{cpu(n)}或图3的cpu核心{core(n)},后面实施例依此类推)(例如:“n”可代表区间[1,n]中的任一正整数)执行该至少一第二日志管理程序诸如一或多个日志管理程序{lmp(n)},以于该至少一第二环缓冲器诸如一或多个环缓冲器{rb(n)}中记录运行于该至少一第二局部电路(例如该一或多个局部电路{pc(n)})的该至少一第二系统(例如:系统#1,如果n=1;又例如:系统#1至系统#n,如果n》1)的该至少一组第二日志(例如:一组日志log(1),如果n=1;又例如:该n组日志log(1)、

…

及log(n),如果n》1)。

[0032]

另外,电子装置10(例如其内的soc ic 100、数据储存装置12等)可依据该方法而被配置成具备多个日志处理管线(pipeline)。在运行于处理器110上的该至少一程序模块(例如:该至少一第一日志管理程序以及该至少一第二日志管理程序,诸如日志管理程序lmp(0)、

…

及lmp(n))的控制下,处理器110可将soc ic 100的架构(例如:该(n+1)个局部电路pc(0)、

…

及pc(n),该(n+1)个环缓冲器rb(0)、

…

及rb(n),以及内部连接结构(structure)诸如数据处理路径)配置成多管线(multi-pipeline)架构。例如,该方法中的相关配置操作可包含:

[0033]

(1)利用该至少一第一日志管理程序诸如日志管理程序lmp(0),将从该第一局部电路连接至该第一环缓冲器的一第一数据处理路径,诸如从局部电路pc(0)连接至环缓冲器rb(0)的一数据处理路径(例如:对应于写入操作write(0)的数据处理路径),配置成一第一日志写入管线,诸如对应于该组日志log(0)的一日志写入管线;

[0034]

(2)利用该至少一第二日志管理程序诸如该一或多个日志管理程序{lmp(n)},将从该至少一第二局部电路连接至该至少一第二环缓冲器的至少一第二数据处理路径,诸如从该一或多个局部电路{pc(n)}分别连接至该一或多个环缓冲器{rb(n)}的一或多个数据处理路径(例如:对应于一或多个写入操作{write(n)}的一或多个数据处理路径),配置成至少一第二日志写入管线,诸如对应于一或多组日志(例如:一组日志log(1),如果n=1;又例如:该n组日志log(1)、

…

及log(n),如果n》1)的一或多个日志写入管线;

[0035]

(3)利用该至少一第一日志管理程序诸如日志管理程序lmp(0),将从该多个环缓冲器{rb}连接至该第一局部电路的多个其它数据处理路径,诸如从该(n+1)个环缓冲器rb(0)、

…

及rb(n)分别连接至局部电路pc(0)的(n+1)个数据处理路径(例如:对应于(n+1)个读取操作read(0)、

…

及read(n)的(n+1)个数据处理路径),配置成多个日志读取管线,诸如分别对应于该(n+1)组日志log(0)、

…

及log(n)的(n+1)个日志读取管线;以及

[0036]

(4)利用该至少一第一日志管理程序诸如日志管理程序lmp(0),将从该第一局部电路诸如局部电路pc(0)朝向(toward)文件系统12fs的一后续的数据处理路径,连同从该后续的数据处理路径延伸至文件系统12fs的一延伸的数据处理路径,配置成一日志导出管线,其中从局部电路pc(0)至文件系统12fs的总(total)输出处理路径可包含该后续的数据处理路径以及该延伸的数据处理路径,且可于其上标示写入操作write

total

以便于理解;

[0037]

其中,基于该多个局部电路{pc}与该多个环缓冲器{rb}之间的管线处理,该(n+1)组日志log(0)、

…

及log(n)缓冲于该多个环缓冲器{rb}的数据量可随着时间动态地改变。

[0038]

依据某些实施例,电子装置10(例如其内的soc ic 100、数据储存装置12等)可依据该方法来记录针对该(n+1)组日志log(0)、

…

及log(n)的整体管理信息,以于日志文件12lf中储存该(n+1)组日志log(0)、

…

及log(n)连同其整体管理信息,其中针对该(n+1)组日志log(0)、

…

及log(n)中的任一组日志(例如每一组日志)中的任一日志(例如每一日志)的整体管理信息可包含一序号(serial number)或一时间戳(timestamp)等。举例来说,该组第一日志诸如该组日志log(0)可包含这组日志当中的各日志的序号、这组日志当中的各日志的时间戳以及这组日志当中的各日志的日志内容,且该至少一组第二日志(例如:一组日志log(1),如果n=1;又例如:该n组日志log(1)、

…

及log(n),如果n》1)中的任一组第二日志可包含该任一组第二日志当中的各日志的序号、该任一组第二日志当中的各日志的时间戳以及该任一组第二日志当中的各日志的日志内容。另外,该(n+1)组日志log(0)、

…

及log(n)中的所有的日志的各自的时间戳是依据一相同的时钟(或称频率)来产生,以指出该(n+1)组日志log(0)、

…

及log(n)之间的相对时序,其中这个时钟可代表位于电子装置10中、由该(n+1)个局部电路pc(0)、

…

及pc(n)(例如分别运行于其上的系统#1、

…

及#n)所共享的时钟。例如,该时钟可设置于soc ic 100以内。又例如,该时钟可设置于soc ic 100以外。

[0039]

图4依据本发明一实施例示出该方法的一局部(partial)日志处理控制方案。为了便于理解,符号「n0」可代表区间[0,n]中的非负整数。图1的实施例所述的该(n+1)个局部电路pc(0)、

…

及pc(n)中的任一局部电路pc(n0),诸如图2的实施例所述的cpu cpu(n0)或图3的实施例所述的cpu核心core(n0),可在日志管理程序lmp(n0)的控制下依据该局部日志处理控制方案来操作,以于环缓冲器rb(n0)中写入一组日志log(n0)的一日志,其中该日志可视为一日志条目(entry)。

[0040]

于步骤s10中,局部电路pc(n0)可开始写入对应的缓冲器诸如环缓冲器rb(n0),尤其,于环缓冲器rb(n0)(例如其所缓冲的该组日志log(n0))中写入这个日志的日志内容(例如这个日志所代表的事件对应的事件信息)。

[0041]

于步骤s11中,局部电路pc(n0)可检查环缓冲器rb(n0)是否为满的(图中标示“环缓冲器是否已满”以求简明)。如果检查结果为是,结束局部日志处理控制方案的工作流程,例如可进入一错误处置程序来处理此情况;如果否,进入步骤s12。

[0042]

于步骤s12中,依据上述时钟的目前时间,局部电路pc(n0)可于环缓冲器rb(n0)(例如其所缓冲的该组日志log(n0))中加入这个日志的一时间戳,其中该时间戳可指出该目前时间。

[0043]

于步骤s13中,局部电路pc(n0)可于环缓冲器rb(n0)(例如其所缓冲的该组日志log(n0))中加入这个日志的一序号。例如,该组日志log(n0)的一系列序号可代表该组日志

log(n0)的所有日志的顺序,而该系列序号中的这个序号可指出这个日志相对于其余日志的相对顺序。

[0044]

于步骤s14中,局部电路pc(n0)可计算这个日志的日志内容的校验和(checksum),尤其,于环缓冲器rb(n0)(例如其所缓冲的该组日志log(n0))中写入该校验和以作为这个日志的完整性检查(integrity check)信息。

[0045]

于步骤s15中,局部电路pc(n0)可进行针对存储器障碍(memory barrier)的控制,例如发出一数据同步障碍(data synchronization barrier,简称dsb)指令。

[0046]

于步骤s16中,局部电路pc(n0)可更新环缓冲器rb(n0)的一输入指标器,其中该输入指标器可指出环缓冲器rb(n0)的一最新输入位置(例如目前写入的位置)。

[0047]

为了更好地理解,该方法可用图4所示的工作流程来说明,但本发明不限于此。依据某些实施例,一个或多个步骤可于图4所示的工作流程中增加、删除或修改。

[0048]

图5依据本发明一实施例示出该方法的一全局(global)日志处理控制方案。局部电路pc(0)(例如图2的cpu cpu(0)或图3的cpu核心core(0))可在日志管理程序lmp(0)的控制下依据该全局日志处理控制方案来操作,以从环缓冲器{rb(n0)}读取该组日志log(n0)当中的一或多个日志。

[0049]

于步骤s20中,局部电路pc(0)可开始读取缓冲器,例如开始执行对应于该全局日志处理控制方案的一主要控制程序。随后,进入步骤s21。

[0050]

于步骤s21中,局部电路pc(0)可进行存储器分配(memory allocation)以取得记忆空间以供一全局环缓冲器global_ring_buffer使用(图中标示“malloc(global_ring_buffer)”以求简明)。随后,进入步骤s22。

[0051]

于步骤s22中,局部电路pc(0)可初始化(initialize)全局环缓冲器global_ring_buffer(图中标示“init global_ring_buffer”以求简明),其中全局环缓冲器global_ring_buffer可包含环缓冲器头区rbh以及该(n+1)个环缓冲器rb(0)、

…

及rb(n)。例如,局部电路pc(0)可于环缓冲器头区rbh中记录该(n+1)个环缓冲器rb(0)、

…

及rb(n)的各自的环缓冲器管理信息,以分别指出该(n+1)个环缓冲器rb(0)、

…

及rb(n)的各自的用户(例如局部电路pc(0)、

…

及pc(n))以及该(n+1)个环缓冲器rb(0)、

…

及rb(n)的各自的大小。随后,进入步骤s23。

[0052]

于步骤s23中,局部电路pc(0)可创建(create)主要工作(main task)以控制后续步骤中的操作。例如,日志管理程序lmp(0)可包含该主要控制程序以及该主要工作,但本发明不限于此。随后,进入步骤s24。

[0053]

于步骤s24中,局部电路pc(0)可尝试从一个局部电路pc(n0)诸如一个cpu(例如图2的cpu cpu(n))/cpu核心(例如图3的cpu核心core(n))的环缓冲器rb(n0)读取一日志(图中标示“从一cpu的环缓冲器读取日志”以求简明)。随后,进入步骤s25。

[0054]

于步骤s25中,局部电路pc(0)可检查环缓冲器rb(n0)是否为空的(图中标示“环缓冲器是否为空”以求简明)。如果是,进入步骤s26;如果否,进入步骤s28。

[0055]

于步骤s26中,局部电路pc(0)可等待一段时间,尤其,休眠一段时间。随后,进入步骤s27。

[0056]

于步骤s27中,局部电路pc(0)可选择下一个局部电路诸如下一个cpu/cpu核心(图中标示“选择下一个cpu”以求简明),以轮流选择全部的局部电路诸如全部的cpu/cpu核心,

进而对全部的局部电路进行检查。随后,回到步骤s24。

[0057]

于步骤s28中,依据这个日志的日志内容,局部电路pc(0)可计算这个日志的校验和。随后,进入步骤s29。

[0058]

于步骤s29中,局部电路pc(0)可检查是否步骤s28中计算的校验和等于这个日志中所记录的校验和(图中标示“校验和是否正确”以求简明)。如果是,进入步骤s30;如果否,进入步骤s24。

[0059]

于步骤s30中,局部电路pc(0)可储存这个日志到文件系统12fs(例如日志文件12lf)。随后,进入步骤s31。

[0060]

于步骤s31中,局部电路pc(n0)可进行针对存储器障碍的控制,例如发出该dsb指令。随后,进入步骤s32。

[0061]

于步骤s32中,局部电路pc(0)可更新环缓冲器rb(n0)的一输出指标器,其中该输出指标器可指出环缓冲器rb(n0)的一最新输出位置(例如目前读取的位置)。随后,回到步骤s24。

[0062]

为了更好地理解,该方法可用图5所示的工作流程来说明,但本发明不限于此。依据某些实施例,一个或多个步骤可于图5所示的工作流程中增加、删除或修改。

[0063]

图6依据本发明一实施例示出该方法所涉及的一种非瞬时计算机可读介质(non-transitory computer-readable medium)10m,其中非瞬时计算机可读介质10m储存有程序代码10p使得soc ic 100于执行上述程序代码10p时进行一多系统日志存取管理程序诸如该多系统日志存取管理(例如,上列实施例中所述的各种操作)。为了便于理解,程序代码10p可被示出为包含日志管理程序lmp(0)、

…

及lmp(n),但本发明不限于此。另外,程序代码10p可被加载至处理器110以成为运行于处理器110上的该至少一程序模块。非瞬时计算机可读介质10m可代表电子装置10的某一储存装置/组件(例如图1所示的数据储存装置12或其它储存装置/组件)。该储存装置/组件可通过硬式磁盘驱动器、固态硬盘、通用闪存储存(universal flash storage,ufs)装置、非挥发性存储器组件(例如电子可抹除可编程只读存储器(electrically-erasable programmable read-only memory,eeprom)及快闪(flash)存储器)等方式来实施,但本发明不限于此。为了简明起见,于本实施例中类似的内容在此不重复赘述。

[0064]

通过仔细设计的日志处理机制,本发明能使多系统架构诸如多核异构(multi-core heterogeneous)cpu架构具备跨系统日志处理能力,尤其能提升整体日志处理效能。例如,本发明的方法及系统单芯片集成电路能控制该多个局部电路中的所有局部电路(例如,该多个处理器/处理器核心中的所有处理器/处理器核心,诸如该多个cpu中的所有cpu、或该多个cpu核心中的所有cpu核心)将其各自的日志分别输出到该多个环缓冲器,而非直接输出到一控制台,且能利用该第一局部电路(例如,该多个处理器/处理器核心中的一主要处理器/处理器核心,诸如该多个cpu中的一主要cpu、或该多个cpu核心中的一主要cpu核心)将完整日志输出到该控制面板,且因此能避免相关技术的问题诸如频繁操作控制台、加上锁定机制所致的等待而造成系统效能降低。另外,本发明的方法及系统单芯片集成电路能随时取得完整的日志,尤其在文件系统中保存完整的日志,且因此能避免相关技术的问题诸如控制台尚未连接、或者控制台已连接但控制面板端主机故障而导致无法查看日志。此外,通过使用存储器障碍的控制程序,本发明可确保单一缓冲器只有一个消费者和一个

生产者的情况下,实现先进先出(fifo)的无锁并发存取(no-lock burst access),避免加锁带来的系统效能下降以及可能导致的死锁。由于引入全局的时间戳,本发明可通过相邻日志的时间戳之间的间隙(gap),提供更好的系统分析参考信息。本发明另可通过引入序号,提供判断是否遗失任何日志的参考信息。

[0065]

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

[0066]

【符号说明】

[0067]

10:电子装置

[0068]

12:数据储存装置

[0069]

12fs:文件系统

[0070]

12lf:日志文件

[0071]

14:接口电路

[0072]

100:系统单芯片(soc)集成电路(ic)

[0073]

110:处理器

[0074]

120:存储器

[0075]

lmp(0)~lmp(n):日志管理程序

[0076]

log(0)~log(n):日志

[0077]

pc(0)~pc(n):局部电路

[0078]

rb(0)~rb(n):环缓冲器

[0079]

rbh:环缓冲器头区

[0080]

write(0)~write(n),write

total

:写入操作

[0081]

read(0)~read(n):读取操作

[0082]

cpu(0)~cpu(n):中央处理单元(cpu)

[0083]

core(0)~core(n):中央处理单元(cpu)核心

[0084]

s10~s16,s20~s32:步骤

[0085]

10m:非瞬时计算机可读介质

[0086]

10p:程序代码。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1