远程更新FPGA的系统及方法与流程

远程更新fpga的系统及方法

技术领域:

1.本发明涉及fpga系统远程更新技术领域,具体的说是一种成本低、灵活准确的远程更新fpga的系统及方法。

背景技术:

2.现有基于cpu远程更新fpga的系统大都需要设置cpld实现,如专利文件cn110196726a,公开了一种基于cpu+cpld实现fpga程序远程升级加载的方法,其系统结构复杂,成本相对较高,不适合大规模推广应用。此外,如专利文献cn108664264a记载了一种基于cpu通过pcie设备拓展的gpio接口模拟jtag方式远程更新fpga的装置和方法,该技术方案需要配合pcie设备,也存在成本高的问题。

技术实现要素:

3.本发明针对现有技术中存在的缺点和不足,提出了一种结构合理、灵活可靠,多冗余的远程更新fpga的系统及方法。

4.本发明通过以下措施达到:

5.一种远程更新fpga的系统,其特征在于,设有cpu、fpga、开关矩阵以及flash存储器,其中所述开关矩阵内设有共用一个控制信号ctl的四个继电器,四个继电器分别为继电器a、继电器b、继电器c、继电器d;所述flash存储器包括至少一个可擦写flash存储器以及至少一个不可擦写flash存储器;所述cpu通过串口、can总线或网口从上位机获取fpga程序代码,并将获取的程序代码写入可擦写的flash中或通过gpio接口模拟jtag接口直接对fpga进行烧写,由cpu控制开关矩阵a和开关矩阵b(本专利仅描述设有两组flash的情况,若系统增加flash数量,开关矩阵数量也会相应的增加),开关矩阵a用于切换选择cpu或fpga的四路信号,所述四路信号分别为clk、cs、mosi、miso,开关矩阵b用于切换这四路信号是通往flash1或flash2,cpu使用gpio接口按照jtag时序模拟jtag接口,与fpga相连。

6.本发明还提出了一种利用上述远程更新fpga系统的方法,其特征在于,使用多种冗余的方式对fpga的程序进行加载,具体包括:一、直接使用cpu的gpio接口按照jtag时序模拟jtag接口对fpga进行程序加载;二、开关矩阵a切换到模式二,由cpu决定使用哪片flash将其提前烧写好的程序向fpga加载;三、由cpu通过开关矩阵a的模式一,及开关矩阵b的模式二向flash2中重新烧写程序,再将开关矩阵a调到模式二,由flash2向fpga加载程序,本专利仅描述了使用一片可擦写的flash的情况,也可增加可擦写flash的数量,有cpu控制多组开关矩阵向某个flash中烧写程序,并由改flash向fpga加载程序。

7.本发明中,当系统工作于第一种方式时,直接使用cpu的gpio接口模拟jtag时序对fpga进行程序加载,在cpu外扩的gpio接口中,选取四个接口,仿照jtag协议的四个接口:模式选择接口tms,时钟接口tck,数据输入接口tdi,数据输出接口tdo,分别配置其输入输出模式,再仿照jtag接口烧写fpga程序时的时序及协议,编写烧写程序,最终实现使用cpu读取由上位机传输的烧写文件,使用外扩gpio接口与fpga的jtag口连接,直接对fpga烧写程

序。

8.本发明当系统工作于第二种方式时,开关矩阵a切换到模式二,由cpu决定使用哪片flash将其提前烧写好的程序向fpga加载,选取一片不可擦除的flash作为主flash,另用不少于一片的可擦写flash作为副flash,若仅使用一片副flash,则仅需配有两个开关矩阵,其中开关矩阵a为选通flash与fpga之间通道或者flash与cpu之间通道的,开关矩阵b为选通fpga与不同flash之间通道的,开关矩阵b随着flash的片数增加而相应增加,用于选通不同flash;由cpu的ctl1信号控制开关矩阵a切换到模式二,即选通flash与fpga之间的通道,再由cpu的ctl2信号控制开关矩阵b切换到模式一或模式二,用于选择不同的flash片对fpga进行程序烧写。

9.本发明当系统工作于第三种方式时,由cpu通过开关矩阵a的模式一,选通flash与cpu之间的通道;开关矩阵b处于模式二,选通cpu和可擦写的副flash,若有多片副flash,则需要相应的增加矩阵模块数量,上位机通过相应串口向cpu提供所需的烧写文件,将烧写文件烧写入所选择的副flash中;副flash重新烧写完毕后,再由cpu控制开关矩阵a调到模式二,选通副flash片与fpga,并将fpga上电,fpga将从副flash2中读取烧写文件,完成程序加载。

10.本发明通过上述技术方案,可以使用多种冗余的方式对fpga的程序进行加载。

附图说明:

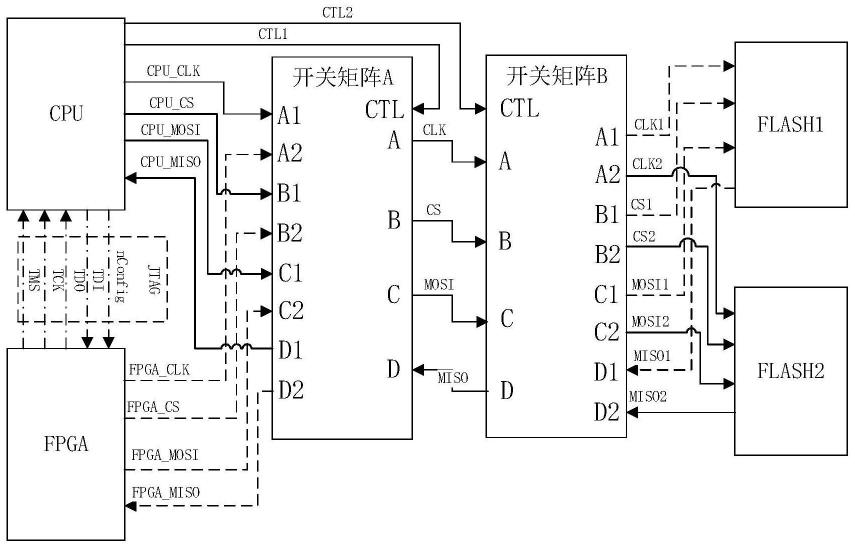

11.附图1是本发明的一种系统结构框图。

12.附图2是本发明中开关矩阵的结构图。

具体实施方式:

13.下面结合附图,对本发明做进一步的说明。

14.如附图1所示,本发明提出了一种远程更新fpga的系统,其特征在于,设有cpu、fpga、开关矩阵以及flash存储器,其中所述开关矩阵内设有共用一个控制信号ctl的四个继电器,四个继电器分别为继电器a、继电器b、继电器c、继电器d;所述flash存储器包括至少一个可擦写flash存储器以及至少一个不可擦写flash存储器;所述cpu通过串口、can总线或网口从上位机获取fpga程序代码,并将获取的程序代码写入可擦写的flash中或通过gpio接口模拟jtag接口直接对fpga进行烧写,由cpu控制开关矩阵a和开关矩阵b(本专利仅描述设有两组flash的情况,若系统增加flash数量,开关矩阵数量也会相应的增加),开关矩阵a用于切换选择cpu或fpga的四路信号,所述四路信号分别为clk、cs、mosi、miso,开关矩阵b用于切换这四路信号是通往flash1或flash2,cpu使用gpio接口按照jtag时序模拟jtag接口,与fpga相连。

15.实施例1:

16.本例提出了一种远程更新fpga系统的方法,如附图2所示,本例能够使用多种冗余的方式对fpga的程序进行加载,具体包括:一、直接使用cpu的gpio接口按照jtag时序模拟jtag接口对fpga进行程序加载;二、开关矩阵a切换到模式二,由cpu决定使用哪片flash将其提前烧写好的程序向fpga加载;三、由cpu通过开关矩阵a的模式一,及开关矩阵b的模式二向flash2中重新烧写程序,再将开关矩阵a调到模式二,由flash2向fpga加载程序,本专

利仅描述了使用一片可擦写的flash的情况,也可增加可擦写flash的数量,有cpu控制多组开关矩阵向某个flash中烧写程序,并由改flash向fpga加载程序;

17.具体的说,当系统工作于第一种方式时,直接使用cpu的gpio接口模拟jtag时序对fpga进行程序加载,在cpu外扩的gpio接口中,选取四个接口,仿照jtag协议的四个接口:模式选择接口tms,时钟接口tck,数据输入接口tdi,数据输出接口tdo,分别配置其输入输出模式,再仿照jtag接口烧写fpga程序时的时序及协议,编写烧写程序,最终实现使用cpu读取由上位机传输的烧写文件,使用外扩gpio接口与fpga的jtag口连接,直接由cpu对fpga烧写程序;

18.具体的说,当系统工作于第二种方式时,开关矩阵a切换到模式二,由cpu决定使用哪片flash将其提前烧写好的程序向fpga加载,选取一片不可擦除的flash作为主flash,另用不少于一片的可擦写flash作为副flash,若仅使用一片副flash,则仅需配有两个开关矩阵,其中开关矩阵a为选通flash与fpga之间通道或者flash与cpu之间通道的,开关矩阵b为选通fpga与不同flash之间通道的,开关矩阵b随着flash的片数增加而相应增加,用于选通不同flash;由cpu的ctl1信号控制开关矩阵a切换到模式二,即选通flash与fpga之间的通道,再由cpu的ctl2信号控制开关矩阵b切换到模式一或模式二,用于选择不同的flash片对fpga进行程序烧写。

19.具体的说,当系统工作于第三种方式时,由cpu通过开关矩阵a的模式一,选通flash与cpu之间的通道;开关矩阵b处于模式二,选通cpu和可擦写的副flash,若有多片副flash,则需要相应的增加矩阵模块数量,上位机通过相应串口向cpu提供所需的烧写文件,将烧写文件烧写入所选择的副flash中;副flash重新烧写完毕后,再由cpu控制开关矩阵a调到模式二,选通副flash片与fpga,并将fpga上电,fpga将从副flash2中读取烧写文件,完成程序加载。

20.本发明通过上述技术方案,可以使用多种冗余的方式对fpga的程序进行加载。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1