一种基于ATE芯片测试的同步方法和系统与流程

一种基于ate芯片测试的同步方法和系统

技术领域

1.本发明涉及ate芯片测试技术,尤其涉及了一种基于ate芯片测试的同步方法和系统。

背景技术:

2.对于ate(automatic test equipment,自动测试设备):集成了大量的硬件组件,tmu组件可以代替示波器,pmu组件可以代替万用表等;兼容一种高等语言,可以通过编程实现自动化控制;可以轻易的发送任何想要的激励。

3.芯片测效率是ate设备的重要指标之一,芯片测试过程中,若每次测试都需要对每块业务板中测试程序执行结果进行采集与分析,则需要耗费大量的时间,大大影响芯片的测试效率。

4.例如专利名称,一种基于ate的mcu/soc芯片的测试方法;专利申请号:cn201410708882.7;申请日为:2014

‑

11

‑

28;专利中记载了一种基于ate的mcu/soc芯片的测试方法,该方法将ate作为基础平台,通过自定的通信协议,实现ate与其他器件的可靠通信。测试开始后,ate通过协议发送指令1和激励1给待测器件,自动记录测试数据1,再发送指令2和激励2给待测器件,自动记录测试数据2,直到完成所有项目测试。

5.现有技术对于每次测试都需要对每块业务板中测试程序执行结果进行采集与分析,则需要耗费大量的时间,大大影响芯片的测试效率。

技术实现要素:

6.本发明针对现有技术的ate芯片每次测试需要对每块业务板中测试程序执行结果进行采集与分析,则需要耗费大量时间,影响芯片测试效率缺点,提供了一种基于ate芯片测试的同步方法和系统。

7.为了解决上述技术问题,本发明通过下述技术方案得以解决:

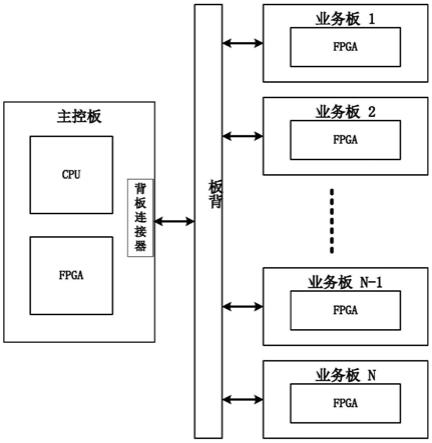

8.一种基于ate芯片测试的同步系统,包括主控板、n个业务板和背板,其中n为正整数;业务板通过背板与主控板通信;主控板包括主控cpu和主控fpga,业务板包括业务板fpga,业务板fpga包括fpga芯片测试执行模块,主控cpu的主程序发送芯片测试程序至主控fpga,主控fpga发送芯片测试程序至fpga芯片测试执行模块。通过在业务板的业务板fpga上设置fpga芯片测试执行模块,将芯片测试结果判断动作在业务板中同步实现,从而提高ate进行芯片测试时的测试效率,同时降低测试成本。

9.作为优选,主控fpga包括fpga同步控制模块,fpga同步控制模块包括同步寄存器和同步控制器;同步寄存器选择同步控制器的输入,即需要同步的业务板组合。

10.在主控fpga设置同步寄存器,能够很好地实现多块业务板测试结果的相互同步,只需要在测试程序运行前设置相关的同步寄存器,从而达到多块业务板测试结果互相同步。

11.作为优选,同步控制器与业务板相互对应。同步控制器与业务板一一对应,能够很

好地保证芯片测试过程中的同步性。

12.作为优选,同步寄存器为n bit位,每1bit控制一个业务板。

13.作为优选,同步控制器包括非门和与门;同步寄存器的信号通过非门,同业务板的芯片测试结果取或;取或后的结果与业务板的芯片测试结果取与。同步控制器的设计能够保证在对业务板进行测试时,保证了测试业务板的可选性,也就是进行任意组合的业务板进行测试。

14.作为优选,fpga通信管理模块,fpga通信管理模块与背板进行通信。

15.一种基于ate芯片测试的同步方法,包括ate芯片测试的同步系统,其同步方法为,

16.测试启动,主控cpu下发芯片测试程序至主控fpga,主控fpga发送芯片测试程序至业务板,业务板上的fpga芯片测试执行模块同步启动芯片测试;

17.测试运行,业务板fpga的fpga芯片测试执行模块进行芯片测试程序的运行;

18.芯片测试结果确定,业务板fpga的fpga芯片测试执行模块对芯片测试结果进行判断,成功则芯片测试结果信号置高,否则芯片测试结果信号置低;

19.测试结果同步,fpga芯片测试执行模块将芯片测试结果同步至主控板fpga的同步控制模块。

20.作为优选,还包括测试结果分析,主控板fpga对业务板的芯片测试结果进行同步,并确定多块业务板芯片测试结果。

21.作为优选,测试结果分析,主控板fpga接收的测试结果信号与预设的同步寄存器按位取或获得结果信号,结果信号是否全为高电平,若全为高电平则业务板芯片测试成功;否则业务板芯片测试失败,并反馈测试结果至对应业务板fpga。

22.作为优选,测试程序为带fpga测试指令的测试程序;若芯片测试结果成功,业务板fpga继续执行后续测试程序;若芯片测试结果失败,业务板fpga将芯片测试结果反馈至主控cpu的主程序。

23.本发明由于采用了以上技术方案,具有显著的技术效果:

24.通过在业务板上设置fpga芯片测试执行模块,将测试结果判断动作放在业务板中同步实现,从而提高芯片测试效率,降低测试成本。

25.在主控fpga设置同步寄存器,能够很好地实现多块业务板测试结果的相互同步,只需要在测试程序运行前设置相关的同步寄存器,从而达到多块业务板测试结果互相同步。每个业务卡执行芯片测试程序结束后,直接将测试结果通过物理连线的方式同步至主控板fpga中,再由主控板将同步后的芯片测试结果通过物理连线的方式传回至各个业务板的fpga,业务板上的测试程序根据同步后的结果获取整个测试系统中所业务板的测试情况,从而根据测试结果执行后续相应的测试动作。

26.本发明的同步方法能有效的节省主控cpu采集测试数据的时间,更快的完成业务板之间测试结果的互相同步,芯片测试时间短,芯片测试效率高。

附图说明

27.图1是本发明的系统图。

28.图2是本发明的系统图。

29.图3是本发明的同步控制器电路图。

30.图4是本发明的测试流程图。

31.图5是本发明的实施例测试流程图。

具体实施方式

32.下面结合附图与实施例对本发明作进一步详细描述。

33.实施例1

34.一种基于ate芯片测试的同步系统,包括主控板、n个业务板和背板,其中n为正整数;业务板通过背板与主控板通信;主控板包括主控cpu和主控fpga,业务板包括业务板fpga,业务板fpga包括fpga芯片测试执行模块;主控cpu的主程序发送芯片测试程序至主控fpga,主控fpga发送测试程序至fpga芯片测试执行模块,主控fpga发送测试程序至fpga芯片测试执行模块。

35.通过在业务板fpga上设置fpga芯片测试执行模块,将测试结果判断动作在业务板中同步实现,从而提高芯片测试效率,降低测试成本。

36.主控板fpga包括fpga通信管理模块,fpga通信管理模块与背板进行通信。背板通过高速接口将主控板与各个业务板连接在一起进行通信;背板通过通信背板连接器与主控板连接。主控板与各业务板件设置有物理连线。

37.主控fpga包括fpga同步控制模块,fpga同步控制模块包括同步寄存器和同步控制器;同步寄存器选择同步控制器的输入,即需要同步的业务板组合。

38.在主控fpga设置同步寄存器,能够很好地实现多块业务板测试结果的相互同步,只需要在测试程序运行前设置相关的同步寄存器,从而达到多块业务板测试结果互相同步。

39.同步控制器与业务板相互对应。同步控制器与业务板一一对应,能够很好地保证芯片测试过程中的同步性。

40.同步控制器包括非门和与门;同步寄存器的信号通过非门,同业务板的芯片测试结果取或;取或后的结果与业务板的芯片测试结果取与。同步控制器的设计能够保证进行测试业务板的可选性。

41.依据附图3所示同步控制器的电路图可知同步寄存器为n bit位,每1bit位控制1个业务板。第0bit寄存器控制对应业务板1,第n

‑

1bit寄存器控制对应业务板n;每一bit代表本业务板与其他业务板同步使能,设置为高有效。这里的n设置为16。

42.实施例2

43.一种基于ate芯片测试的同步方法,包括ate芯片测试的同步系统,依据附图4可知,其同步方法为,

44.测试启动,主控cpu下发芯片测试程序至主控fpga,主控fpga发送芯片测试程序至业务板,业务板上的fpga芯片测试执行模块同步启动芯片测试;

45.测试运行,业务板fpga的fpga芯片测试执行模块进行芯片测试程序的运行;

46.芯片测试结果确定,业务板fpga的fpga芯片测试执行模块对芯片测试结果进行判断,成功则芯片测试结果信号置高,否则芯片测试结果信号置低;

47.测试结果同步,fpga芯片测试执行模块将芯片测试结果同步至主控板fpga的同步控制模块。

48.实施例3

49.在上述实施例基础上,本实施例还包括测试结果分析,主控板fpga对业务板的芯片测试结果进行同步,并确定多块业务板芯片测试结果。

50.测试结果分析,主控板fpga接收的测试结果信号与预设的同步寄存器按位取或获得结果信号,结果信号是否全为高电平,若全为高电平则业务板芯片测试成功;否则业务板芯片测试失败,并反馈测试结果至对应业务板fpga。

51.测试程序为带fpga芯片测试指令的测试程序;若芯片测试结果成功,业务板fpga继续执行后续的测试程序;若芯片测试结果失败,业务板fpga将测试结果反馈至主控cpu的主程序。

52.实施例4

53.依据附图5可知,在现有技术中对业务板芯片进行测试时,主控cpu的主程序下发测试程序启动测试,业务板接收测试测试后,所有的业务板均进行测试程序的运行;判断主控cpu查询测试结束,结束则主控cpu采集所有业务板测试结果;主控cpu对测试结果分析;否则重新运行测试程序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1