一种数据加密方法、装置、内存控制器、芯片及电子设备与流程

1.本技术实施例涉及芯片技术领域,具体涉及一种数据加密方法、装置、内存控制器、芯片及电子设备。

背景技术:

2.内存(memory)是电子设备(例如计算机)的重要部件之一,用于与cpu(central processing unit,中央处理器)交换高速缓存数据。例如,内存中被cpu频繁访问的数据可被复制到缓存(cache)中,而缓存中不再被cpu频繁访问的数据可更换到内存中,以保障cpu能够从缓存读取到频繁访问的数据,加快cpu的数据读取速度。可见,内存中暂时存放着cpu的运算数据,因此保障内存中数据的安全性具有重要意义。

技术实现要素:

3.本技术实施例提供一种数据加密方法、装置、内存控制器、芯片及电子设备,适用于对整个内存进行数据加密,并提升数据加密的安全性和可靠性。

4.为实现上述目的,本技术实施例提供如下技术方案。

5.第一方面,本技术实施例提供一种数据加密方法,包括:

6.检测向内存写数据的写指令,所述写指令至少指示需写入内存的明文数据;

7.对加密密钥进行混淆处理,以得到混淆密钥;

8.根据所述混淆密钥对所述明文数据进行加密处理,以得到加密值;

9.根据所述加密值得到所述明文数据对应的密文数据;

10.将所述密文数据写入内存。

11.第二方面,本技术实施例提供一种数据加密装置,包括:

12.指令检测模块,用于检测向内存写数据的写指令,所述写指令至少指示需写入内存的明文数据;

13.混淆模块,用于对加密密钥进行混淆处理,以得到混淆密钥;

14.加密模块,用于根据所述混淆密钥对所述明文数据进行加密处理,以得到加密值;

15.密文得到模块,用于根据所述加密值得到所述明文数据对应的密文数据;

16.写入模块,用于将所述密文数据写入内存。

17.第三方面,本技术实施例提供一种内存控制器,所述内存控制器被配置为执行如上述第一方面所述的数据加密方法。

18.第四方面,本技术实施例提供一种芯片,所述芯片包括如上述第三方面所述的内存控制器。

19.第五方面,本技术实施例提供一种电子设备,所述电子设备包括如上述第四方面所述的芯片。

20.本技术实施例提供的数据加密方法,可在检测到向内存写数据的写指令时,对加密密钥进行混淆处理,得到混淆密钥;再根据混淆密钥对需写入内存的明文数据进行加密

处理,得到明文数据的加密值;从而根据该加密值得到明文数据对应的密文数据,将该密文数据写入内存,以实现在向内存写数据时,保障写入内存的数据为密文数据,实现内存中数据的加密保护。由于本技术实施例是对加密密钥进行混淆处理后,再根据混淆密钥对需写入内存的明文数据进行加密,因此可保障内存中不同内存块使用的混淆密钥是不同的。也就是说,相同的明文数据需写入不同内存块时,不同内存块对应的相同明文数据的加密值能够不同,降低了加密使用的信息被泄露的风险,提升了内存中密文数据被破解的难度,提升了数据加密的安全性和可靠性。另外,由于本技术实施例并不需要在内存中额外存储每个内存块的计数值,因此可减少内存的存储空间消耗,能够适用于对整个内存进行数据加密。本技术实施例提供的数据加密方法可适用于对整个内存进行数据加密,并提升数据加密的安全性和可靠性。

附图说明

21.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

22.图1为电子设备的可选架构示意图。

23.图2为电子设备的另一可选架构示意图。

24.图3为本技术实施例提供的数据加密方法的可选流程图。

25.图4为本技术实施例提供的数据加密方法的可选实现示意图。

26.图5为本技术实施例提供的得到处理参数值的可选流程图。

27.图6为本技术实施例提供的数据加密方法的另一可选流程图。

28.图7为申请实施例实现密钥混淆的可选流程图。

29.图8为本技术实施例提供的完整性保护树的结构示意图。

30.图9为本技术实施例提供的密文数据的完整性保护流程图。

31.图10为本技术实施例提供的数据加密装置的可选框图。

32.图11为本技术实施例提供的数据加密装置的另一可选框图。

33.图12为本技术实施例提供的数据加密装置的再一可选框图。

具体实施方式

34.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

35.图1为电子设备的可选架构示意图。如图1所示,电子设备可以包括:cpu核110、缓存120、内存控制器(memory controller,mc)130和内存140。在一些实施例中,cpu核110、缓存120和内存控制器130可集成在芯片中。例如,cpu核110、缓存120和内存控制器130集成于soc(system on chip,片上系统)芯片。

36.在图1所示架构中,内存控制器130作为缓存120和内存140交换数据的桥梁,可将

缓存120中的数据写入内存140中,也可从内存140读取数据并送入缓存120中。例如,cpu核110从缓存120中寻找不到数据时,可控制内存控制器130从内存140中读取数据并送入缓存120,以供cpu核110使用。缓存120中不再被cpu核110频繁访问的数据,可由内存控制器130写入到内存140中。

37.内存140中暂时存放着cpu核110的运算数据,为保护内存中数据的安全性,内存控制器130可引入内存加密引擎(memory encrypt engine)对写入内存的数据进行加密保护。图2示出了电子设备的另一可选架构示意图。结合图1和图2所示,cpu核110、缓存120和内存控制器130可集成于芯片150,并且内存控制器130中设置有内存加密引擎131,用于对写入内存的数据进行加密,对内存中读出的数据进行解密。

38.当数据需从缓存120写入内存140时,内存控制器130中的内存加密引擎131可将数据加密成密文数据,再将密文数据写入内存140中;当密文数据需从内存140读取到缓存120时,内存加密引擎131可将内存140中的密文数据解密成明文数据,再将明文数据送入缓存120中。也就是说,芯片150中的数据是以明文的形式存在,而内存140中的数据是以密文的形式存在,从而对内存140中的数据实现加密保护。

39.可以看出,当需要将缓存120中的明文数据写入内存140时,内存加密引擎131可使用数据加密方式,将明文数据加密成密文数据,再将密文数据写入内存140。在这个过程中,如果内存加密引擎131使用的数据加密方式的安全性和可靠性较低,则密文数据存在极易被破解的风险,因此亟需提升数据加密的安全性和可靠性。

40.本技术实施例提供新型的数据加密方案,适用于对整个内存进行数据加密,并提升数据加密的安全性和可靠性。

41.图3示出了本技术实施例提供的数据加密方法的可选流程图。在一些实施例中,该数据加密方法可基于图2所示架构实施,并由内存控制器130执行该数据加密方法。例如,可由内存控制器130中的内存加密引擎131执行该数据加密方法。如图3所示,该流程可以包括如下步骤。

42.在步骤s10中,检测向内存写数据的写指令,所述写指令至少指示需写入内存的明文数据。

43.在一些实施例中,当缓存120中的明文数据需更换到内存140中时,内存控制器130可检测到向内存写数据的写指令。该写指令可由cpu核110产生并传递给内存控制器130,以使得内存控制器130检测到该写指令。例如,cpu核110可定期确定缓存120中访问频率低于预定频率的明文数据,针对该明文数据,产生向内存写数据的写指令并传递给内存控制器130,以实现将缓存120中不再频繁访问的明文数据更换到内存140中。

44.在一些实施例中,该写指令可至少指示缓存中需写入内存140的明文数据。在进一步的一些实施例中,该写指令还可指示该明文数据需写入内存140的内存地址。

45.在步骤s11中,对加密密钥进行混淆处理,以得到混淆密钥。

46.在步骤s12中,根据所述混淆密钥对所述明文数据进行加密处理,以得到加密值。

47.内存控制器130(具体可以是内存控制器130中的内存加密引擎131)可产生用于数据加密的加密密钥。需要说明的是,本技术实施例并不是直接使用加密密钥对明文数据进行加密处理,而是先对加密密钥进行混淆处理,得到混淆密钥;再使用混淆密钥对明文数据进行加密处理,得到加密值。

48.先对加密密钥进行混淆处理,再利用混淆密钥对明文数据进行加密处理的好处在于:保障相同的明文数据基于不同的混淆密钥,可得到不同的加密值,提升数据加密的安全性和可靠性。

49.具体来说,加密密钥可以是电子设备启动后,由内存加密引擎131基于随机数生成。对于内存140中的不同内存块,如果直接使用加密密钥进行加密处理,则不同内存块使用的加密密钥都是相同的,这将导致相同明文数据需写入不同内存块时,相同明文数据对应的加密值也是相同的;也就是说,内容相同的明文数据需写入不同内存块时,如果直接使用加密密钥对明文数据进行加密处理,则不同内存块中对应的相同明文数据的加密值也是相同的,这导致内存中的密文数据极易被破解,数据加密的安全性和可靠性较低。因此,本技术实施例先对加密密钥进行混淆处理,得到混淆密钥,再根据混淆密钥对明文数据进行加密处理,可保障不同内存块使用的混淆密钥是不同的。从而内容相同的明文数据需写入不同内存块时,不同内存块中对应的相同明文数据的加密值能够不同,提升了数据加密的安全性和可靠性。

50.在一些实施例中,本技术实施例可根据明文数据写入内存的内存地址,对加密密钥进行混淆处理,以得到混淆密钥。从而,相同的明文数据需写入内存中不同的内存地址时,由于用于密钥混淆的内存地址不同,因此针对写入不同内存地址的相同明文数据,可得到不同的加密值,能够保障相同的明文数据得到的加密值是不同的,提升数据加密的安全性和可靠性。当然,基于明文数据写入内存的内存地址,对加密密钥进行混淆处理仅是一种可选手段,本技术实施例也可基于其他信息(例如明文数据的数据大小、当前时间等),对加密密钥进行混淆处理。

51.在一些实施例中,本技术实施例可基于分组加密算法,对所述明文数据进行加密处理,得到加密值。在其他可能的实施例中,本技术实施例也可基于流加密算法(例如祖冲之加密算法),对所述明文数据进行加密处理,得到加密值。当然,本技术实施例并不限制加密处理所使用的加密算法,任何能够用于加密处理的加密算法均可适用于本技术实施例。

52.在步骤s13中,根据所述加密值得到所述明文数据对应的密文数据。

53.在根据所述混淆密钥对所述明文数据进行加密处理,得到明文数据的加密值后,本技术实施例可基于该加密值得到明文数据对应的密文数据。在一些实施例中,本技术实施例可直接将该加密值作为明文数据对应的密文数据。在其他可能的一些实施例中,本技术实施例也可对该加密值进行进一步的处理,得到明文数据对应的密文数据。例如,本技术实施例可基于明文数据需写入内存的内存地址生成处理参数值,再将该处理参数值与加密值进行结合处理(例如,将该处理参数值与加密值进行异或处理等),得到明文数据对应的密文数据。

54.在步骤s14中,将所述密文数据写入内存。

55.在一些实施例中,本技术实施例可基于写指令指示的明文数据需写入内存的内存地址,将密文数据写入内存中。

56.本技术实施例提供的数据加密方法,可在检测到向内存写数据的写指令时,对加密密钥进行混淆处理,得到混淆密钥;再根据混淆密钥对需写入内存的明文数据进行加密处理,得到明文数据的加密值;从而根据该加密值得到明文数据对应的密文数据,将该密文数据写入内存,以实现在向内存写数据时,保障写入内存的数据为密文数据,实现内存中数

据的加密保护。由于本技术实施例是对加密密钥进行混淆处理后,再根据混淆密钥对需写入内存的明文数据进行加密,因此可保障内存中不同内存块使用的混淆密钥是不同的。也就是说,相同的明文数据需写入不同内存块时,不同内存块对应的相同明文数据的加密值能够不同,降低了加密使用的信息被泄露的风险,提升了内存中密文数据被破解的难度,提升了数据加密的安全性和可靠性。另外,由于本技术实施例并不需要在内存中额外存储每个内存块的计数值,因此可减少内存的存储空间消耗,能够适用于对整个内存进行数据加密。本技术实施例提供的数据加密方法可适用于对整个内存进行数据加密,并提升数据加密的安全性和可靠性。

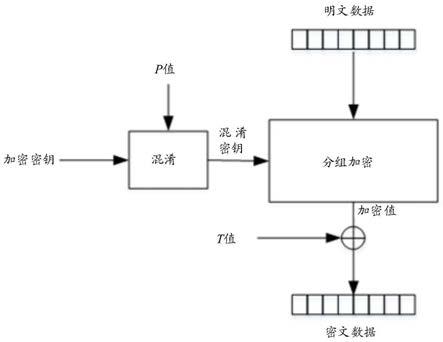

57.图4示出了图3所示数据加密方法的可选实现示意图。在图4所示示意中,加密值可进一步与处理参数值(处理参数值例如图4所示t值)进行异或处理,得到明文数据对应的密文数据。图4所示实现过程可在内存加密引擎131检测到向内存写数据的写指令时执行,该写指令可以指示需写入内存的明文数据,以及明文数据需写入内存140的内存地址(内存地址例如图4所示p值)。

58.如图4所示,内存加密引擎131产生的加密密钥可与p值进行混淆,得到混淆密钥。然后,根据混淆密钥对明文数据进行分组加密处理,得到加密值。加密值可与t值进行异或处理,得到密文数据。从而,密文数据可基于写指令指示的内存地址(即p值)写入内存140中。当然,本技术实施例也可根据混淆密钥对明文数据进行其他形式的加密算法处理,得到加密值;例如,可根据混淆密钥对明文数据进行流加密处理等,得到加密值。本技术实施例也可支持加密值与t值进行其他形式的结合处理,以得到密文数据,而不限于异或处理。

59.在一些实施例中,处理参数值(即t值)可基于明文数据需写入内存的内存地址得到。图5示出了得到处理参数值的可选流程图。图5所示流程可由内存控制器130(具体可以是内存控制器130中的内存加密引擎131)执行,如图5所示,该流程可以包括如下步骤。

60.在步骤s20中,确定计数器的计数值。

61.在检测到所述写指令时,内存控制器130可确定计数器的计数值。计数器可以位于内存控制器130内,也可能是位于芯片150内的器件。

62.在步骤s21中,从内存地址的最低有效位中确定顺序与所述计数值相应的比特值。

63.在确定计数器的计数值后,本技术实施例可基于该计数值,从内存地址的最低有效位中确定相应的比特值。在一些实施例中,本技术实施例可按照该计数值,从内存地址的最低有效位中确定顺序与该计数值相应的比特值。例如,设j为计数器的计数值,则本技术实施例可从内存地址的最低有效位中确定顺序与j相应的比特值(即,内存地址的最低有效位的第j个比特值)。

64.在步骤s22中,根据所述比特值、内存地址的比特位个数、计数器的计数值以及设定常数,确定处理参数值。

65.在从内存地址中确定比特值后,本技术实施例可基于所述比特值、内存地址的比特位个数、计数器的计数值以及设定常数,确定出处理参数值。在一些实施例中,本技术实施例可将所述比特值与设定常数相乘,得到相乘结果,再根据内存地址的比特位个数、计数器的计数值和相乘结果进行运算,得到处理参数值。所述运算可以例如异或运算;例如,本技术实施例可将所述比特值与设定常数相乘,得到相乘结果,再根据内存地址的比特位个数、计数器的计数值和相乘结果进行异或运算处理,得到处理参数值。当然,本技术实施例

也可支持其他形式的运算,而不限于异或运算。

66.在一些实施例中,t值可定义为其中,bit(p,j)为内存地址p的最低有效位的第j个比特值,j为计数器的计数值,n是内存地址p的比特位个数,t

j

为设定常数(数值可以固定),

⊕

表示异或运算。

67.在一些实施例中,内存加密引擎在得到混淆密钥后,可根据所述混淆密钥对所述明文数据进行多轮迭代的加密运算,以得到加密值;即,明文数据可通过多轮迭代的加密运算(例如32轮迭代的加密运算)来实现加密处理,其中,每轮加密运算需要使用到密钥混淆处理得到的混淆密钥。

68.在一些实施例中,用于对明文数据进行加密处理的混淆密钥可以包括:每轮加密运算使用的混淆密钥。例如,本技术实施例可根据明文数据的内存地址对每轮加密运算使用的轮密钥进行混淆处理,以得到每轮加密运算使用的混淆密钥。图6示出了本技术实施例提供的数据加密方法的另一可选流程图。如图6所示,该流程可以包括如下步骤。

69.在步骤s30中,检测向内存写数据的写指令,所述写指令至少指示需写入内存的明文数据以及明文数据需写入内存的内存地址。

70.在步骤s31中,通过密钥扩展算法,产生每轮加密运算使用的轮密钥。

71.在基于多轮迭代的加密运算实现明文数据的加密处理的情况下,本技术实施例需确定每轮加密运算使用的轮密钥。每轮加密运算使用的轮密钥可以视为是:内存加密引擎通过密钥扩展算法,生成的用于每轮加密运算的加密密钥。由于本技术实施例并不是直接基于每轮加密运算使用的轮密钥,对明文数据进行多轮迭代加密,而是需要将每轮加密运算使用的轮密钥进行混淆处理后,再基于混淆密钥对明文数据进行多轮迭代加密,因此每轮加密运算使用的轮密钥可以视为是本技术实施例进行密钥混淆的对象。

72.在步骤s32中,根据所述内存地址,对每轮加密运算使用的轮密钥进行混淆处理,得到每轮加密运算使用的混淆密钥。

73.在步骤s33中,根据每轮加密运算使用的混淆密钥,对明文数据进行多轮迭代的加密运算,以得到加密值;其中,一轮加密运算基于相应轮的混淆密钥实现。

74.本技术实施例可利用内存地址,对每轮加密运算使用的轮密钥进行混淆处理,得到每轮加密运算使用的混淆密钥。从而内存加密引擎可基于每轮加密运算使用的混淆密钥,对明文数据进行多轮迭代的加密运算,得到明文数据的加密值。其中,一轮加密运算可以基于相应轮的混淆密钥进行加密处理。以进行32轮的迭代加密运算为例,则第1轮加密运算可基于第1轮的混淆密钥实现,第2轮加密运算可基于第2轮的混淆密钥实现,以此类推,直至第32轮的加密运算可基于第32轮的混淆密钥实现。

75.在步骤s34中,将所述加密值与处理参数值进行异或处理,得到明文数据对应的密文数据;其中,所述处理参数值基于所述内存地址生成。

76.在对明文数据进行多轮迭代的加密运算,得到加密值后,本技术实施例可进一步将加密值与处理参数值进行异或处理,得到最终的密文数据。处理参数值的得到过程可参照前文相应部分的描述,此处不再赘述。

77.当然,步骤s34仅是进一步提升数据加密安全性和可靠性的可选手段,本技术实施例也可不实施步骤s34,而是将加密值直接作为密文数据。

78.在步骤s35中,根据所述内存地址,将密文数据写入内存中。

79.本技术实施例在基于多轮迭代的加密运算,将明文数据转换为加密值的情况下,可利用明文数据需写入内存的内存地址,对每轮加密运算使用的轮密钥进行混淆,得到每轮加密运算使用的混淆密钥。从而基于每轮加密运算使用的混淆密钥,对明文数据进行多轮迭代的加密运算,得到相应的加密值,并最终得到密文数据。本技术实施例通过对每轮加密运算使用的轮密钥进行混淆,来得到每轮加密运算使用的混淆密钥,可使得明文数据进行多轮迭代的加密运算后,加密值的破解难度提升,进一步提升了数据加密的安全性和可靠性。

80.作为一种可选实现,图7示出了本技术实施例实现密钥混淆的可选流程图。在一些实施例中,本技术实施例可基于图7所示流程实现图6所示步骤s32。图7所示流程可由内存控制器130(具体可以是内存控制器130中的内存加密引擎131)执行,如图7所示,该流程可以包括如下步骤。

81.在步骤s40中,将内存地址的高比特位值和低比特位值进行处理,得到地址初始处理值。

82.在一些实施例中,针对明文数据需写入内存的内存地址,本技术实施例可确定内存地址的高比特位值和低比特位值,将高比特位值和低比特位值进行异或处理(当然,本技术实施例也可支持其他的处理形式,而不限于异或处理),得到地址初始处理值。例如,可设内存地址p=(ad0,ad1),ad0为内存地址p的高比特位值,ad1为内存地址p的低比特位值,本技术实施例可将内存地址p的高比特位值ad0和低比特位值ad1进行异或处理,得到地址初始处理值。设地址初始处理值为ak,则ak=ad0⊕

ad1。在进一步的示例中,以64位的内存地址p为例,则ad0可以是内存地址p的高32位比特位值,ad1可以是内存地址p的低32位比特位值,并且

83.在步骤s41中,根据所述地址初始处理值,得到分别与每轮加密运算相对应的地址目标处理值。

84.在一些实施例中,本技术实施例可直接将地址初始处理值作为与每轮加密运算相对应的地址目标处理值;也就是说,每轮加密运算对应的地址目标处理值相同。在另一些实施例中,本技术实施例可将地址初始处理值进行进一步的处理后,得到与每轮加密运算相对应的地址目标处理值,且每轮加密运算相对应的地址目标处理值不同。例如,本技术实施例可根据每轮加密运算的轮数,分别将地址初始处理值进行循环左移位运算,得到与每轮加密运算相对应的地址目标处理值。在一个示例中,针对第i轮加密运算,本技术实施例可根据第i轮加密运算的轮数i,将地址初始处理值进行循环左移位运算,得到第i轮加密运算相对应的地址目标处理值ak

i

,即ak

i

=ak<<<i。

85.在步骤s42中,将每轮加密运算相对应的地址目标处理值,分别与相应轮加密运算使用的轮密钥进行混淆,得到每轮加密运算使用的混淆密钥。

86.在一些实施例中,本技术实施例可将每轮加密运算相对应的地址目标处理值,分别与相应轮加密运算使用的轮密钥进行异或处理,得到每轮加密运算使用的混淆密钥。例如,本技术实施例可将第1轮加密运算相对应的地址目标处理值,与第1轮加密运算使用的轮密钥进行异或处理,得到第1轮加密运算使用的混淆密钥;将第2轮加密运算相对应的地址目标处理值,与第2轮加密运算使用的轮密钥进行异或处理,得到第2轮加密运算使用的

混淆密钥,以此类推,直至得到每轮加密运算使用的混淆密钥。

87.在一个示例中,本技术实施例可以使用sm4算法对明文数据进行多轮迭代的加密运算,以得到相应的加密值。sm4算法是一个分组密码算法,分组大小为128bit(比特),使用sm4算法进行加密涉及多轮迭代的加密运算以及密钥扩展算法,每轮加密运算需要使用密钥扩展算法生成的轮密钥来实现。以进行32轮迭代的加密运算为例,则32轮迭代的加密运算使用到的轮密钥可以设为rk,且rk=(rk0,rk1,...rk

31

),其中,rk0可以视为是第1轮加密运算使用的轮密钥,rk1可以视为是第2轮加密运算使用的轮密钥,以此类推,rk

31

可以是第32轮加密运算使用的轮密钥。设第i轮加密运算的轮密钥为rk

i

,i为0至31的整数,则第i轮加密运算相对应的地址目标处理值ak

i

可与第i轮加密运算的轮密钥rk

i

进行异或处理,得到第i轮加密运算使用的混淆密钥。设第i轮加密运算使用的混淆密钥为rk

i

',则rk

i

'=rk

i

⊕

ak

i

。以进行32轮迭代的加密运算为例,则本技术实施例可得到32轮加密运算分别使用的混淆密钥(rk0',rk1',...,rk

31

'),可选的,第i轮加密运算使用的混淆密钥

88.需要说明的是,图7所示的基于内存地址,对每轮加密运算使用的轮密钥进行混淆的流程仅是一种可选实现手段,本技术实施例也可支持其他的混淆手段,例如,只要能够在每轮加密运算使用的轮密钥中混合入所述内存地址的信息或者所述内存地址处理后的信息,则均可达成对每轮加密运算使用的轮密钥进行混淆处理的目的。

89.需要说明的是,使用sm4算法对明文数据进行多轮迭代的加密运算仅是一种可选手段,本技术实施例也可支持其他类型的加密算法,例如sm1,sm7,ssf33等加密算法。

90.在得到每轮加密运算使用的混淆密钥之后,本技术实施例可根据每轮加密运算使用的混淆密钥,对明文数据进行多轮迭代的加密运算,以得到加密值。提升加密值的破解难度,进一步提升数据加密的安全性和可靠性。

91.在进一步的一些实施例中,内存控制器在将密文数据写入内存时,还可引入密文数据的完整性保护机制,以抵御重放攻击等问题。密文数据的完整性保护机制可基于完整性保护树实现,本技术实施例可通过生成密文数据对应的完整性保护树,来实现密文数据的完整性保护机制。图8示出了本技术实施例提供的完整性保护树的结构示意图。结合图8所示,完整性保护树包括多个节点层(例如图8所示的第0层节点层、第1层节点层、第2层节点层和第3层节点层),一个节点层包括至少一个节点(例如第1层节点层中的节点11),一个节点中的数据至少包括:至少一个局部计数器(例如节点11中的n1000至n1127)和与所述局部计数器对应的全局计数器(例如节点11中的g1000)。

92.其中,非末端节点层(例如第1层节点层至第3层节点层)中一个节点的一个局部计数器用于直接关联下一节点层中的一个节点(例如第1层节点层中的节点11中的n1000可直接关联第0层节点层中的节点01)。末端节点层(例如第0层节点层)中一个节点的一个局部计数器,用于直接关联密文数据对应的一个数据项(例如第0层节点层的节点01中的n0000可直接关联密文数据对应的数据项d0);其中,密文数据可对应多个数据项(例如图8所示数据项d0至数据项d127),密文数据对应的数据项的数量可根据实际情况而定,本技术实施例并不设限。

93.完整性保护树中除根节点层(例如图8所示第3层节点层)外的每个节点配置有用于进行验证的mac(message authentication code,消息认证码),一个节点的mac基于该节点中的数据、与该节点直接关联的局部计数器、和与该局部计数器对应的全局计数器计算

得到。例如,节点01的mac可基于节点01中的数据、与节点01直接关联的局部计数器n1000、以及与局部计数器n1000对应的全局计数器g1000计算得到。

94.在生成密文数据对应的完整性保护树后,本技术实施例可将完整性保护树的根节点层存储在芯片的安全存储空间,而将除根节点层外的其他节点层存储在内存中。基于密文数据对应的完整性保护树,本技术实施例可在验证密文数据完整的情况下,再将密文数据写入内存或者从内存读取密文数据。

95.图9示出了本技术实施例提供的密文数据的完整性保护流程图。该流程可由内存控制器(具体可以是内存控制器中的内存加密引擎)执行,如图9所示,该流程可以包括如下步骤。

96.在步骤s50中,确定页表中密文数据对应的数据项。

97.本技术实施例可在密文数据对应的数据项在内存被读取或被写入前,对密文数据对应的数据项进行页表完整性保护。通过对密文数据对应的数据项的页表的完整性保护,可以确定密文数据对应的数据项是否被篡改。

98.可选的,页表(tag)可以为普通页表,可以为客户机页表,也可以为嵌套页表,或者,可以为客户机页表和嵌套页表的总和。页表中密文数据对应的数据项可以是页表中用于实现密文数据的地址映射的表项,一个数据项可以为一个页表项,也可以为一个页目录项。一个数据项的长度可以为内存中一个物理块的长度,也即计算机的一个缓存行长度。

99.在步骤s51中,从完整性保护树的根节点层的下一节点层开始,依序对完整性保护树的各节点层中的目标节点进行验证,直至验证到完整性保护树的末端节点层中的目标节点;其中,目标节点为与密文数据对应的数据项关联的节点。

100.完整性保护树中的一个节点层包括至少一个节点。所述目标节点为完整性保护树中与密文数据对应的数据项关联的节点。基于与该数据项的关联关系,可以从完整性保护树的非根节点层的节点中确定目标节点,从而逐层对目标节点进行验证。结合图8所示完整性保护树的结构,以数据项d0为例,则与数据项d0关联的目标节点包括节点01、节点11、节点21和根节点。

101.在对目标节点的验证过程中,由于所述根节点层存储在芯片的安全存储区域,因此本技术实施例可从完整性保护树的根节点层的下一节点层开始,自上而下的逐层对目标节点进行验证,直至验证到完整性保护树的末端节点层。在这个过程中,在验证当前节点层时,本技术实施例可基于目标节点中的数据、与目标节点直接关联的局部计数器、与该局部计数器对应的全局计数器,计算得到所述目标节点的节点待验证值;然后比较所述节点待验证值和所述目标节点的mac是否一致;若一致,则继续验证下一节点层;若不一致,则可确定密文数据对应的数据项不完整,终止密文数据写入内存或者从内存中读出。

102.在一个示例中,以验证第2层节点层为例,第2层节点层中与密文数据对应的数据项关联的目标节点为节点21,则本技术实施例可基于节点21中的数据(全局计数器g2000以及局部计数器n2000至n2127)、与节点21直接关联的局部计数器n3000、局部计数器n3000对应的全局计数器g3000,计算新的mac值,该新的mac值可作为节点21的节点待验证值;然后,比较该新的mac值与节点21的mac值是否一致;若一致,则继续验证下一节点层;若不一致,则可确定密文数据对应的数据项不完整,终止密文数据写入内存或者从内存中读出。

103.需要说明的是,与目标节点直接关联的局部计数器位于目标节点所在节点层的上

一节点层中(例如,以验证到目标节点11为例,则与节点11直接关联的局部计数器为第2层节点层中节点21的局部计数器n2000)。而与局部计数器对应的全局计数器,是与该局部计数器位于同一节点中(例如局部计数器n2000对应的全局计数器g2000均位于节点21中)。

104.在一些实施例中,本技术实施例可以使用杂凑函数对目标节点中的数据、与目标节点直接关联的局部计数器、与该局部计数器对应的全局计数器进行计算,生成摘要值,从而得到目标节点的节点待验证值。

105.在步骤s52中,基于所述目标节点的验证结果,确定密文数据的完整性验证结果。

106.在一些实施例中,若完整性保护树的各节点层中的目标节点均验证通过,则确定密文数据对应的数据项的完整性验证通过,可在内存对密文数据进行读取或者写入;若完整性保护树中存在任一节点层的目标节点验证不通过,则确定密文数据对应的数据项不完整,终止密文数据写入内存或者从内存中读出。

107.本技术实施例通过引入密文数据的完整性保护树,对密文数据进行完整性验证,并在密文数据的完整性验证通过时,才在内存对密文数据进行读取或者写入,可进一步提升对密文数据的安全保护。

108.上文描述了本技术实施例提供的多个实施例方案,各实施例方案介绍的各可选方式可在不冲突的情况下相互结合、交叉引用,从而延伸出多种可能的实施例方案,这些均可认为是本技术实施例披露、公开的实施例方案。

109.下面对本技术实施例提供的数据加密装置进行介绍。下文描述的装置内容可以认为是内存控制器(具体可以是内存控制器中的内存加密引擎)为实现本技术实施例提供的数据加密方法,所需设置的功能模块。下文描述的装置内容可与上文描述的内容相互对应参照。

110.作为一种可选实现,图10示出了本技术实施例提供的数据加密装置的可选框图。该装置可应用于内存控制器(具体可以是内存控制器中的内存加密引擎)。如图10所示,该装置可以包括:

111.指令检测模块1,用于检测向内存写数据的写指令,所述写指令至少指示需写入内存的明文数据;

112.混淆模块2,用于对加密密钥进行混淆处理,以得到混淆密钥;

113.加密模块3,用于根据所述混淆密钥对所述明文数据进行加密处理,以得到加密值;

114.密文得到模块4,用于根据所述加密值得到所述明文数据对应的密文数据;

115.写入模块5,用于将所述密文数据写入内存。

116.在一些实施例中,所述写指令还指示明文数据需写入内存的内存地址。混淆模块2,用于对加密密钥进行混淆处理,以得到混淆密钥包括:

117.根据所述内存地址对所述加密密钥进行混淆处理,以得到混淆密钥。

118.在一些实施例中,所述混淆密钥包括:每轮加密运算使用的混淆密钥。加密模块3,用于根据所述混淆密钥对所述明文数据进行加密处理,以得到加密值包括:

119.根据每轮加密运算使用的混淆密钥,对明文数据进行多轮迭代的加密运算,以得到加密值;其中,一轮加密运算基于相应轮的混淆密钥实现。

120.在一些实施例中,混淆模块2,用于根据所述内存地址对所述加密密钥进行混淆处

理,以得到混淆密钥包括:

121.通过密钥扩展算法,产生每轮加密运算使用的轮密钥;

122.根据所述内存地址,对每轮加密运算使用的轮密钥进行混淆处理,得到每轮加密运算使用的混淆密钥。

123.在一些实施例中,混淆模块2,用于根据所述内存地址,对每轮加密运算使用的轮密钥进行混淆处理,得到每轮加密运算使用的混淆密钥包括:

124.将内存地址的高比特位值和低比特位值进行处理,得到地址初始处理值;

125.根据所述地址初始处理值,得到分别与每轮加密运算相对应的地址目标处理值;

126.将每轮加密运算相对应的地址目标处理值,分别与相应轮加密运算使用的轮密钥进行混淆,得到每轮加密运算使用的混淆密钥。

127.在一些实施例中,混淆模块2,用于将内存地址的高比特位值和低比特位值进行处理,得到地址初始处理值包括:

128.将所述内存地址的高比特位值和低比特位值进行异或处理,得到地址初始处理值。

129.在一些实施例中,混淆模块2,用于根据所述地址初始处理值,得到分别与每轮加密运算相对应的地址目标处理值包括:

130.根据每轮加密运算的轮数,分别将地址初始处理值进行循环左移位运算,得到与每轮加密运算相对应的地址目标处理值。

131.在一些实施例中,混淆模块2,用于将每轮加密运算相对应的地址目标处理值,分别与相应轮加密运算使用的轮密钥进行混淆,得到每轮加密运算使用的混淆密钥包括:

132.将每轮加密运算相对应的地址目标处理值,分别与相应轮加密运算使用的轮密钥进行异或处理,得到每轮加密运算使用的混淆密钥。

133.图11示出了本技术实施例提供的数据加密装置的另一可选框图。结合图10和图11所示,该装置还可以包括:

134.处理参数值确定模块6,用于根据所述内存地址,确定处理参数值。

135.在一些实施例中,密文得到模块4,用于根据所述加密值得到所述明文数据对应的密文数据包括:

136.将所述加密值与所述处理参数值进行异或处理,得到所述明文数据对应的密文数据。

137.在一些实施例中,处理参数值确定模块6,用于根据所述内存地址,确定处理参数值包括:

138.确定计数器的计数值;

139.从所述内存地址的最低有效位中确定顺序与所述计数值相应的比特值;

140.根据所述比特值、所述内存地址的比特位个数、计数器的计数值以及设定常数,确定处理参数值。

141.图12示出了本技术实施例提供的数据加密装置的再一可选框图。结合图10和图12所示,该装置还可以包括:

142.保护树生成模块7,用于生成所述密文数据对应的完整性保护树;所述完整性保护树包括多个节点层,一个节点层包括至少一个节点,一个节点中的数据至少包括:至少一个

局部计数器和与所述局部计数器对应的全局计数器;非末端节点层中一个节点的一个局部计数器用于直接关联下一节点层中的一个节点,末端节点层中一个节点的一个局部计数器用于直接关联密文数据对应的一个数据项;所述完整性保护树中除根节点层外的每个节点配置有用于进行验证的mac,一个节点的mac基于该节点中的数据、与该节点直接关联的局部计数器、和与该局部计数器对应的全局计数器计算得到;其中,完整性保护树的根节点层存储在芯片的安全存储空间,除根节点层外的其他节点层存储在内存中;

143.验证模块8,用于确定页表中密文数据对应的数据项;从完整性保护树的根节点层的下一节点层开始,依序对完整性保护树的各节点层中的目标节点进行验证,直至验证到完整性保护树的末端节点层中的目标节点,所述目标节点为与密文数据对应的数据项关联的节点;基于所述目标节点的验证结果,得出密文数据的完整性验证结果;

144.读写控制模块9,用于若所述完整性验证结果为密文数据对应的数据项完整,则在内存对密文数据进行读取或者写入;若所述完整性验证结果为密文数据对应的数据项不完整,则终止密文数据写入内存或者从内存中读出。

145.本技术实施例提供的内存控制器(具体可以是内存控制器中的内存加密引擎)可设置上述所述的数据加密装置,以实现本技术实施例提供的数据加密方法。在一些实施例中,本技术实施例提供的内存控制器可被配置为执行本技术实施例提供的数据加密方法。

146.本技术实施例还提供一种芯片,该芯片可以包括执行本技术实施例提供的数据加密方法的内存控制器。

147.本技术实施例还可提供一种电子设备,该电子设备可以包括上述所述的芯片。

148.虽然本技术实施例披露如上,但本技术并非限定于此。任何本领域技术人员,在不脱离本技术的精神和范围内,均可作各种更动与修改,因此本技术的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1