存储器存储装置和包括非易失性存储器的电子装置的制作方法

存储器存储装置和包括非易失性存储器的电子装置

1.相关申请的交叉引用

2.本技术要求于2020年8月11日在韩国知识产权局提交的韩国专利申请no.10-2020-0100407的优先权以及从其累积的全部权益,其全部内容通过引用并入本文。

技术领域

3.本公开涉及一种存储器存储装置和一种包括非易失性存储器的电子装置。更具体地,本公开涉及一种执行垃圾收集的存储器存储装置和电子装置。

背景技术:

4.半导体存储器装置包括易失性存储器装置和非易失性存储器装置。易失性存储器装置在断电时会丢失其存储的内容,但它们具有较高的读写速度。相反,由于非易失性存储器装置即使在断电时也保持其存储的内容,因此非易失性存储器装置用于存储无论是否被供电都需要维护的内容。

5.例如,易失性存储器装置包括静态ram(sram)、动态ram(dram)、同步dram(sdram)等。非易失性存储器装置即使断电也会保留其存储的内容。例如,非易失性存储器装置包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪存、相变ram(pram)、磁ram(mram)、电阻ram(rram)、铁电ram(fram)等。闪存可以被分类为nor闪存和nand闪存。

6.特别地,当与普通的eeprom相比时,闪存装置具有能够实现为例如高度集成的辅助大容量存储装置的优点。

7.使用闪存来生产各种存储器系统。存储器系统可以通过协议将数据存储到闪存中或从闪存读取数据。

8.闪存可以执行垃圾收集以确保空闲块。依据执行这种垃圾收集的时序,闪存的性能可能迅速劣化,因此需要一种控制该现象的方法。

技术实现要素:

9.本公开的各方面提供了一种能够通过预测执行垃圾收集的时间段来改善非易失性存储器的性能的电子装置。

10.本公开的各方面还提供了一种能够通过预测执行垃圾收集的时间段来改善非易失性存储器的性能的存储器存储装置。

11.然而,本公开的各方面不限于本文阐述的那些。通过参照下面给出的本公开的详细描述,本公开的以上和其他方面对于本公开所属领域的普通技术人员将变得更加明显。

12.其他实施例的具体细节包括在详细描述和附图中。

13.根据本公开的一方面,提供了一种电子装置,所述电子装置包括:非易失性存储器、存储器控制器、以及主机,所述存储器控制器被配置为控制所述非易失性存储器,所述主机连接到所述存储器控制器,其中,所述存储器控制器被配置为:响应于从所述主机接收

到的第一写入信号,向所述非易失性存储器提供所述第一写入信号,所述非易失性存储器被配置为:基于提供的所述第一写入信号来执行第一写入操作,基于执行所述第一写入操作的结果来生成第一元数据,并且向所述主机提供生成的所述第一元数据,所述主机被配置为:使用基于提供的所述第一元数据或所述第一写入信号被训练的神经网络模型,确定出是否执行所述非易失性存储器的垃圾收集,以及所述主机被配置为:响应于确定执行垃圾收集,向所述存储器控制器提供垃圾收集请求信号。

14.根据本公开的一方面,提供了一种存储器存储装置,所述存储器存储装置包括非易失性存储器以及存储器控制器,所述存储器控制器被配置为控制所述非易失性存储器,其中,所述存储器控制器被配置为向所述非易失性存储器提供第一写入命令、地址和数据,所述存储器控制器被配置为从所述非易失性存储器接收响应于所述第一写入命令生成的元数据,所述存储器控制器被配置为使用基于提供的所述第一元数据被训练的神经网络模型,确定出是否执行所述非易失性存储器的垃圾收集,以及所述存储器控制器被配置为响应于确定执行垃圾收集,向所述非易失性存储器提供第二写入命令、擦除命令和地址。

15.根据本公开的一方面,提供了一种电子装置,所述电子装置包括非易失性存储器、存储器控制器、以及主机,所述存储器控制器被配置为控制所述非易失性存储器,所述主机连接到所述存储器控制器,其中,所述存储器控制器被配置为:响应于从所述主机接收到的第一写入信号,向所述非易失性存储器提供所述第一写入信号,所述非易失性存储器被配置为:基于提供的所述第一写入信号来执行写入操作,基于执行所述写入操作的结果来生成元数据,并且向所述主机提供生成的所述元数据,所述元数据指示所述非易失性存储器中包括的空闲块的数量,以及所述主机被配置为响应于提供的所述元数据向所述存储器控制器提供垃圾收集请求信号。

附图说明

16.通过参照附图详细描述本公开的示例性实施例,本公开的上述和其他方面以及特征将变得更加明显,其中:

17.图1是示出根据一些实施例的电子装置的透视图。

18.图2是示出图1的存储器控制器的框图。

19.图3是示出图1的非易失性存储器的框图。

20.图4是示出根据一些实施例的非易失性存储器装置的示例性框图。

21.图5是示出根据一些实施例的存储单元阵列的示例性电路图。

22.图6是示意性地示出根据一些实施例的非易失性存储器的内部的示例性示图。

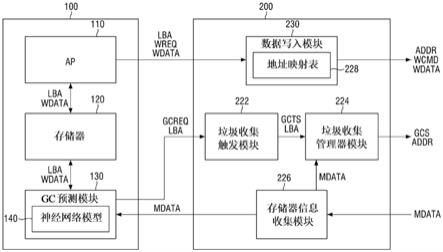

23.图7是示出根据一些实施例的电子装置的框图。

24.图8是示出图7的垃圾收集预测模块的框图。

25.图9是示出根据一些实施例的电子装置的垃圾收集预测操作的流程图。

26.图10是更详细地示出图9的垃圾收集预测操作的流程图。

27.图11至图14是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。

28.图15是示出根据一些实施例的电子装置中的垃圾收集操作的梯形图。

29.图16至图18是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。

30.图19是示出根据一些实施例的电子装置中的垃圾收集操作的梯形图。

31.图20和图21是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。

32.图22是示出根据一些实施例的电子装置的框图。

33.图23是示出图22的电子装置中的垃圾收集操作的梯形图。

34.图24是示出根据一些实施例的电子装置的框图。

35.图25是示出根据一些实施例的电子装置的框图。

具体实施方式

36.在下文中,将参照附图描述根据本公开的技术精神的实施例。

37.在下文中,将参照图1至图3描述包括主机100、存储器控制器200和非易失性存储器300的电子装置1。

38.图1是示出根据一些实施例的电子装置的透视图。图2是示出图1的存储器控制器的框图。图3是示出图1的非易失性存储器的框图。

39.参照图1,电子装置1可以包括主机100和存储器存储装置10。主机100和存储器存储装置10可以电连接。主机100可以向存储器存储装置10提供逻辑块地址lba和请求信号req,并且可以与存储器存储装置10交换数据data。例如,主机100可以连接到存储器控制器200。

40.主机100可以包括例如个人计算机(pc)、膝上型计算机、移动电话、智能电话、平板pc等。

41.存储器存储装置10可以包括存储器控制器200和非易失性存储器(nvm)300。存储器存储装置10可以被集成到一个半导体装置中。例如,存储器存储装置10可以包括嵌入式通用闪存(ufs)存储器装置、嵌入式多媒体卡(emmc)、固态硬盘(ssd)等。另外,例如,存储器存储装置10可以包括可移除ufs存储卡、紧凑型闪存(cf)卡、安全数字(sd)卡、微型sd卡、迷你sd卡、极限数字(xd)卡、记忆棒等。

42.非易失性存储器300可以包括nand闪存。然而,根据本公开的技术精神的实施例不限于此,并且非易失性存储器300可以包括nor闪存、或相变ram(pram)、磁阻ram(mram)、电阻存储器(诸如,铁电ram(feram)和电阻ram(rram))。

43.存储器控制器200可以连接到非易失性存储器300以控制非易失性存储器300。例如,响应于从主机100接收到的逻辑块地址lba、请求信号req等,存储器控制器200可以向非易失性存储器300提供地址addr、命令cmd、控制信号ctrl等。存储器控制器200可以向非易失性存储器300提供信号以控制向非易失性存储器300的数据写入或从非易失性存储器300的数据读取。另外,存储器控制器200和非易失性存储器300可以交换数据data。

44.参照图2,存储器控制器200可以包括处理器210、存储器211、主机接口(i/f)212、存储器接口213和工作存储器220。

45.处理器210可以包括中央处理单元(cpu)、控制器、专用集成电路(asic)等。处理器210可以控制存储器控制器200的整体操作。处理器210可以通过驱动加载在工作存储器220中的固件来控制存储器控制器200。

46.存储器211可以存储初始启动存储器存储装置10所需的代码数据。

47.存储器控制器200和主机100可以通过主机接口212连接。例如,可以通过主机接口212发送和接收数据data。主机接口212可以包括先进技术附件(ata)、串行ata(sata)、外部

sata(e-sata)、通用串行总线(usb)等。

48.存储器控制器200和非易失性存储器300可以通过存储器接口213连接。例如,可以通过存储器接口213来发送和接收数据data、控制信号ctrl、地址addr、命令cmd等。工作存储器220可以被实现为高速缓冲存储器、dram、sram、闪存等。

49.工作存储器220可以包括闪存转换层(ftl)。ftl可以包括管理非易失性存储器300的写入操作、读取操作和擦除操作等的系统软件。例如,可以在ftl中执行将逻辑地址转换为物理地址的处理。ftl可以包含固件。ftl可以被加载到工作存储器220中。ftl的固件可以由处理器210执行。

50.工作存储器220可以包括垃圾收集触发模块222、垃圾收集管理器模块224、存储器信息收集模块226和地址映射表228。“模块”可以实现为包括定制vlsi电路或门阵列、现成的(off-the-shelf)半导体(诸如逻辑芯片、晶体管或其他分立组件)的硬件电路。模块还可以以诸如现场可编程门阵列、可编程阵列逻辑、可编程逻辑器件等的可编程硬件设备来实现。模块还可以以由各种类型的处理器执行的软件来实现。

51.工作存储器220可以使用地址映射表228将逻辑块地址lba转换为地址addr,并将其提供给非易失性存储器300。工作存储器220可以对非易失性存储器300的存储单元执行管理。例如,工作存储器220可以对非易失性存储器300的存储单元阵列310的块执行垃圾收集和坏块管理操作。块可以对应于擦除的最小单位(例如,可以在同一擦除操作中一起擦除其存储单元的存储器区域,其中该区域的部分不被单独擦除)。

52.存储器控制器200可以使用垃圾收集触发模块222、垃圾收集管理器模块224等来控制非易失性存储器300的垃圾收集。例如,垃圾收集触发模块222可以响应于垃圾收集请求而向垃圾收集管理器模块224提供垃圾收集触发信号。例如,垃圾收集管理器模块224可以使用元数据等来控制非易失性存储器300的垃圾收集。

53.当数据连续写入闪存时,有效数据可能散布在整个非易失性存储器300中。空闲块是非易失性存储器300中没有存储有效数据的块。空闲块计数表示非易失性存储器300的空闲块的数量值(quantitative value)(例如,空闲块的数量)。垃圾收集是用于在非易失性存储器300中确保空闲块的处理。由于写入数据的单位是页,并且擦除数据的单位是块,因此需要用于调整单位的方法。因此,通过垃圾收集,将有效页的数据写入另一个块,并擦除包括该有效页的块,从而确保空闲块。垃圾收集可以提高存储器存储装置10的性能。

54.参照图3,非易失性存储器300可以包括存储单元阵列310、地址译码器320、电压发生器330、读/写电路340、控制逻辑350等。

55.存储单元阵列310可以通过字线wl连接到地址译码器320。存储单元阵列310可以通过位线bl连接到读/写电路340。存储单元阵列310可以包括多个存储单元。例如,沿行方向布置的存储单元可以连接到字线wl。例如,沿列方向布置的存储单元可以连接到位线bl。

56.地址译码器320可以通过字线wl连接到存储单元阵列310。地址译码器320可以在控制逻辑350的控制下操作。地址译码器320可以从存储器控制器200接收地址addr。地址译码器320可以从电压发生器330接收诸如编程或读取的操作所需的电压。

57.地址译码器320可以对接收到的地址addr之中的行地址进行译码。地址译码器320可以使用译码的行地址来选择字线wl。译码的列地址dca可以被提供给读/写电路340。例如,地址译码器320可以包括行译码器、列译码器、地址缓冲器等。

58.电压发生器330可以在控制逻辑350的控制下生成存取操作所需的电压。例如,电压发生器330可以生成执行编程操作所需的编程电压和编程验证电压。例如,电压发生器330可以生成执行读取操作所需的读取电压,以及生成执行擦除操作所需的擦除电压和擦除验证电压。另外,电压发生器330可以将执行每个操作所需的电压提供给地址译码器320。

59.读/写电路340可以通过位线bl连接到存储单元阵列310。读/写电路340可以与存储器控制器200交换数据data。读/写电路340可以在控制逻辑350的控制下操作。读/写电路340可以从地址译码器320接收译码的列地址dca。读/写电路340可以使用译码的列地址dca选择位线bl。

60.例如,读/写电路340可以将接收到的数据data编程到存储单元阵列310中。读/写电路340可以从存储单元阵列310读取数据,并将读取的数据提供给外部(例如,存储器控制器200)。例如,读/写电路340可以包括诸如感测放大器、写入驱动器、列选择电路、页面缓冲器等组件。

61.控制逻辑350可以连接到地址译码器320、电压发生器330和读/写电路340。控制逻辑350可以控制非易失性存储器300的操作。控制逻辑350响应于从存储器控制器200提供的控制信号crtl和命令cmd(例如,写入命令和读取命令)进行操作。控制逻辑350可以在存储器控制器200的控制下执行存储单元阵列310的垃圾收集。

62.图4是示出根据一些实施例的非易失性存储器装置的示例性框图。

63.参照图3和图4,根据一些实施例的非易失性存储器300可以包括多个半导体层la1至lan。多个半导体层la1至lan均可以是存储器芯片(例如,dram存储器芯片)。可选择地,多个半导体层la1至lan中的一些半导体层可以是执行与外部装置(例如,图1的主机100)接口通信的主芯片,而其余的半导体层可以是存储数据的从芯片。

64.例如,非易失性存储器300的第n层lan和第一层la1可以是包括存储单元阵列310的半导体芯片。多个半导体层la1至lan可以通过硅通路tsv在彼此之间发送和接收信号。根据一些实施例的非易失性存储器300的配置和布置不限于此。

65.图5是示出根据一些实施例的存储单元阵列的示例性电路图。

66.参照图5,多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33可以沿第一方向x和第二方向y布置在衬底(未示出)上。多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33可以具有沿第三方向z延伸的形状。多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33可以共同连接到形成在衬底上(或未示出)或形成在衬底中的公共源极线csl。公共源极线csl被示出为连接到多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33在第三方向z上的最下端。然而,将公共源极线csl电连接到多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33在第三方向z上的最下端是足够的,并且公共源极线csl不限于物理地位于多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33的下端。另外,在该图中,多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23、ns33示出为以3

×

3的阵列布置,但是布置在非易失性存储器的存储单元阵列310中的多个单元串的布置形状和数量不限于此。

67.单元串ns11、ns12和ns13可以连接到第一接地选择线gsl1。单元串ns21、ns22和ns23可以连接到第二接地选择线gsl2。单元串ns31、ns32和ns33可以连接到第三接地选择线gsl3。

68.另外,单元串ns11、ns12和ns13可以连接到第一串选择线ssl1。单元串ns21、ns22和ns23可以连接到第二串选择线ssl2。单元串ns31、ns32和ns33可以连接到第三串选择线ssl3。

69.多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33中的每个单元串可以包括连接到每条串选择线的串选择晶体管sst。另外,多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33中的每个单元串可以包括连接到每条接地选择线的接地选择晶体管gst。

70.多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33中的每个单元串中的接地选择晶体管的一端可以连接到公共源极线csl。另外,多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33均可以具有沿第三方向z顺序地堆叠在接地选择晶体管与串选择晶体管之间的多个存储单元。尽管未在图中示出,但是多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33均可以包括位于接地选择晶体管与串选择晶体管之间的虚设单元。另外,每个串中包括的串选择晶体管的数量不限于该图。

71.例如,单元串ns11可以包括:接地选择晶体管gst11、多个存储单元m11_1至m11_8、以及串选择晶体管sst11,接地选择晶体管gst11设置在第三方向z上的最下端;多个存储单元m11_1至m11_8沿第三方向z顺序地堆叠在接地选择晶体管gst11上;串选择晶体管sst11堆叠在第三方向z上的最上面的存储单元m11_8上。另外,单元串ns21可以包括:接地选择晶体管gst21、多个存储单元m21_1至m21_8、以及串选择晶体管sst21,接地选择晶体管gst21设置在第三方向z上的最下端;多个存储单元m21_1至m21_8沿第三方向z顺序地堆叠在接地选择晶体管gst21上;串选择晶体管sst21堆叠在第三方向z上的最上面的存储单元m21_8上。另外,单元串ns31可以包括:接地选择晶体管gst31、多个存储单元m31_1至m31_8、以及串选择晶体管sst31,接地选择晶体管gst31设置在第三方向z上的最下端;多个存储单元m31_1至m31_8沿第三方向z顺序地堆叠在接地选择晶体管gst31上;串选择晶体管sst31堆叠在第三方向z上的最上面的存储单元m31_8上。其他串的配置也可以与此类似。

72.可以通过每条字线共同电连接位于在第三方向z上距衬底(未示出)或接地选择晶体管相同高度的存储单元。例如,在与存储单元m11_1、m21_1和m31_1相同的高度处形成的存储单元可以连接到第一字线wl1。另外,在与存储单元m11_2、m21_2和m31_2相同的高度处形成的存储单元可以连接到第二字线wl2。在下文中,由于连接到第三字线wl3至第八字线wl8的存储单元的布置和结构与以上相似,因此将省略其描述。

73.多个单元串ns11、ns21、ns31、ns12、ns22、ns32、ns13、ns23和ns33的每个串选择晶体管的一端可以连接到位线bl1、bl2或bl3。例如,串选择晶体管sst11、sst21和sst31可以连接到沿第二方向y延伸的位线bl1。连接到位线bl2或bl3的其他串选择晶体管的描述也与上述相似,因此将省略其描述。

74.与一条串(或接地)选择线和一条字线相对应的存储单元可以形成一页。可以以页面为单位执行写入操作和读取操作。每个页面中的每个存储单元可以存储两位或更多位。写入每个页面的存储单元的位可以形成逻辑页面。

75.存储单元阵列310可以被设置为三维存储阵列。三维存储阵列可以单片形成在具有布置在衬底(未示出)上的有源区域和涉及存储单元的操作的电路的存储单元的阵列的一个或更多个物理层级(level)上。涉及存储单元的操作的电路可以位于衬底内或位于衬

底上。单片形成是指三维阵列的每个层级的层可以直接沉积在三维阵列的较低层级的层上。可选择地,涉及存储单元的操作的电路可以连接到第三方向z上的最上端的接触部分。将参照图6对此进行详细描述。

76.图6是示意性地示出根据一些实施例的非易失性存储器的内部的示例性示图。

77.参照图6,根据一些实施例的非易失性存储器300可以具有芯片对芯片(c2c)结构。在该图中,非易失性存储器300的单元区域cell可以对应于图5的存储单元阵列310。

78.c2c结构可以包括通过以下操作获得的结构:在第一晶片上制造包括单元区域cell的上芯片;在不同于第一晶片的第二晶片上制造包括外围电路区域peri的下芯片;以及通过接合(bonding)方法将上芯片和下芯片彼此连接。在一个示例中,接合方法可以包括将形成在上芯片的最上面的金属层上的接合金属电连接到形成在下芯片的最上面的金属层上的接合金属的方法。例如,当接合金属由铜(cu)形成时,接合方法可以是cu-cu接合方法,并且接合金属还可以由铝或钨形成。

79.根据一些实施例的非易失性存储器300的外围电路区域peri和单元区域cell均可以包括外部焊盘接合区域pa、字线接合区域wlba和位线接合区域blba。

80.外围电路区域peri可以包括第一衬底1210、层间绝缘层1215、形成在第一衬底1210上的多个电路元件1220a、1220b和1220c、分别连接到多个电路元件1220a、1220b和1220c的第一金属层1230a、1230b和1230c、形成在第一金属层1230a、1230b和1230c上的第二金属层1240a、1240b和1240c。在一个实施例中,第一金属层1230a、1230b和1230c可以由具有相对高电阻的钨形成,并且第二金属层1240a、1240b和1240c可以由具有相对低电阻的铜形成。

81.在本公开中,仅示出和描述了第一金属层1230a、1230b和1230c以及第二金属层1240a、1240b和1240c,但是本公开不限于此,并且还可以在第二金属层1240a、1240b和1240c上形成一个或更多个金属层。形成在第二金属层1240a、1240b和1240c上的一个或更多个金属层中的至少一些可以由电阻低于形成第二金属层1240a、1240b和1240c的铜的电阻的铝等形成。

82.层间绝缘层1215可以设置在第一衬底1210上以覆盖多个电路元件1220a、1220b和1220c、第一金属层1230a、1230b和1230c以及第二金属层1240a、1240b和1240c,并且可以包括诸如氧化硅或氮化硅的绝缘材料。

83.下接合金属1271b和1272b可以在字线接合区域wlba中形成在第二金属层1240b上。在字线接合区域wlba中,外围电路区域peri的下接合金属1271b和1272b可以通过接合方法电连接到单元区域cell的上接合金属1371b和1372b。下接合金属1271b和1272b以及上接合金属1371b和1372b可以由铝、铜、钨等形成。

84.单元区域cell可以提供至少一个存储块。单元区域cell可以包括第二衬底1310和公共源极线1320(对应于图5的csl)。在第二衬底1310上,多条字线1330(1331至1338,对应于图5的wl1至wl8)可以沿着垂直于第二衬底1310的顶表面的第三方向z堆叠。串选择线和接地选择线可以分别设置在字线1330的上方和下方,并且多条字线1330可以设置在串选择线与接地选择线之间。

85.在位线接合区域blba中,沟道结构ch可以沿垂直于第二衬底1310的顶表面的方向延伸,以穿透字线1330、串选择线和接地选择线。沟道结构ch可以包括数据存储层、沟道层、

掩埋绝缘层等。沟道层可以电连接到第一金属层1350c和第二金属层1360c。例如,第一金属层1350c可以是位线接触,并且第二金属层1360c可以是位线(对应于图5的bl1至bl3)。在一个实施例中,位线1360c可以沿着平行于第二衬底1310的顶表面的第二方向y延伸。

86.在图6所示的一个实施例中,其中设置有沟道结构ch和位线1360c的区域可以被定义为位线接合区域blba。在位线接合区域blba中,位线1360c可以电连接到在外围电路区域peri中提供页面缓冲器1393的电路元件1220c。作为一个示例,位线1360c可以连接到单元区域cell中的上接合金属1371c和1372c,并且上接合金属1371c和1372c可以连接到与页面缓冲器1393的电路元件1220c连接的下接合金属1271c和1272c。

87.在字线接合区域wlba中,字线1330可以沿着平行于第二衬底1310的顶表面的第一方向x延伸,并且可以连接到多个单元接触塞1340(1341至1347)。字线1330和单元接触塞1340可以在由沿着第一方向x以不同长度延伸的至少一些字线1330提供的焊盘中彼此连接。第一金属层1350b和第二金属层1360b可以顺序地连接到与字线1330连接的单元接触塞1340的顶部。在字线接合区域wlba中,单元接触塞1340可以通过单元区域cell的上接合金属1371b和1372b以及外围电路区域peri的下接合金属1271b和1272b连接到外围电路区域peri。

88.单元接触塞1340可以电连接到在外围电路区域peri中提供行译码器1394的电路元件1220b。在一个实施例中,提供行译码器1394的电路元件1220b的工作电压可以不同于提供页面缓冲器1393的电路元件1220c的工作电压。作为一个示例,提供页面缓冲器1393的电路元件1220c的工作电压可以大于提供行译码器1394的电路元件1220b的工作电压。

89.公共源极线接触塞1380可以设置在外部焊盘接合区域pa中。公共源极线接触塞1380可以由诸如金属、金属化合物或多晶硅的导电材料形成,并且可以电连接到公共源极线1320。第一金属层1350a和第二金属层1360a可以顺序地堆叠在公共源极线接触塞1380上。作为一个示例,其中设置有公共源极线接触塞1380、第一金属层1350a和第二金属层1360a的区域可以被定义为外部焊盘接合区域pa。

90.同时,输入/输出焊盘1205和1305可以设置在外部焊盘接合区域pa中。参照图6,在第一衬底1210下方,可以形成下绝缘层1201以覆盖第一衬底1210的底表面,并且第一输入/输出焊盘1205可以形成在下绝缘层1201上。第一输入/输出焊盘1205可以通过第一输入/输出接触塞1203连接到设置在外围电路区域peri中的多个电路元件1220a、1220b和1220c中的至少一个,并且可以通过下绝缘层1201与第一衬底1210分开。另外,侧绝缘层可以设置在第一输入/输出接触塞1203与第一衬底1210之间,以将第一输入/输出接触塞1203与第一衬底1210电分开。

91.继续参照图6,上绝缘层1301可以形成在第二衬底1310上以覆盖第二衬底1310的顶表面,并且第二输入/输出焊盘1305可以设置在上绝缘层1301上。第二输入/输出焊盘1305可以通过第二输入/输出接触塞1303连接到设置在外围电路区域peri中的多个电路元件1220a、1220b和1220c中的至少一个。

92.根据实施例,第二衬底1310、公共源极线1320等可以不设置在设置有第二输入/输出接触塞1303的区域中。另外,第二输入/输出焊盘1305在第三方向z上可以不与字线1330交叠。参照图6,第二输入/输出接触塞1303可以在与第二衬底1310的顶表面平行的方向上与第二衬底1310分开,并且可以穿透单元区域cell的层间绝缘层1315以连接到第二输入/

输出焊盘1305。

93.根据实施例,可以选择性地形成第一输入/输出焊盘1205和第二输入/输出焊盘1305。例如,根据一些实施例的非易失性存储器300可以仅包括设置在第一衬底1210下方的第一输入/输出焊盘1205,或者仅包括设置在第二衬底1310上方的第二输入/输出焊盘1305。可选择地,非易失性存储器300可以包括第一输入/输出焊盘1205和第二输入/输出焊盘1305两者。

94.在单元区域cell和外围电路区域peri中的每一者中包括的外部焊盘接合区域pa和位线接合区域blba中的每一者中,最上面的金属层可以具有作为虚设图案存在的金属图案,或者可以是空的。

95.在根据一些实施例的非易失性存储器300的外部焊盘接合区域pa中,对应于形成在单元区域cell的最上面的金属层上的上金属图案1372a,具有与单元区域cell的上金属图案1372a相同形状的下金属图案1273a可以形成在外围电路区域peri的最上面的金属层中。形成在外围电路区域peri的最上面的金属层上的下金属图案1273a可以不连接到外围电路区域peri中的单独的接触。上金属图案1372a可以通过接合方法电连接到上接合金属1371a。上接合金属1371a可以电连接到第二金属层1360a。

96.类似地,在外部焊盘接合区域pa中,对应于形成在外围电路区域peri的最上面的金属层上的下金属图案1272a,具有与外围电路区域peri的下金属图案1272a相同形状的上金属图案1373a可以形成在单元区域cell的最上面的金属层中。上金属图案1373a可以电连接到第二输入/输出接触塞1303。下接合金属1271a可以通过接合方法电连接到下金属图案1272a。下接合金属1271a可以在外部焊盘接合区域pa中电连接到第一金属层。

97.下接合金属1271b和1272b可以形成在字线接合区域wlba中的第二金属层1240b上。在字线接合区域wlba中,外围电路区域peri的下接合金属1271b和1272b可以通过接合方法电连接到单元区域cell的上接合金属1371b和1372b。

98.另外,在位线接合区域blba中,对应于形成在外围电路区域peri的最上面的金属层中的下金属图案1252,具有与外围电路区域peri的下金属图案1252相同形状的上金属图案1392可以形成在单元区域cell的最上面的金属层中。在形成在单元区域cell的最上面的金属层中的上金属图案1392上可以不形成接触。下金属图案1252可以具有接触1251,以连接到电路元件1220c。

99.在下文中,将参照图7和图8描述包括垃圾收集预测模块130的电子装置1。

100.图7是示出根据一些实施例的电子装置的框图。图8是示出图7的垃圾收集预测模块的框图。

101.参照图7,主机100可以包括应用处理器110、存储器120和垃圾收集(gc)预测模块130。然而,根据本公开的技术精神的实施例不限于此,并且可以省略一些配置。

102.应用处理器110可以控制主机100的整体操作。例如,应用处理器110可以接收逻辑块地址lba和存储在存储器120中的写入数据wdata。应用处理器110可以将逻辑块地址lba和写入数据wdata与写入请求信号wreq一起发送到存储器控制器200。该操作可以由应用处理器110计算和执行。

103.存储器120可以存储要在应用处理器110和垃圾收集预测模块130中使用的数据。存储器120可以接收数据以临时存储它,并且当需要该数据时将该数据发送到应用处理器

110和垃圾收集预测模块130。另外,存储器120可以从应用处理器110和垃圾收集预测模块130接收并存储数据。

104.垃圾收集预测模块130可以从存储器120或应用处理器110接收逻辑块地址lba和写入数据wdata。此外,垃圾收集预测模块130可以从存储器控制器200接收元数据mdata。

105.垃圾收集预测模块130可以使用接收到的逻辑块地址lba、写入数据wdata和元数据mdata中的至少一个来训练神经网络模型140。垃圾收集预测模块130可以基于经训练的神经网络模型140向存储器控制器200提供垃圾收集请求信号gcreq、逻辑块地址lba等。稍后将描述垃圾收集预测模块130的更详细描述。

106.存储器控制器200可以包括数据写入模块230、垃圾收集触发模块222、垃圾收集管理器模块224和存储器信息收集模块226。

107.数据写入模块230可以包括地址映射表228。数据写入模块230可以从应用处理器110接收逻辑块地址lba、写入数据wdata和写入请求信号wreq。响应于写入请求信号wreq,数据写入模块230可以控制非易失性存储器300将写入数据wdata写入非易失性存储器300。

108.例如,数据写入模块230可以基于地址映射表228将逻辑块地址lba转换为地址addr。这里,地址addr可以是物理块地址。地址映射表228可以在存储器控制器200的控制下改变。

109.数据写入模块230可以将地址addr、写入命令wcmd和写入数据wdata提供给非易失性存储器300。响应于写入命令wcmd,非易失性存储器300可以将写入数据wdata写入到存储单元阵列310的与地址addr相对应的块。然而,根据本公开的技术精神的实施例不限于此,并且非易失性存储器300可以执行读取操作或擦除操作。

110.垃圾收集触发模块222可以从主机100接收垃圾收集请求信号gcreq,并控制存储器控制器200以便执行垃圾收集。例如,垃圾收集触发模块222可以从垃圾收集预测模块130接收垃圾收集请求信号gcreq和逻辑块地址lba。

111.响应于垃圾收集请求信号gcreq,垃圾收集触发模块222可以将垃圾收集触发信号gcts和逻辑块地址lba提供给垃圾收集管理器模块224。例如,可以通过垃圾收集触发模块222的操作来执行垃圾收集。如果垃圾收集触发模块222没有将垃圾收集触发信号gcts发送到垃圾收集管理器模块224,则可以不执行存储器存储装置10的垃圾收集。

112.垃圾收集管理器模块224可以从垃圾收集触发模块222接收垃圾收集触发信号gcts,并且响应于此,可以控制非易失性存储器300执行垃圾收集。

113.例如,垃圾收集管理器模块224可以将与逻辑块地址lba相对应的地址addr发送到非易失性存储器300,并且发送垃圾收集信号gcs。这里,垃圾收集信号gcs可以包括写入命令和擦除命令,但是根据本公开的技术精神的实施例不限于此。

114.可以通过垃圾收集管理器模块224执行非易失性存储器300的垃圾收集。例如,可以将与地址addr相对应的块的有效页的数据复制到另一块。另外,可以擦除与地址addr相对应的块。与地址addr相对应的块可以变为空闲块,因此,可以提高存储器存储装置10的性能。

115.这里,垃圾收集管理器模块224可以从存储器信息收集模块226接收元数据mdata。垃圾收集管理器模块224可以允许使用提供的元数据mdata以小的垃圾收集成本来执行垃圾收集。

116.存储器信息收集模块226可以从非易失性存储器300接收和收集元数据mdata。这里,元数据mdata可以包括ftl元数据。

117.更详细地,元数据mdata可以指示非易失性存储器300中的空闲块的数量、更新块的可写入页面信息、有效页面的数量、所有块的擦除的数量、管理页面映射的块的有效页面的数量等。然而,根据本公开的技术精神的实施例不限于此,并且元数据mdata还可以包括关于在执行写入操作之后的非易失性存储器300的信息。

118.元数据mdata可以包括关于在通过写入命令wcmd在非易失性存储器300中执行写入操作之后的非易失性存储器300的信息。例如,假定在执行写入操作之前包括在非易失性存储器300中的空闲块的数量是100,并且在执行写入操作之后包括在非易失性存储器300中的空闲块的数量是50,则元数据mdata可以包括记录了空闲块的数量已从100改变为50的数据。

119.存储器信息收集模块226可以将元数据mdata提供给垃圾收集管理器模块224和主机100。这里,元数据mdata可以由存储器控制器200处理,然后提供给主机100。

120.存储器信息收集模块226可以将元数据mdata提供给垃圾收集预测模块130。然后,垃圾收集预测模块130可以接收作为用于非易失性存储器300的数据的元数据mdata,并训练神经网络模型140以预测何时应该执行垃圾收集。

121.参照图8,垃圾收集预测模块130可以包括神经网络模型140和比较器132。然而,根据本公开的技术精神的实施例不限于此,并且可以包括其他配置。

122.神经网络模型140可以接收元数据mdata、逻辑块地址lba、写入数据wdata等。可以基于接收到的元数据mdata、逻辑块地址lba、写入数据wdata等来训练神经网络模型140。在此,神经网络模型140的训练方法可以包括深度学习、机器学习等。

123.垃圾收集预测模块130可以使用经训练的神经网络模型140输出垃圾收集预测值。比较器132可以接收垃圾收集预测值,并将其与参考值ref_val进行比较。比较器132可以基于比较结果输出垃圾收集请求信号gcreq。例如,当比较结果不满足标准时,比较器132可以不输出垃圾收集请求信号gcreq。

124.在下文中,将参照图7至图10描述垃圾收集预测操作。

125.图9是示出根据一些实施例的电子装置的垃圾收集预测操作的流程图。图10是更详细地示出图9的垃圾收集预测操作的流程图。

126.参照图7和图9,存储器存储装置10可以执行写入操作(步骤s400)。例如,地址addr、写入命令wcmd和写入数据wdata可以从存储器控制器200发送到非易失性存储器300,并且写入数据wdata可以被写到非易失性存储器300。

127.这里,存储器存储装置10的写入操作可以被执行多次而不是一次。例如,存储器存储装置10的写入操作不限于一次,并且可以针对相同的地址addr执行多次。

128.主机100的存储器120可以存储主机数据(步骤s401)。例如,主机100的存储器120可以从应用处理器110接收并存储逻辑块地址lba、写入数据wdata等。此外,存储器120可以将所存储的逻辑块地址lba、写入数据wdata等提供给垃圾收集预测模块130。例如,垃圾收集预测模块130可以接收已经在写入操作中使用的逻辑块地址lba、写入数据wdata等。

129.存储器控制器200的存储器信息收集模块226可以从非易失性存储器300接收元数据mdata(步骤s402)。另外,主机100的垃圾收集预测模块130可以从存储器信息收集模块

226接收元数据mdata并进行存储(步骤s403)。

130.垃圾收集预测模块130可以使用利用所存储的数据训练的神经网络模型140执行垃圾收集预测(步骤s404)。垃圾收集预测模块130可以使用接收到的逻辑块地址lba、写入数据wdata、元数据mdata等来训练神经网络模型140。例如,垃圾收集预测模块130可以在多个写入操作中的每个写入操作被执行之后使用用于非易失性存储器300的元数据mdata来训练神经网络模型140。

131.垃圾收集预测模块130可以确定出是否使用经训练的神经网络模型140预测到垃圾收集(步骤s405)。如果没有预测到垃圾收集(步骤s405中为“否”),则可以重复步骤s400至s405。如果预测到垃圾收集(步骤s405中为“是”),则可以执行垃圾收集(步骤s406)。例如,垃圾收集预测模块130可以将垃圾收集请求信号gcreq发送到垃圾收集触发模块222,从而执行垃圾收集。

132.对于垃圾收集预测模块130的更详细的垃圾收集预测操作,参见图10。在图10中,假设仅使用元数据mdata中包括的信息的空闲块计数fbc。然而,根据本公开的技术精神的实施例不限于此。

133.参照图10,垃圾收集预测模块130可以预测非易失性存储器300的空闲块计数(步骤s407)。例如,垃圾收集预测模块130可以在当前时间段tn预测在针对非易失性存储器300执行/运行写入操作的未来时间段t

n+1

的非易失性存储器的空闲块计数。当前时间段tn发生在过去时间段t

n-1

之后,在该过去时间段t

n-1

中已经针对非易失性存储器300执行/运行了一个或更多个写入操作。具体地,垃圾收集预测模块130可以使用先前写入操作产生的空闲块计数来训练神经网络模型,并使用经训练的神经网络模型预测后续写入操作之后的空闲块计数。例如,垃圾收集预测模块130可以输出预测的空闲块计数。

134.垃圾收集预测模块130可以确定出预测的空闲块计数是否小于参考值ref_val(步骤s408)。

135.例如,如果预测的空闲块计数不小于参考值ref_val(步骤s408为“否”),则垃圾收集预测操作可以终止。垃圾收集预测模块130可以不将垃圾收集请求信号gcreq提供给存储器控制器200。

136.例如,如果预测的空闲块计数小于参考值ref_val(步骤s408中为“是”),则垃圾收集预测模块130可以将垃圾收集请求信号gcreq提供给存储器控制器200。因此,存储器存储装置10可以执行垃圾收集。例如,即使尚未满足垃圾收集条件,当满足了预测的垃圾收集条件时,也可以执行存储器存储装置10的垃圾收集。因此,可以减少由存储器存储装置10的垃圾收集引起的负载,并且可以改善存储器存储装置10的性能。

137.图11至图14是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。这里,假设垃圾收集预测模块130使用元数据mdata中的非易失性存储器300的空闲块计数fbc。

138.参照图11,非易失性存储器300的空闲块计数fbc可以随着时间变化。例如,在时间t-3执行了写入操作之后,非易失性存储器300的空闲块计数fbc可以是100。例如,在时间t-2执行了写入操作之后,非易失性存储器300的空闲块计数fbc可以为70。例如,在时间t-1执行了写入操作之后,非易失性存储器300的空闲块计数fbc可以是40。

139.每个时间段中的非易失性存储器300的空闲块计数fbc可以是从非易失性存储器

300提供的元数据mdata或可以被包括在从非易失性存储器300提供的元数据mdata中。此外,用于执行垃圾收集的空闲块计数fbc的标准可以是小于20。例如,当非易失性存储器300的空闲块计数fbc为20或更大时,不执行垃圾收集,并且当非易失性存储器300的空闲块计数fbc小于20时,可以执行垃圾收集。

140.参照图12,神经网络模型140可以包括输入层141、隐藏层142和143以及输出层144。神经网络模型140可以基于接收到的输入数据i1和i2执行计算,并基于计算结果生成输出数据o1和o2。

141.可以通过基于输入数据i1和i2执行计算来训练神经网络模型140。在这种情况下,用于训练神经网络模型140的输入数据i1和i2可以是训练数据。

142.神经网络模型140可以是包括两个或更多个隐藏层的深度神经网络。神经网络模型140可以包括卷积神经网络(cnn)、递归神经网络(rnn)、深度信念网络、限制玻尔兹曼机等。

143.神经网络模型140中包括的层141、142、143和144中的每一层可以包括多个神经元。神经元可以对应于多个人工节点。例如,输入层141可以包括两个神经元,并且隐藏层142和143中的每一层可以包括三个神经元。然而,根据本公开的技术精神的实施例不限于此,并且神经网络模型140中包括的每一层可以包括各种数量的神经元。

144.神经网络模型140中包括的神经元可以彼此连接并交换数据。一个神经元可以从其他神经元接收数据并进行计算,并且将计算结果输出到其他神经元。

145.每个神经元的输入和输出可以是输入激活和输出激活。例如,激活可以是不仅对应于一个神经元的输出而且对应于下一层中包括的神经元的输入的参数。同时,每个神经元可以基于从先前层中包括的神经元接收的激活和权重,来确定其自身的激活。权重是用于计算每个神经元中的输出激活的参数,并且可以是分配给神经元之间的连接关系的值。

146.在神经网络模型140中,许多数据集在多个相互连接的神经元之间进行交换,并且在穿过层时经历了许多计算过程。同时,通过这样的计算过程来训练神经网络模型140,并且可以基于其来优化权重和偏差。

147.再次参照图11至图14,每个时间段中的非易失性存储器300的空闲块计数fbc可以是神经网络模型140的输入。参照图13,可以在时间t-3、t-2和t-1将非易失性存储器300的空闲块计数fbc输入到神经网络模型140。可以使用相应的输入来训练神经网络模型140,并且因此,垃圾收集预测模块130可以输出非易失性存储器300的空闲块计数fbc被预测为10的结果。

148.参照图14,非易失性存储器300的空闲块计数fbc在时间t-3为100,在时间t-2为70,在时间t-1为40。

149.使用这样的数据训练神经网络模型140,结果,垃圾收集预测模块130可以输出非易失性存储器300的空闲块计数fbc在时间t为10的结果。

150.例如,当执行下一次写入操作时非易失性存储器300的空闲块计数fbc的预测值可以是10。因此,垃圾收集预测模块130可以通过比较器132将参考值ref_val 20与预测值10进行比较。由于预测值小于参考值ref_val,因此垃圾收集预测模块130可以将垃圾收集请求信号gcreq提供给存储器控制器200,以便执行垃圾收集。

151.在上面,已经使用非易失性存储器300的空闲块计数fbc描述了根据本公开的技术

精神的实施例,但是实施例不限于此。

152.通过垃圾收集预测模块130的经训练的神经网络模型140,可以在不满足垃圾收集性能标准的时间段执行垃圾收集。例如,通过预测垃圾收集被执行的时间段,可以减少由垃圾收集引起的负载,并且可以进一步提高存储器存储装置10的性能。

153.图15是示出根据一些实施例的电子装置中的垃圾收集操作的梯形图。

154.参照图15,主机100可以将逻辑块地址lba、写入请求信号wreq和第一写入数据wdata1提供给存储器控制器200(步骤s410)。存储器控制器200可以响应于写入请求信号wreq执行程序(步骤s411)。存储器控制器200可以将地址addr、写入命令wcmd和第一写入数据wdata1提供给非易失性存储器300(步骤s412)。非易失性存储器300可以响应于从存储器控制器200提供的写入命令wcmd来写入第一写入数据wdata1(步骤s413)。

155.在第一写入数据wdata1写入非易失性存储器300的存储单元阵列310之后,非易失性存储器300可以将第一元数据mdata1提供给主机100(步骤s414)。例如,非易失性存储器300可以将第一元数据mdata1提供给存储器控制器200的存储器信息收集模块226。存储器控制器200的存储器信息收集模块226可以将接收到的第一元数据mdata1提供给主机100。

156.主机100可以存储逻辑块地址lba、第一写入数据wdata1或第一元数据mdata1中的至少一个(步骤s415)。另外,主机100可以使用神经网络模型140执行垃圾收集预测(步骤s416)。例如,可以使用逻辑块地址lba、第一写入数据wdata1或第一元数据mdata1中的至少一个来训练神经网络模型140。主机100的垃圾收集预测模块130可以使用经训练的神经网络模型140输出预测值。垃圾收集预测模块130可以将预测值与参考值进行比较,如果满足该标准,则将垃圾收集请求信号gcreq和逻辑块地址lba提供给存储器控制器200(步骤s417)。

157.存储器控制器200可以响应于垃圾收集请求信号gcreq执行垃圾收集(步骤s418)。例如,垃圾收集管理器模块224可以通过垃圾收集触发模块222执行非易失性存储器300的垃圾收集。因此,存储器控制器200可以将地址addr、写入命令wcmd和擦除命令ecmd提供给非易失性存储器300(步骤s419)。

158.响应于接收到的写入命令wcmd和擦除命令ecmd,非易失性存储器300可以复制和擦除与地址addr相对应的块的有效页,从而执行垃圾收集(步骤s420)。

159.在非易失性存储器300的垃圾收集被执行之后并且经过了特定时间段,主机100可以将逻辑块地址lba、写入请求信号wreq和第二写入数据wdata2提供给存储器控制器200(步骤s421)。在此,特定时间段对应于垃圾收集被执行之后的时间段,并且不必须是规则(regular)的时间段。另外,第二写入数据wdata2可以不同于第一写入数据wdata1。

160.存储器控制器200可以响应于接收到的写入请求信号wreq执行程序(步骤s422)。因此,存储器控制器200可以将地址addr、写入命令wcmd和第二写入数据wdata2提供给非易失性存储器300(步骤s423)。

161.非易失性存储器300可以响应于写入命令wcmd来写入第二写入数据wdata2(步骤s424)。

162.这里,在第一写入数据wdata1写入到非易失性存储器300之后,垃圾收集被执行以生成空闲块,并且第二写入数据wdata2可以写入到新生成的空闲块。因此,可以减少在第二写入数据wdata2被写入之后执行垃圾收集时产生的负载,从而可以提高存储器存储装置10

的整体性能。

163.在下文中,将参照图16至图18描述使用利用逻辑块地址累计计数lba_ac训练的神经网络模型140的垃圾收集预测操作。

164.图16至图18是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。这里,假定垃圾收集预测模块130使用逻辑块地址累计计数lba_ac。

165.参照图16,主机100提供的逻辑块地址累计计数lba_ac可以随着时间变化。例如,在执行了写入操作之后,逻辑块地址累计计数lba_ac在时间t-3可以为0。例如,在执行了写入操作之后,逻辑块地址累计计数lba_ac在时间t-2可以为30。例如,在执行了写入操作之后,逻辑块地址累计计数lba_ac在时间t-1可以为60。

166.每个时间段中的逻辑块地址累计计数lba_ac可以是从逻辑块地址lba和写入数据wdata推导出的数据。另外,用于执行垃圾收集的逻辑块地址累计计数lba_ac的标准可以是大于80。例如,当逻辑块地址累计计数lba_ac为80或小于80时,可以不执行垃圾收集,当逻辑块地址累计计数lba_ac大于80时,可以执行垃圾收集。

167.每个时间段中的逻辑块地址累计计数lba_ac可以是神经网络模型140的输入。参照图17,时间t-3、t-2和t-1处的逻辑块地址累计计数lba_ac可以输入到神经网络模型140。可以使用相应的输入来训练神经网络模型140,并且因此,垃圾收集预测模块130可以输出非易失性存储器300的逻辑块地址累计计数lba_ac被预测为90的结果。

168.参照图18,逻辑块地址累计计数lba_ac在时间t-3为0,在时间t-2为30,在时间t-1为60。

169.使用这样的数据来训练神经网络模型140,结果,垃圾收集预测模块130可以输出逻辑块地址累计计数lba_ac在时间t为90的结果。

170.例如,当执行下一次写入操作时,逻辑块地址累计计数lba_ac的预测值可以是90。因此,垃圾收集预测模块130可以通过比较器132将参考值ref_val 80与预测值90进行比较。因此,由于预测值大于参考值ref_val,因此垃圾收集预测模块130可以将垃圾收集请求信号gcreq提供给存储器控制器200,从而执行垃圾收集。

171.在上面,已经使用逻辑块地址累计计数lba_ac描述了根据本公开的技术精神的实施例,但是实施例不限于此。

172.通过垃圾收集预测模块130的经训练的神经网络模型140,可以在不满足垃圾收集性能标准的时间段执行垃圾收集。例如,通过预测垃圾收集被执行的时间段,可以减少由垃圾收集引起的负载,并且可以进一步提高存储器存储装置10的性能。

173.图19是示出根据一些实施例的电子装置中的垃圾收集操作的梯形图。

174.参照图19,主机100可以将逻辑块地址lba、写入请求信号wreq和第一写入数据wdata1提供给存储器控制器200(步骤s430)。存储器控制器200可以响应于写入请求信号wreq执行程序(步骤s431)。存储器控制器200可以将地址addr、写入命令wcmd和第一写入数据wdata1提供给非易失性存储器300(步骤s432)。非易失性存储器300可以响应于从存储器控制器200提供的写入命令wcmd来写入第一写入数据wdata1(步骤s433)。

175.主机100可以存储逻辑块地址lba或第一写入数据wdata1中的至少一个(步骤s434)。然后,主机100可以使用神经网络模型140执行垃圾收集预测(步骤s435)。例如,可以使用逻辑块地址lba或第一写入数据wdata1中的至少一个来训练神经网络模型140。主机

100的垃圾收集预测模块130可以使用经训练的神经网络模型140输出预测值。垃圾收集预测模块130可以将预测值与参考值进行比较,如果满足该标准,则将垃圾收集请求信号gcreq和逻辑块地址lba提供给存储器控制器200(步骤s436)。

176.存储器控制器200可以响应于垃圾收集请求信号gcreq执行垃圾收集(步骤s437)。例如,垃圾收集管理器模块224可以通过垃圾收集触发模块222执行非易失性存储器300的垃圾收集。因此,存储器控制器200可以将地址addr、写入命令wcmd和擦除命令ecmd提供给非易失性存储器300(步骤s438)。

177.响应于接收到的写入命令wcmd和擦除命令ecmd,非易失性存储器300可以复制和擦除与地址addr相对应的块的有效页,从而执行垃圾收集(步骤s439)。

178.图20和图21是示出根据一些实施例的使用神经网络的垃圾收集预测操作的示图。

179.参照图20,在第n块的情况下,可以满足用于非易失性存储器300的空闲块计数fbc的条件,但是可以不满足用于逻辑块地址累计计数lba_ac的条件。

180.在第(n+1)块的情况下,可以满足非易失性存储器300的空闲块计数fbc的条件和逻辑块地址累计计数lba_ac的条件两者。

181.在第(n+2)块的情况下,非易失性存储器300的逻辑块地址累计计数lba_ac的条件和空闲块计数fbc的条件都可以不被满足。

182.在这种情况下,即使满足一个条件,也可以执行非易失性存储器300的垃圾收集。例如,可以执行第n块和第(n+1)块的垃圾收集。然而,由于不满足条件,因此可以不执行第(n+2)块的垃圾收集。

183.参照图21,垃圾收集预测模块130可以包括神经网络模型140和确定器131。这里,神经网络模型140可以包括第一神经网络模型145和第二神经网络模型146。

184.可以使用非易失性存储器300的空闲块计数fbc来训练第一神经网络模型145。可以使用逻辑块地址累计计数lba_ac来训练第二神经网络模型146。

185.确定器131可以从第一神经网络模型145和第二神经网络模型146接收结果,如果满足至少一个条件,则将垃圾收集请求信号gcreq发送到存储器控制器200。例如,确定器131可以根据图20的表输出结果。

186.在本实施例中,神经网络模型140被描述为仅使用元数据mdata和逻辑块地址lba之一进行训练,但是根据本公开的技术精神的实施例不限于此。例如,可以使用所有的元数据mdata、写入数据wdata和逻辑块地址lba来训练神经网络模型140。

187.在下文中,将参照图22和图23描述包括具有垃圾收集预测模块240的存储器控制器200的电子装置1。

188.图22是示出根据一些实施例的电子装置的框图。图23是示出图22的电子装置中的垃圾收集操作的梯形图。为了描述的简化,将简要给出或省略与参照图1至图21的描述重复的描述。

189.参照图22,主机100可以包括应用处理器110和存储器120。存储器控制器200可以包括缓冲器231、数据写入模块230、垃圾收集触发模块222、垃圾收集管理器模块224、存储器信息收集模块226和垃圾收集预测模块240。例如,在本实施例中,主机100可以不包括垃圾收集预测模块240,但是存储器控制器200可以包括垃圾收集预测模块240。

190.应用处理器110可以将逻辑块地址lba、写入请求信号wreq和写入数据wdata提供

给缓冲器231。缓冲器231可以临时存储接收到的逻辑块地址lba、写入请求信号wreq和写入数据wdata。缓冲器231可以将所存储的逻辑块地址lba、写入请求信号wreq和数据wdata提供给数据写入模块230。此外,缓冲器231可以将所存储的逻辑块地址lba以及写入数据wdata提供给垃圾收集预测模块240。

191.包括在存储器控制器200中的垃圾收集预测模块240可以与上述垃圾收集预测模块130相同。例如,垃圾收集预测模块240可以预测使用经训练的神经网络模型250执行垃圾收集的时间段。

192.垃圾收集预测模块240可以接收逻辑块地址lba、写入数据wdata和元数据mdata,并使用逻辑块地址lba、写入数据wdata或元数据mdata中的至少一个来训练神经网络模型250。

193.如果由经训练的神经网络模型250预测的结果值满足特定条件,则垃圾收集预测模块240可以将垃圾收集请求信号gereq和逻辑块地址lba提供给垃圾收集触发模块222。因此,存储器控制器200可以执行非易失性存储器300的垃圾收集。

194.参照图23,主机100可以将逻辑块地址lba、写入请求信号wreq和第一写入数据wdata1提供给存储器控制器200(步骤s440)。存储器控制器200可以响应于写入请求信号wreq执行程序(步骤s441)。存储器控制器200可以将地址addr、写入命令wcmd和第一写入数据wdata1提供给非易失性存储器300(步骤s442)。非易失性存储器300可以响应于从存储器控制器200提供的写入命令wcmd来写入第一写入数据wdata1(步骤s443)。

195.在第一写入数据wdata1写入非易失性存储器300的存储单元阵列310之后,非易失性存储器300可以将第一元数据mdata1提供给存储器控制器200(步骤s444)。例如,非易失性存储器300可以将第一元数据mdata1提供给存储器控制器200的存储器信息收集模块226。存储器控制器200的存储器信息收集模块226可以将接收到的第一元数据mdata1提供给存储器控制器200的垃圾收集预测模块240。

196.垃圾收集预测模块240可以存储逻辑块地址lba、第一写入数据wdata1和第一元数据mdata1(步骤s445)。垃圾收集预测模块240可以通过使用利用逻辑块地址lba、第一写入数据wdata1或第一元数据mdata1中的至少一个训练的神经网络模型250来执行垃圾收集预测(步骤s446)。

197.垃圾收集预测模块240可以使用经训练的神经网络模型250输出预测值。垃圾收集预测模块240可以将预测值与参考值进行比较,如果满足标准,则将地址addr、写入命令wcmd和擦除命令ecmd提供给非易失性存储器300(步骤s447)。

198.非易失性存储器300可以接收地址addr、写入命令wcmd和擦除命令ecmd以执行存储单元阵列310的垃圾收集(步骤s448)。

199.在本实施例中,与在上述其他实施例中的包括垃圾收集预测模块130的主机100不同,存储器控制器200可以包括垃圾收集预测模块240。例如,即使诸如元数据mdata的信号没有被发送到主机100,垃圾收集预测也可以由存储器控制器200本身执行。

200.在下文中,将参照图24描述包括具有应用处理器110的主机100的电子装置1。

201.图24是示出根据一些实施例的电子装置的框图。为了描述的简化,将简要给出或省略与参照图1至图21的描述重复的描述。

202.参照图24,主机100可以包括应用处理器110。应用处理器110可以包括神经网络模

型140。例如,与参照图1至图21描述的电子装置1不同,主机100可以不包括存储器120和垃圾收集预测模块130。

203.例如,应用处理器110可以代替地执行垃圾收集预测模块130的功能。另外,存储器120和垃圾收集预测模块130的功能可以仅由应用处理器110来实现。

204.应用处理器110可以向存储器控制器200提供逻辑块地址lba、写入请求信号wreq和写入数据wdata。应用处理器110可以从存储器控制器200接收元数据mdata以训练神经网络模型140。当满足特定垃圾收集执行条件时,应用处理器110可以使用经训练的神经网络模型140将垃圾收集请求信号gcreq和逻辑块地址lba提供给存储器控制器200。

205.在下文中,将参照图25描述包括多个非易失性存储器301、302和303的电子装置2。

206.图25是示出根据一些实施例的电子装置的框图。为了描述的简化,将简要给出或省略与参照图1至图24的描述重复的描述。

207.参照图25,存储器存储装置10可以包括连接到存储器控制器200的多个非易失性存储器301、302和303。

208.非易失性存储器301、302和303中的每一个可以与参照图3描述的非易失性存储器300基本上相同。例如,非易失性存储器301、302和303中的每一个可以包括存储单元阵列310、地址译码器320、电压发生器330、读/写电路340、控制逻辑350等。

209.存储器控制器200和非易失性存储器301可以通过第一通道1连接。存储器控制器200和非易失性存储器302可以通过第二通道2连接。存储器控制器200和非易失性存储器303可以通过第三通道3连接。

210.参照图1至图21描述的垃圾收集预测模块130可以被包括在主机100中。例如,主机100中包括的垃圾收集预测模块130可以使用从非易失性存储器301、302和303中的每一个发送的元数据mdata来训练神经网络模型140。另外,经训练的神经网络模型140可以用于预测对非易失性存储器301、302和303中的每一个执行垃圾收集的时间段。

211.参照图22和图23描述的垃圾收集预测模块240可以被包括在存储器控制器200中。例如,包括在存储器控制器200中的垃圾收集预测模块240可以使用从非易失性存储器301、302和303中的每一个发送的元数据mdata来训练神经网络模型250。另外,经训练的神经网络模型250可以用于预测对非易失性存储器301、302和303中的每一个执行垃圾收集的时间段。

212.在详细描述的最后,本领域技术人员将理解,可以在不实质上脱离本公开的原理的情况下对优选实施例进行许多变化和修改。因此,所公开的本发明的优选实施例仅在一般性和描述性意义上使用,而不是出于限制的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1