一种提高量子计算保真度的量子位拓扑结构重构方法

1.本发明涉及量子计算技术领域,尤其涉及一种提高量子计算保真度的量子位拓扑结构重构方法。

背景技术:

2.虽然目前量子计算设备仅是一种量子计算原型机,其易出错且不支持量子容错计算,但是在某些场合依然可以表现出远超经典计算的性能。

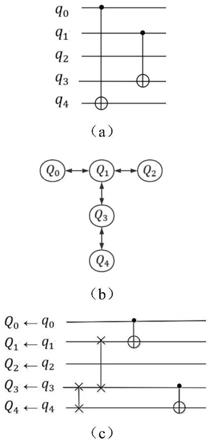

3.量子算法一般可以用量子线路的形式表示,当在量子计算设备上运行一个量子线路时,量子线路中的逻辑量子位需要映射到设备上的物理量子位。ibmq平台的一个物理量子位只允许与近邻量子位直接交互,这种约束被称为量子位交互约束,其限定了哪两个量子位上可以实现两量子位操作.拓扑结构上的有无连接线代表两个量子位是否可以直接交互。图1.(b)代表ibmq_quito,其量子位0可以与1直接交互,但是量子位0不能和3直接交互。假设一条逻辑线路的量子位之间是全交互的,逻辑量子位要映射到物理量子位,很难保证逻辑量子线路中的所有两量子位操作均满足量子位交互约束.此时需要通过量子线路转换,将一个逻辑量子线路(假设量子位之间完全交互性且忽略噪声)转换为一个遵循设备物理约束的量子线路,即将线路与设备兼容。

4.保真度指量子算法在量子计算设备上执行正确的概率。目前的量子计算设备存在各种噪声因素,且同种噪声中也存在差异,影响着量子计算设备上执行量子线输出正确结果的概率,所以尽量使用保真度高的量子操作对提高量子计算成功率而言至关重要。图1.(a)显示了一个有2个量子门组成的量子逻辑线路,图1.(b)显示设备ibmq_quito的拓扑结构,图1.(c)显示了将图1.(a)的逻辑线路映射到图1.(b)上的近邻化量子线路。图2显示了将图1.(b)的近邻化的量子线路在平台上执行1000次的分布结果,理论上输入|00000>输出|00000>,但是有其它输出,因为噪声存在。

5.cnot error可以影响一个或两个量子位的值或相位,且两量子位cnot error并不等价。如图3.(a)和图3.(b)分别显示设备ibmq_quito,设备ibmq_16_melbourne上的cnot error分布情况。边的颜色越深代表cnot error越小,其cnot门映射到对应的量子位上,执行出正确结果的概率越大。不同设备其cnot error不一样,量子线路映射在不同的设备上的执行的正确率不一样。

6.两量子位运算的错误率比单量子位运算的错误率数量级要高。如图4显示了设备ibmq_quito的部分噪声参数,cnot error要比single

‑

qubit pauli

‑

x error至少高一个数量级。

7.在进行量子逻辑线路的映射时,需考虑多方面的因素,主要包含以下几个方面:

8.(1)近邻:以ibmq为代表的超导构成的量子架构体系中,只允许最近邻的量子位之间交互。在量子线路映射过程中要满足物理约束,即线路中的双量子位门经过转换,映射在设备上时候,其控制位与目标位近邻。

9.(2)保真:在进行量子逻辑线路的映射时,应尽量减少达到近邻添加的交换门

(swap gate)数量,且将更多数量的门映射到设备上具有高保真的操作度,从而增加整个量子线路的保真度。

10.目前现有技术缺点有以下几个方面:(1)引入的辅助门多:当量子线路中的双量子位门要在量子计算设备上执行,要是不近邻的双量子位门,即在拓扑结构上两个量子位之间没有边相连,则需要插入引入辅助操作(比如使用swap门),辅助门一旦多,则增加计算错误。将cnot(0,2)映射到图3.(b)上的量子位0,2时,因为量子位不是近邻,需要插入swap门满足物理约束。与插入swap(0,14),swap(14,13),swap(13,12),swap(12,11),swap(11,3),swap(3,2)相比,插入swap(0,1),swap(1,2)实现近邻方式门数少且避开低保真的操作,执行的成功率较高。(2)保真度低:其中cnot error可以影响一个或两个量子位的值或相位。量子线路映射时,因为噪声大小不同,导致输出结果不一样。图3.(a)中量子位0 1的cnot error比量子位1 2之间的cnot error低。例如将cnot(0,4)映射到图3.(a)量子位0 1上要比映射到量子位3,4上,执行的成功率高。

11.如何解决上述技术问题为本发明面临的课题。

技术实现要素:

12.本发明的目的在于提供一种提高量子计算保真度的量子位拓扑结构重构方法。

13.本发明是通过如下措施实现的:在已知一种n个量子位的量子计算设备的拓扑结构和噪声因素前提下,以该拓扑结构为基础,与另一种n个量子位的拓扑结构和噪声因素进行比较,重构量子位拓扑结构;

14.主要包括以下步骤:

15.步骤一:从已知的量子计算设备的拓扑结构中,选择两个量子位数相等期且不同种的拓扑结构;

16.步骤二:分别获得选择的量子计算设备的噪声因素,从中提取cnot error参数;

17.步骤三:比较两个拓扑结构的相同两个量子位,观察两个量子位之间是否均有连通约束,如果有,选择此连接方式,用于量子位直接交互,减少插入swap门;若两个量子位均没有连通约束,则不进行任何操作;图5.(a)、5.(b)显示两种拓扑结构,且两个量子位之间是否存在边代表其两个量子位能否直接交互,在图5.(b)上的量子位0 3存在边,表示有连通约束,能直接交互。在图5.(a)上的量子位0 3没有一条直接相连接的边,cnot门映射到量子位0 3时则需要插入一个swap门;

18.步骤四:比较两个拓扑结构的相同两个量子位,如果两个量子位之间均有连通约束,选择其中cnot error错误率低的拓扑结构的量子位连接方式;图6.(a)、6.(b)显示两个拓扑结构,边上的数字代表两个量子位之间的cnot error,图6.(a)的cnot error低于图6.(b)上的值,所以选择图6.(a)的量子位0 1的连接方式;

19.步骤五:重复步骤三和步骤四,直到全部将拓扑结构上的量子位两两比较完毕,重构量子位拓扑结构。

20.与现有技术相比,本发明的有益效果为:

21.(1)插入的swap门数量少:通过将量子位拓扑结构重构,部分量子位可以实现直接交互,减少swap门的插入。

22.(2)执行正确结果的概率高:将逻辑线路中的双量子门映射到设备上的较高保真

度的量子位上时,提高执行后的保真度。

23.(3)运行更多的量子门数:目前量子计算设备上能执行的门数有限,即在其执行门数越多的时候其保真度也会下降,对比原先保真度不变的情况下,通过映射在重构的量子位拓扑结构时候减少的swap门数,来执行含有更多门数的量子线路。

24.(4)经济:相比于重新建造量子计算机设备,这种量子位拓扑结构重构方法在经济成本上更加低廉。

25.(5)操作简单:步骤操作简单明确,不需要太复杂的流程。

附图说明

26.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。

27.图1.(a)表示一个由2个量子门组成的量子逻辑线路;图1.(b)表示量子计算设备ibmq_quito的拓扑结构;图1.(c)表示图1.(a)的逻辑量子线路经过转换后且满足图1.(b)上的量子计算设备物理约束的一种线路

28.图2显示了将图1.(c)量子线路在图1.(b)所示的量子计算设备上上执行1000次的结果分布

29.图3.(a)和图3.(b)分别显示量子计算设备ibmq_quito,ibmq_16_melbourne上的cnot error分布情况

30.图4显示了设备ibmq_quito的部分噪声参数,

31.图5.(a),5.(b)显示了两个量子计算设备的拓扑结构,两个量子位之间是否存在边代表其两个量子位能否直接交互。

32.图6.(a),6.(b)显示了假定的两个量子计算的拓扑结构且边上的数字代表两个量子位之间的cnot error

33.图7显示了两个五量子位的量子设备的拓扑结构

34.图8显示重构的量子位拓扑结构

具体实施方式

35.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。当然,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

36.实施例1

37.参见图1至图8,本发明提供其技术方案为,如图7显示了两个五量子位的量子设备的拓扑结构,并获得其对应的参数,根据其具体参数或拓扑结构上的颜色深浅判断其错误率低高,颜色越深代表其错误率越低。随机以图7.(b)所示的拓扑结构为基础,进行了以下操作来重构了量子位拓扑结构:

38.所述量子位拓扑结构包括以下内容:

39.(1)对于量子位0 1来说,拓扑结构(b)上量子位0 1相对于拓扑结构(a)上量子位0 1来说cnot error高,所以在量子位0 1方面选择拓扑结构(a)的连通约束。

40.(2)对于量子位0 2来说,拓扑结构(b)上量子位0 2有连通约束可以直接交互,然

而(a)的量子位0 2无法直接交互,所以选择(b)的量子位0 2连方式。

41.(3)对于量子位0 3来说,拓扑结构(a)(b)的量子位0 3均无连通约束,不可以直接交互,所以不进行任何操作。

42.(4)对于量子位0 4来说,拓扑结构(a)(b)的量子位0 4均无连通约束,不可以直接交互,所以不进行任何操作。

43.(5)对于量子位1 2来说,拓扑结构(b)上量子位1 2相对于拓扑结构(a)上量子位1 2来说cnot error高,选择拓扑结构(a)的量子位1 2连接方式。

44.(6)对于量子位1 3来说,拓扑结构(b)上量子位1 3均无连通约束,拓扑结构(a)上量子位1 3来说有连通约束能直接交互,选择拓扑结构(a)的量子位1 3连接方式。

45.(7)设备b上量子位3 4相对于拓扑结构(a)上量子位3 4来说cnot error低,选择拓扑结构(b)的连接方式。

46.(8)不断重复上述类似过程,直到拓扑结构上所有任意两两量子位对比完成。

47.重构的量子位拓扑结构如图8显示,充分结合了拓扑结构(a)(b)的优点。将线路映射图8的设备上既能减少swap门数,又能提高量子线路的保真度。

48.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1