一种具备物理不可克隆函数功能的多熵源随机数发生器

1.本发明一种具备物理不可克隆函数功能的多熵源随机数发生器,属于集成电路技术领域。

背景技术:

2.随机数发生器(random number generator, rng)是密码系统的关键组件,用于生成随机种子和密钥,密钥与网络的安全性密切相关,常用于对传输信息进行加密和解密。此外,随机数发生器还应用于生成填充位、生成差分功率分析的掩码、生成一次性密码、实现统计模拟等。但是现有的随机数发生器由于其结构复杂,且随机数熵源单一,不可编程,使产生的随机数安全性较低,因此,需要提出一种结构简单、易集成的具备物理不可克隆函数功能的多熵源随机数发生器。

技术实现要素:

3.本发明为了克服现有技术中存在的不足,所要解决的技术问题为:提供一种具备物理不可克隆函数功能的多熵源随机数发生器硬件结构的改进。

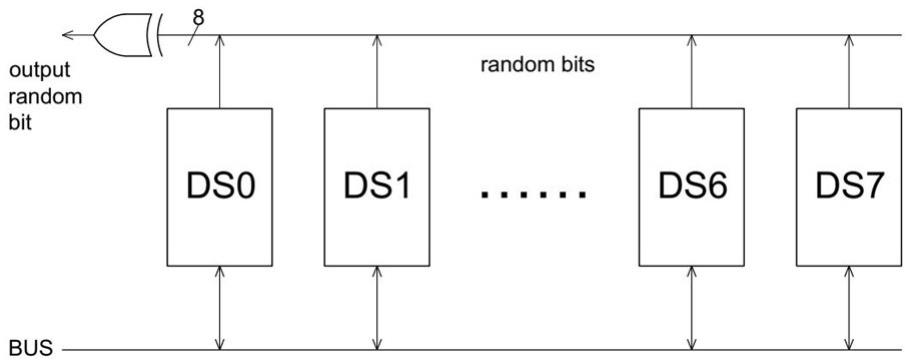

4.为了解决上述技术问题,本发明采用的技术方案为:一种具备物理不可克隆函数功能的多熵源随机数发生器,包括8个相互独立且分散布局的数据产生模块,每个数据产生模块结构完全相同,能够生成三种物理熵源,用于产生物理随机数或者物理不可克隆函数的响应;通过总线对每一个数据产生模块进行配置,决定每个数据产生模块的工作状态,当8个数据产生模块都工作在随机数模式且包含三种物理熵源时,经过异或处理后得到随机数;当选中其中的某一数据产生模块,并且工作于物理不可克隆函数功能时,通过总线完成激励的写入和响应的读取;其中三种物理熵源分别为布尔网络熵源、环形振荡器熵源、亚稳态熵源。

5.所述数据产生模块通过总线连接而成,微处理器或者微控制器通过总线完成对各个数据产生模块的配置,运行随机数发生器功能时,8比特随机数经过异或运算后作为最终输出;运行物理不可克隆函数功能时,通过总线选中某一数据产生模块,进行配置信息、写入激励和读取响应;数据产生模块中的bus interface模块完成信息的交互,接收微处理器或者微控制器发送的指令信息,输出function作为配置信息给ctrl模块。

6.所述数据产生模块包括混合网络、ctrl模块、后处理模块,所述控制模块通过控制信号使混合网络产生三种物理熵源中的任意一种或产生物理不可克隆函数的响应,经过熵源采集和后处理模块输出随机数或者通过总线读取物理不可克隆函数的响应;所述混合网络包括8个hxor单元和1个hxnor单元。

7.所述物理不可克隆函数在混合网络变换为布尔网络的基础上,将hxor单元输出节点的初始状态作为激励,并将布尔网络的混沌瞬态作为响应,构成了激励响应对。

8.当运行布尔网络熵源时,hxor/hxnor单元将输入信号previous、next执行逻辑异或/同或后输出信号out,任意一个hxor/hxnor单元的输出out连接到前一个单元的输入next,同时连接到后一个单元的输入previous,构成布尔网络结构产生混沌信号。

9.当运行环形振荡器熵源时,任意一个hxor/hxnor单元将输入信号previous执行逻辑非运算输出信号out,所有的hxor/hxnor单元将在布尔网络的互联基础上变化为9个反相器构成的环形振荡器,构成基于环形振荡器的熵源结构。

10.当运行亚稳态熵源时,每个hxor/hxnor单元中的反馈回路,等效为单个反相器与多路选择器组成的回路,hxor/hxnor单元输出信号呈现出不稳定的状态,即构成亚稳态熵源。

11.当电路运行物理不可克隆函数功能时,ctrl模块将激励信号写入到8个hxor单元中,控制信号跳转为布尔网络熵源的控制信号的同时,ctrl模块发出一个采样脉冲,经过延迟模块后采集布尔网络的输出作为bn

‑

puf的响应。

12.所述延迟模块由偶数个反相器级联组成。

13.所述后处理模块将采集到的随机值进行逻辑异或运算,再使用线性反馈移位寄存器去除随机比特位之间的偏差。

14.本发明相对于现有技术具备的有益效果为:本发明提供的具备物理不可克隆函数功能的多熵源随机数发生器全部由数字逻辑电路组成,具有结构简单易于实现的优势,可广泛应用于保密通信、密钥分发、数据加密等信息安全领域,可在现场可编程逻辑门阵列(field programmable gate array,fpga)上实现与验证,为同类芯片设计实现提供原型支持。

附图说明

15.下面结合附图对本发明做进一步说明:图1为本发明多熵源随机数发生器的结构示意图;图2为本发明数据产生模块的结构示意图;图3为本发明混合网络中hxor单元、hxnor单元的结构示意图;图4为本发明控制逻辑的状态转移图;图5为本发明后处理模块的结构示意图。

具体实施方式

16.如图1至图5所示,本发明一种具备物理不可克隆函数功能的多熵源随机数发生器,包括8个相互独立且分散布局的数据产生模块,每个数据产生模块结构完全相同,能够生成三种物理熵源,用于产生物理随机数或者物理不可克隆函数的响应;通过总线对每一个数据产生模块进行配置,决定每个数据产生模块的工作状态,当8个数据产生模块都工作在随机数模式且包含三种物理熵源时,经过异或处理后得到随机数;当选中其中的某一数据产生模块,并且工作于物理不可克隆函数功能时,通过总

线完成激励的写入和响应的读取;其中三种物理熵源分别为布尔网络熵源、环形振荡器熵源、亚稳态熵源。

17.所述数据产生模块通过总线连接而成,微处理器或者微控制器通过总线完成对各个数据产生模块的配置,运行随机数发生器功能时,8比特随机数经过异或运算后作为最终输出;运行物理不可克隆函数功能时,通过总线选中某一数据产生模块,进行配置信息、写入激励和读取响应;数据产生模块中的bus interface模块完成信息的交互,接收微处理器或者微控制器发送的指令信息,输出function作为配置信息给ctrl模块。

18.所述数据产生模块包括混合网络、ctrl模块、后处理模块,所述控制模块通过控制信号使混合网络产生三种物理熵源中的任意一种或产生物理不可克隆函数的响应,经过熵源采集和后处理模块输出随机数或者通过总线读取物理不可克隆函数的响应;所述混合网络包括8个hxor单元和1个hxnor单元。

19.所述物理不可克隆函数在混合网络变换为布尔网络的基础上,将hxor单元输出节点的初始状态作为激励,并将布尔网络的混沌瞬态作为响应,构成了激励响应对。

20.当运行布尔网络熵源时,hxor/hxnor单元将输入信号previous、next执行逻辑异或/同或后输出信号out,任意一个hxor/hxnor单元的输出out连接到前一个单元的输入next,同时连接到后一个单元的输入previous,构成布尔网络结构产生混沌信号。

21.当运行环形振荡器熵源时,任意一个hxor/hxnor单元将输入信号previous执行逻辑非运算输出信号out,所有的hxor/hxnor单元将在布尔网络的互联基础上变化为9个反相器构成的环形振荡器,构成基于环形振荡器的熵源结构。

22.当运行亚稳态熵源时,每个hxor/hxnor单元中的反馈回路,等效为单个反相器与多路选择器组成的回路,hxor/hxnor单元输出信号呈现出不稳定的状态,即构成亚稳态熵源。

23.当电路运行物理不可克隆函数功能时,ctrl模块将激励信号写入到8个hxor单元中,控制信号跳转为布尔网络熵源的控制信号的同时,ctrl模块发出一个采样脉冲,经过延迟模块后采集布尔网络的输出作为bn

‑

puf的响应。

24.所述延迟模块由偶数个反相器级联组成。

25.所述后处理模块将采集到的随机值进行逻辑异或运算,再使用线性反馈移位寄存器去除随机比特位之间的偏差,0、1比例更加均匀。

26.本发明提供的具备物理不可克隆函数功能的多熵源随机数发生器,其中包含8个相互独立且分散布局的数据产生模块,每个数据产生模块结构完全相同,并且可以变换出三种设计原理的物理随机源,分别是基于自治布尔网络、环形振荡器、亚稳态原理实现,可用于产生物理随机数或者物理不可克隆函数的响应。通过总线协议完成对每一个数据产生模块进行配置,决定每个数据产生模块处于何种工作状态,当八个数据产生模块都工作在随机数模式且包含三种物理随机数原理时,经过异或处理后的随机数满足中华人民共和国密码行业标准gm/t 0008

‑

2012《安全芯片密码检测准则》规定的安全等级3。当选中其中的某一数据产生模块,并且工作于物理不可克隆函数功能时,通过总线协议完成激励的写入和响应的读取。

27.利用自治布尔网络中逻辑器件的非理想特性,如退化效应、非线性时间延迟和短脉冲抑制等,产生物理随机过程(如相位噪声或混沌信号),进而从中提取随机数具有实际应用价值。

28.基于环形振荡器的随机数发生器其原理是将环形振荡器中的噪声(频域分析中称之为相位噪声,时域分析中称之为相位抖动)转化成逻辑电平产生随机数。随机性根源是电子运动产生的热噪声,通过低频振荡器对高频振荡器进行采样、量化来产生随机数序列。

29.基于亚稳态的随机数发生器其原理是利用逻辑器件处于亚稳态时,触发器或者锁存器采集输入信号不满足建立保持时间要求,输出逻辑值取决于热噪声从而产生出随机序列。

30.本发明基于混合异或、混合同或单元设计混合网络结构,进而提出一种具备物理不可克隆函数功能的多熵源随机数发生器,每个数据产生模块中的随机数发生器功能根据配置信息决定使用混合网络变换出的布尔网络、环形振荡器和亚稳态熵源中的任意一种,经过熵源采集和后处理输出随机数。

31.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,通过ctrl模块控制混合网络的运行状态,控制信号决定混合网络运行何种状态如附图4所示:s0基于布尔网络随机数发生器,s1基于环形振荡器的随机数发生器,s3基于亚稳态的随机数发生器,s2运行物理不可克隆函数。

32.本发明的具备物理不可克隆函数功能的多熵源随机数发生器可以利用现场可编程门阵列(fpga)、复杂可编程逻辑器件(cpld)、专用标准产品(assp)、专用集成电路(asic)实现。

33.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,由8个相同的数据产生模块(ds)组成,通过总线协议互联而成。微处理器或者微控制器通过总线协议完成对各个数据产生模块的配置,运行随机数发生器功能时,8比特随机数经过异或处理后作为最终输出;运行物理不可克隆函数功能时,通过总线协议选中某一数据产生模块,进行配置信息、写入激励和读取响应。

34.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,数据产生模块中的bus interface模块完成信息的交互,接收微处理器或者微控制器发送的指令信息,输出function作为配置信息给控制(ctrl)模块,例如当function=2’b00运行布尔网络熵源。当function=2’b10运行puf功能,并且通过总线进行写入激励和读取响应。

35.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,其中控制(ctrl)模块包括输入信号clock(时钟)、reset(状态重置)、function(功能选择)、challenge(8bit输入激励);输出信号pulse(用于采集puf响应)、control(2bit控制信号)、challenge_out(经过时序调整的激励信号)。

36.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,其中混合网络由8个hxor和1个hxnor单元组成,hxor和hxnor单元组成如图3所示,根据排列组成混合网络,其中hxor/hxnor的输出端out连接到前一个hxor/hxnor的next端,同时连接到下一个hxor/hxnor的previous端。ctrl模块的control信号连接到hxor/hxnor单元control信号,hxor单元的challenge按位连接到ctrl的8bit challenge_out总线,hxnor单元没有challenge输入。

37.本发明的具备物理不可克隆函数功能的多熵源随机数发生器,混合网络中的out[2]、out[5]、out[8]分别连接到3个d触发器数据端,采集到的随机比特位输出到后处理模块lfsr,经过后处理模块输出随机数。

[0038]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,ctrl模块发出采样脉冲经过延迟(delay)模块后,由8个d触发器采集布尔网络中8个hxor单元的输出位作为puf响应,通过bus interface模块和总线协议与微控制器或微处理器完成信息的交互。

[0039]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,选择运行布尔网络熵源时control = 2’b00,hxor/hxnor单元将输入信号previous、next执行逻辑异或/同或后输出信号out,任意一个hxor/hxnor单元的输出out连接到前一个单元的输入next,同时连接到后一个单元的输入previous,构成布尔网络结构产生混沌信号。

[0040]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,选择运行环形振荡器熵源时control = 2’b01,任意一个hxor/hxnor单元将输入信号previous执行逻辑非运算输出信号out,所有的hxor/hxnor单元将在布尔网络的互联基础上变化为9个反相器构成的环形振荡器,构成基于环形振荡器的熵源结构。

[0041]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,选择运行亚稳态熵源时control= 2’b11。每个hxor/hxnor单元中的反馈回路,等效为单个反相器与多路选择器组成的回路。hxor/hxnor单元输出信号呈现出不稳定的状态,即构成亚稳态熵源。

[0042]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,随机数后处理模块首先将采集得到的3bit随机值进行逻辑异或运算,再使用线性反馈移位寄存器(linear feedback shift register,lfsr),其表达式为f(x) = x

9 + x

6 + x

5 + x

3 + x

2 + 1。lfsr作用是去除随机比特位之间的偏差,属于弱后处理电路,结构相对简单,随机数后处理速度较快。

[0043]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,其中物理不可克隆函数在混合网络变换为布尔网络的基础上,将hxor单元输出节点的初始状态作为激励,并将布尔网络的混沌瞬态作为响应,构成了激励响应对。bn

‑

puf可以通过混沌机制来放大电路器件存在的微小差异来产生不同的响应,其中激励和响应信号的数据位宽都是8bit,存在256个激励响应对。如果使用n个hxor和1个hxnor构成布尔网络(n+1为3的正整数倍),那么bn

‑

puf具有nbit*2

n

激励响应位,响应位与hxor个数存在超指数关系属于强puf范畴。

[0044]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,当电路运行物理不可克隆函数功能时,control = 2’b10将8bit激励信号写入到8个hxor单元中。control信号由2’b10跳转为2’b00的同时,ctrl模块发出一采样脉冲,经过延迟(delay)模块后采集布尔网络的输出作为bn

‑

puf的响应。delay模块由偶数个反相器级联组成,实验结果表明bn

‑

puf响应的均匀性、可靠性和唯一性分别接近于理想值50%、100%和50%。

[0045]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器,在xilinx artix7器件实现过程中延迟模块由24个反相器级联组成,采集得到bn

‑

puf的响应,计算其汉明重量(hamming weight,hw)为51.7%,片内汉明距离(hamming distance intra, hdintra)为2.1%,片间汉明距离(hamming distance inter, hdinter)为47.1%,分别接近于理想值50%、0%和50%。bn

‑

puf工作在0℃~70℃温度范围内,片内汉明距离hdintra 的值介于2%~4%之间,其可靠性最差为96%,表明布尔网络设计为物理不可克隆函数可稳定运行。

[0046]

本发明使用混合异或(hybrid xor,hxor),混合同或(hybrid xnor,hxnor)单元组成混合网络(hybrid network,hn)可变换为布尔网络、环形振荡器和亚稳态熵源,同时借由布尔网路产生混沌的特性引入物理不可克隆函数(physical unclonable function,puf)称之为bn

‑

puf,具有指数级增长的激励响应对(challenge response pairs, crps)空间属于强puf范畴。

[0047]

本发明的具备物理不可克隆函数功能的多熵源随机数发生器结构简单、易集成,可在现场可编程逻辑门阵列(field programmable gate array,fpga)上实现与验证,为同类芯片设计实现提供原型支持。

[0048]

关于本发明具体结构需要说明的是,本发明采用的各部件模块相互之间的连接关系是确定的、可实现的,除实施例中特殊说明的以外,其特定的连接关系可以带来相应的技术效果,并基于不依赖相应软件程序执行的前提下,解决本发明提出的技术问题,本发明中出现的部件、模块、具体元器件的型号、连接方式除具体说明的以外,均属于本领域技术人员在申请日前可以获取到的已公开专利、已公开的期刊论文、或公知常识等现有技术,无需赘述,使得本案提供的技术方案是清楚、完整、可实现的,并能根据该技术手段重现或获得相应的实体产品。

[0049]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1