一种集成芯片的制作方法

1.本发明涉及集成电路技术领域,特别是涉及一种集成芯片。

背景技术:

2.人工智能和5g nr等领域的快速技术迭代和演进对专用集成电路(asic)的灵活性提出挑战。已有方案是,asic搭配现场可编程逻辑门阵列(fpga)或asic内嵌嵌入式现场可编程逻辑门阵列(efpga)的部分可编程架构:在asic上实现相对固定系统功能;在fpga或efpga上实现技术迭代和演进线路的可变系统功能。

3.fpga或efpga承载系统关键功能,通常同时要求与asic的广泛连接,以及与外部大规模存储器的高带宽连接。现有技术如图1a,独立存储访问的部分可编程架构:建立fpga或efpga与asic连接(图1a.am1)以及asic与大规模存储器例如dram连接(图1a.am2)基础上,并增加fpga或efpga与大规模存储器(图1a.am3),这需要使用更多fpga或efpga的io接口,并导致功耗增加。现有技术如图1b,使用总线建立asic、大规模存储器及fpga或efpga的连接,避免了独立存储访问的fpga或efpga上同时产生多组io接口及功耗开销(如图1a.am1和1a.am3),但asic与fpga或efpga的互连及存储访问效率降低。

技术实现要素:

4.本发明提供一种集成芯片,其能够提高存储访问效率,并且降低功耗。

5.为解决上述技术问题,本发明提供的一个技术方案为:提供一种集成芯片,包括:第一逻辑组件,第一逻辑组件包括:第一可编程门阵列组合,包括至少一个第一可编程门阵列组件;第一专用集成电路阵列组件,第一专用集成电路阵列组件与至少一个第一可编程门阵列组件位于同一层;第一接口模块,包括第一键合引出区域;第一专用集成电路阵列组件以及至少一个第一可编程门阵列组件通过内部金属层与第一接口模块连接;第一存储阵列组件,第一存储阵列组件设置有第二键合引出区域,第二键合引出区域和第一键合引出区域构成三维异质集成互连,以将可编程门阵列组合、第一专用集成电路阵列组件与第一存储阵列组件上的互连信号连接在一起。

6.其中,第一接口模块靠近第一可编程门阵列组件的一侧具有接口路由单元;第一可编程门阵列组件的可编程功能模块通过内部金属层引出至第一可编程门阵列组件靠近第一接口模块的一侧且连接接口路由单元。

7.其中,第一可编程门阵列组件包括:可编程路由网络,至少一个第一可编程门阵列组件通过内部金属层与可编程路由网络互连,并通过可编程路由网络连接至接口路由单元。

8.其中,第一接口模块数量至少为二,两个第一接口模块与第一可编程门阵列组件间隔设置。

9.其中,第一可编程门阵列组件为现场可编程门阵列(field

‑

programmable gate array,fpga);或嵌入式现场可编程门阵列(embedded field

‑

programmable gate array,

efpga)。

10.其中,集成芯片还包括:物理层,物理层用于实现第一可编程门阵列组件、第一专用集成电路阵列组件与第一存储阵列组件之间的电平转换;物理层设置于第一接口模块上。

11.其中,集成芯片还包括:存储控制单元,存储控制单元设置于第一接口模块上;或者存储控制单元设置于第一可编程门阵列组件靠近第一接口的位置处;或者存储控制单元设置于第一专用集成电路阵列组件靠近第一接口的位置处;或者存储控制单元设置于第一存储阵列组件上;存储控制单元控制第一可编程门阵列组件对第一存储阵列组件进行存储访问。

12.其中,集成芯片还包括:第二存储阵列组件,第二存储阵列组件设置于第一可编程门阵列组合远离第一存储阵列组件的一侧;第二存储阵列组件设置有第三键合引出区域;第一接口模块包括第四键合引出区域,第一可编程门阵列组件与第二存储阵列组件通过第三键合引出区域、第四键合引出区域键合连接。

13.其中,集成芯片还包括:第二存储阵列组件,第二存储阵列组件设置于第一存储阵列组件远离第一可编程门阵列组合的一侧;第二存储阵列组件设置有第三四键合引出区域;第一存储阵列组件包括第四键合引出区域,第一存储阵列组件与第二存储阵列组件通过第四键合引出区域、第三键合引出区域键合连接。

14.其中,集成芯片还包括:存储控制单元,存储控制单元设置于第一接口模块上;存储控制单元控制第一可编程门阵列组件访问第一存储阵列组件以及第二存储阵列组件。

15.其中,第一可编程门阵列组件还包括:可编程逻辑单元,连接存储控制单元,可编程逻辑单元引出逻辑信号;存储控制单元基于逻辑信号分时选择性的控制第一可编程门阵列组件访问第一存储阵列组件,或者控制第一可编程门阵列组件访问第二存储阵列组件。

16.其中,集成芯片还包括:第一存储控制单元,设置于第一接口模块上;第二存储控制单元,设置于第一接口模块上;第一存储控制单元控制第一可编程门阵列组件访问第一存储阵列组件,第二存储控制单元控制第一可编程门阵列组件访问第二存储阵列组件。

17.其中,第一可编程门阵列组件还包括:可编程逻辑单元,连接第一存储控制单元以及第二存储控制单元,可编程逻辑单元引出逻辑信号;第一存储控制单元基于逻辑信号控制第一可编程门阵列组件访问第一存储阵列组件,第二存储控制单元同时基于逻辑信号控制第一可编程门阵列组件访问第二存储阵列组件。

18.本发明的有益效果,区别于现有技术的情况,本发明的集成芯片通过第一接口模块的第一键合引出区域、第二键合引出区域将第一逻辑组件与第一存储阵列组件键合在一起。其中,第一逻辑组件包括第一可编程门阵列组合和第一专用集成电路阵列组件,并且第一接口模块位于第一可编程门阵列阵列外。通过三维异质集成结构,实现可编程门阵列与存储阵列的高密度近存存储访问互连,实现存储访问的高带宽、低功耗的目的。

附图说明

19.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它

的附图,其中:

20.图1a与图1b为现有技术的集成芯片的结构示意图;

21.图2为本发明存算一体的集成芯片的第一实施例的结构示意图;

22.图3为本发明第一可编程门阵列组件的平面结构示意图;

23.图4为图2中第一可编程门阵列组件对第一存储阵列组件的存储访问结构示意图;

24.图5为本发明存算一体的集成芯片的第二实施例的结构示意图;

25.图6为图5中第一可编程门阵列组件以及第二可编程门阵列组件对第一存储阵列组件的共享存储访问的结构示意图;

26.图7为图5中第一可编程门阵列组件以及第二可编程门阵列组件对第一存储阵列组件独立存储访问的的结构示意图;

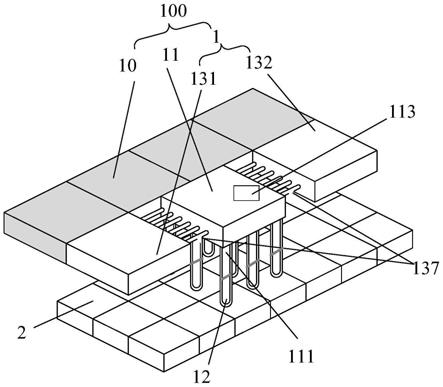

27.图8为本发明存算一体的集成芯片的第三实施例的结构示意图;

28.图9为图8中第一可编程门阵列组件对第一存储阵列组件以及第二存储阵列组件的共享存储访问的结构示意图;

29.图10为图8中第一可编程门阵列组件对第一存储阵列组件以及第二存储阵列组件的独立存储访问的结构示意图;

30.图11为本发明存算一体的集成芯片的第四实施例的结构示意图;

31.图12为图11中第一可编程门阵列组件对第一存储阵列组件以及第二存储阵列组件的共享存储访问的结构示意图;

32.图13为图11中第一可编程门阵列组件对第一存储阵列组件以及第二存储阵列组件的独立存储访问的结构示意图;

33.图14为可编程路由网络和可编程逻辑块的结构示意图;

34.图15为功能组件210、220、230之间的三维异质集成结构示意图。

具体实施方式

35.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

36.请参见图2,为本发明集成芯片的第一实施例的结构示意图。具体的,集成芯片包括第一逻辑组件100以及第一存储阵列组件2。本技术中,利用三维异质异构集成的方式将第一逻辑组件100以及第一存储阵列组件2键合集成在一起。以此能够实现集成芯片的高带宽、低功耗互连。

37.具体的,如图2所示,第一逻辑组件100包括第一可编程门阵列组合1、第一专用集成电路阵列组件10以及第一接口模块11。其中,第一可编程门阵列组合1包括至少一个第一可编程门阵列组件,本实施例以第一可编程门阵列组合1包括两个第一可编程门阵列组件131以及132为例进行说明。具体的,第一专用集成电路阵列组件10与第一可编程门阵列组件131、第一可编程门阵列组件132位于同一层。第一接口模块11包括并互连第一键合引出区域111。第一专用集成电路阵列组件10、第一可编程门阵列组件131、第一可编程门阵列组件132通过芯片内部金属层与第一接口模块11连接。

38.第一可编程门阵列组件131和第一可编程门阵列组件132包括:逻辑单元lab(logic array block)/clb(configurable logic block)、存储单元bram(block random access memory,bram)、乘法单元dsp(digital signal processer)、乘累加单元mac(multiply accumulate)和用于实现定制计算功能的用户单元等可编程功能模块的部分或全部任意组合,以实现通用可编程处理。第一可编程门阵列组件131和第一可编程门阵列组件132内包含可编程路由网络,可编程路由网络通过芯片的内部金属层广泛互连第一可编程门阵列组件131和第一可编程门阵列组件132,提供第一可编程门阵列组件131和第一可编程门阵列组件132之间的高带宽、可编程互连。

39.第一专用集成电路阵列组件10包括,乘加计算阵列、乘法计算阵列、脉动处理器阵列、哈希计算阵列、多种编码器阵列、机器学习的专用层阵列、检索功能阵列、图像/视频处理阵列以及cpu和mcu等硬核运算/处理单元的一种或多种任意组合。第一专用集成电路阵列组件10具备有限的可编程性或不具备可编程性,应用于特定需求的计算/处理加速,较具备任意可编程性的能可编程功能模块的计算/处理密度大很多,显著增加集成芯片计算/处理密度。第一存储阵列组件2包括并互连第二键合引出区域12。第二键合引出区域12和第一键合引出区域111构成三维异质集成互连,进而将可编程门阵列组合1中的第一可编程门阵列组件131、第一可编程门阵列组件132以及第一专用集成电路阵列组件10与第一存储阵列组件2连接在一起。进而实现集成芯片的高带宽、低功耗的可编程存算一体结构。

40.在一实施例中,第一存储阵列组件2可以为dram(dynamic random access memory,随机存储器),在另一实施例中,第一存储阵列组件2还可以为sram(static random access memory,静态随机存储器),当然考虑到技术迭代发展,第一存储阵列组件2还可以为其它类型的存储器或sram以及其它类型存储器的组合,例如闪存(flash)、变阻存储器(rram或reram)、磁阻存储器(mram)、铁电存储器(feram)、氧化物电阻存储器(oxram)、电桥存储器(cbram)、相变存储器(pcm)、自旋转移力矩存储器(stt

‑

mram)和电擦除存储器(eeprom)等,具体不做限定。上述存储器有各自的特征优势,并可能需要存储控制器作为存储访问界面,存储控制器用于实现物理接口、数据读写、数据缓冲、数据预取、数据刷新和数据块重映射等功能,具体不做限定。

41.具体的,本技术中,第一接口模块11位于第一可编程门阵列组合1以及第一专用集成电路阵列组件10外。第一接口模块11靠近第一可编程门阵列组件131以及第一可编程门阵列组件132的两侧均设置有可编程路由网络延伸扩展的接口路由单元137,可以理解的,若第一可编程门阵列组合1仅包括一个第一可编程门阵列组件时,那么第一接口模块11仅靠近这一个第一可编程门阵列组件的一侧具有接口路由单元137。而这一个第一可编程门阵列组件中互连可编程功能模块的可编程路由网络通过芯片内部金属层连接至相邻的接口路由单元137。而本实施例中,第一接口模块11的两侧各设置有一个第一可编程门阵列组件,那么第一接口模块11靠近第一可编程门阵列组件131以及第一可编程门阵列组件132的两侧均设置有接口路由单元137。第一可编程门阵列组件131以及第一可编程门阵列组件132的可编程功能模块通过芯片内部金属层引出至第一可编程门阵列组件131以及第一可编程门阵列组件132靠近第一接口模块11的一侧且连接接口路由单元137。本实施例中,第一接口模块11设置在第一可编程门阵列组件131以及第一可编程门阵列组件132的外侧,第一可编程门阵列组件131以及第一可编程门阵列组件132的可编程功能模块需要通过芯片

内部金属层连接至第一接口模块11的接口路由单元137。并且进一步的,第一接口模块11还通过第一键合引出区域111与第一存储阵列组件2的第二键合引出区域12构成三维异质集成互连,且第一专用集成电路阵列组件10通过芯片内部金属层与第一接口模块11连接。以此实现集成芯片的高带宽、低功耗的可编程静态存算一体结构。具体的,通过三维异质集成互连的方式将第一可编程门阵列组合1、第一专用集成电路阵列组件10和第一存储阵列组件2互连,大大提高互连密度;降低互连分布参数,即提高互连速度并降低互连功耗。其中,第一可编程门阵列组件可通过重构,实现通用计算,进而实现系统通用性。

42.与现有io接口和/或io电路互连不同,第一专用集成电路阵列组件10、第一可编程门阵列组件131和第一可编程门阵列组件132通过芯片内部金属层与第一接口模块11连接,无需现有技术的io电路所提供的驱动、外部电平升压(输出时)、外部电平降压(输入时)、三态控制器、静电防护esd和浪涌保护电路等功能,不用通过现有技术的io接口和/或io电路互连,直接建立芯片内高密度金属层互连。

43.第一可编程门阵列组件131和第一可编程门阵列组件132,无需通过可编程门阵列的io接口和/或io电路引出互连线,而是通过可编程路由网络延伸扩展的接口路由单元,扩展与可编程门阵列组件广泛互连的可编程路由网络,外延并互连到第一专用集成电路阵列组件10和第一接口模块11。由此将可编程门阵列组件的可编程路由网络延伸至第一专用集成电路阵列组件10上,并形成广泛互连,由可编程门阵列组件的内部资源以高带宽、可编程的方式,调度第一专用集成电路阵列组件10上高密度计算单元,实现高密度、可编程计算/处理;由此将可编程门阵列组件的可编程路由网络延伸至第一接口模块11,并形成广泛互连,由可编程门阵列组件的内部资源以高带宽、可编程的方式,访问第一接口模块11。进一步的,第一可编程门阵列组件131和/或第一可编程门阵列组件132通过接口路由单元137,扩展可编程门阵列组件内部广泛互连可编程资源的可编程路由网络,外延并互连到第一接口模块11,进而通过三维异质集成互连到第一存储阵列组件2上的大容量存储阵列。三维异质集成互连实现在三维器件内部,无需现有技术的io电路所提供的驱动、外部电平升压(输出时)、外部电平降压(输入时)、三态控制器、静电防护esd和浪涌保护电路等功能,不用通过现有技术的io接口和/或io电路互连,直接建立跨芯片高密度金属层互连。三维异质集成互连,通过半导体金属制程工艺,实现芯片间的层叠互连,使得芯片间互连线物理及电气参数遵循半导体制程工艺特征,减少了孔、互连线和io结构的使用,增加芯片间的互连密度和互连速度;同时,三维异质集成互连因不通过传统io结构,且互连距离较短,降低了芯片之间的通讯功耗;进而提高了集成芯片的集成度和互连频率,并降低了互连功耗。由此可编程门阵列组件的可编程路由网络跨芯片延伸至第一存储阵列组件2上的大容量存储阵列,并形成广泛互连,实现可编程门阵列组件的可编程功能模块以高带宽、可编程的方式,对第一存储阵列组件2上的大容量存储阵列的三维异质集成的存储访问。三维集成芯片同时兼具外部存储器的大容量,以及类似可编程门阵列组件通过存储路由单元延伸可编程路由网络互连存储单元bram(现有技术,容量小)的,大位宽、高带宽的关键优势,从根本上突破了现有技术可编程门阵列组件扩展大规模存储器的io数量瓶颈、访存带宽瓶颈和访存功耗瓶颈。

44.在一实施例中,如图3所示的实施例中,第一可编程门阵列组件131和/或第一可编程门阵列组件132的可编程功能模块包括:可编程逻辑块(logic array block,lab/

configurable logic block,clb)133,存储块(block random access memory,bram)134,乘法单元(digital signal processer)135和乘加单元(multiply accumulate,mac)138和用于实现定制计算功能的用户单元等可编程功能模块的部分或全部任意组合。需要说明的是,乘法单元135不是数字信号处理器芯片,是嵌入式可编程乘法单元。

45.本实施例中,第一键合引出区域111即为第一可编程门阵列组合1中的跨芯片互连资源,也即第一可编程门阵列组合1直接通过跨芯片金属层互连至第一存储阵列组件2,实现存储访问,避免利用第一可编程门阵列组合1的io接口与第一存储阵列组件2互连,进而实现高带宽、低功耗的目的,并且具有密度高,分布参数低的优点。

46.在一具体实施例中,如图3所示,存储单元134通过存储路由单元136与逻辑单元133连接,进而连接至整个可编程路由网络。跨芯片互连大容量存储阵列的第一接口模块11通过接口路由单元137与逻辑单元133连接,进而连接至整个可编程路由网络。

47.如图3所示,本实施例的集成芯片,设计了接口路由单元137,接口路由单元137与第一可编程门阵列组合1的可编程功能模块内部的可编程路由网络广泛互连,并且接口路由单元137直接连接至第一可编程门阵列组合1外部的第一接口模块(图2第一接口模块11),进而通过第一接口模块与第一存储阵列组件2连接,实现第一可编程门阵列组合1的可编程功能模块,通过可编程路由网络的外延扩展,互连到第一存储阵列组件2上的大容量存储阵列中,建立第一可编程门阵列组合1的可编程功能模块对第一存储阵列组件2上大容量存储阵列的可编程、大容量、高带宽和低功耗的存储访问。

48.本实施例的集成芯片,实现第一可编程门阵列组合1以及第一专用集成电路阵列组件10对第一存储阵列组件2的存储访问,与传统技术中第一可编程门阵列组合1以及第一专用集成电路阵列组件10通过io接口与第一存储阵列组件2连接的方式不同,本实施例的集成芯片能够节省io资源,提供远高于io接口的互连密度和远低于io接口的互连距离,提高了存储访问带宽,降低了存储访问功耗。

49.在一实施例中,还可以在第一可编程门阵列组合1上设置全局总线,例如noc axi ahb等,可以实现第一可编程门阵列组合1上可编程逻辑跨区域存储访问。具体的,全局总线可以条带状设置在第一接口模块11的附近,或者还可以设置在其他存储访问关联位置处,具体不做限定。

50.在一实施例中,第一专用集成电路阵列组件10包括乘加计算阵列、乘法计算阵列、脉动处理器阵列、哈希计算阵列、多种编码器阵列、机器学习的专用层阵列、检索功能阵列、图像/视频处理阵列以及cpu和mcu等硬核运算/处理单元的一种或多种任意组合。第一专用集成电路阵列组件10具备有限的可编程性或不具备可编程性,应用于特定需求的计算/处理加速,较具备任意可编程性的能可编程功能模块的计算/处理密度大很多,显著增加集成芯片计算/处理密度。第一专用集成电路阵列组件10还可以设置第一可编程门阵列组合1的配置电路和锁相环等,配置电路和锁相环分别是独立于第一可编程门阵列组合1的可编程门阵列配置模块和可编程时钟模块。在一具体实施例中,可编程门阵列组件中的可编程功能模块以条带状排布,且专用集成电路阵列组件中的功能模块同样以条带状排布,以便提高被可编程功能模块调度效率。

51.集成芯片中,相邻组件之间通过三维异质集成互连,逐层建立芯片内高密度金属层互连,集成芯片中的构成组件被层叠设计和封装在同一个集成芯片内,无需现有技术中

的io电路所提供的驱动、外部电平升压(输出时)、外部电平降压(输入时)、三态控制器、静电防护esd和浪涌保护电路等功能,不用通过现有技术的io接口和/或io电路互连,而直接建立跨组件高密度金属层互连。因此减少可编程门阵列组件io结构的使用,增加专用集成电路组件、可编程门阵列组件和存储阵列组件的互连密度和互连速度;同时,三维异质集成互连因不通过传统io结构,且互连距离较短,降低了芯片之间的通讯功耗;进而提高了集成芯片的集成度以及专用集成电路组件、可编程门阵列组件和存储阵列组件互连频率,并降低了互连功耗。由此可编程门阵列组件上广泛互连可编程资源的可编程路由网络跨芯片延伸至存储芯片上的大容量存储阵列,并形成广泛互连,实现可编程资源以高带宽、可编程的方式,对存储芯片上的大容量存储阵列的三维异质集成的存储访问。多层芯片同时兼具外部存储器的大容量,以及类似可编程门阵列组件上通过可编程路由网络互连存储块bram(现有技术,容量小)的,大位宽、高带宽的关键优势。从根本上突破了现有技术可编程门阵列芯片扩展大规模存储器的io数量瓶颈、访存带宽瓶颈和访存功耗瓶颈。

52.在一实施例中,集成芯片还包括:存储控制单元113,存储控制单元113可以设置于第一接口模块11上,如图2所示;或者在另一实施例中,存储控制单元113还可以设置于第一接口模块11外且靠近第一接口模块11的位置处,例如,存储控制单元113设置于第一专用集成电路阵列组件10上,或者存储控制单元113设置于第一存储阵列组件2上。存储控制单元113用于控制第一可编程门阵列组合1对第一存储阵列组件2的存储访问,第一存储控制单元113还可以控制第一专用集成电路阵列组件10对第一存储阵列组件2的存储的访问(通过可编程门阵列组合1中的可编程路由网络建立互连)。本实施例的集成芯片,能够避免通过物理io接口和/或物理io电路互连,进而节省io资源,提供远高于io接口的互连密度,提高了存储访问带宽,降低了存储访问功耗。实现了第一可编程门阵列组合1以及第一专用集成电路阵列组件10内部信号到第一存储阵列组件2的高密度、近距离互连。

53.在一优选实施例中,将存储控制单元113设置在第一接口模块11上。由于可编程门阵列组件和专用集成电路组件访问存储阵列组件均需要通过第一接口模块11,这对数据流有利。在一优选实施例中,将存储控制单元设置于专用集成电路组件上,由于专用集成电路组件的工艺性能优于存储阵列组件,以此可以获得更高的密度和速度。在一优选实施例中,将存储控制单元设置于存储阵列组件上,由于存储阵列组件工艺比专用集成电路组件单位面积便宜,可以降低实现成本,并相对提高专用集成电路阵列组件密度。

54.在一实施例中,集成芯片上还设置物理层,用于实现第一逻辑组件100与第一存储阵列组件2之间的电平转换,因为第一逻辑组件100与第一存储阵列组件2的三维异质集成是芯片内金属层跨芯片互连,没有io电路进行电平转换,当第一逻辑组件100与第一存储阵列组件2内核电压不同时,需要设置物理层进行电平转换。物理层可以设置在第一逻辑组件100上,例如第一接口模块11上或附近;也可以设置在第一存储阵列组件2上,具体不做限定。

55.本技术中,第一接口模块11与第一存储阵列组件2的三维异质集成互连的物理及电气参数遵循半导体制程工艺特征,较传统pcb或2.5d封装,第一可编程门阵列组合1与第一存储阵列组件2的互连数量(存储访问带宽)提高4~2个数量级。较传统pcb或2.5d封装,实现第一可编程门阵列组合1与第一存储阵列组件2的直接互连,不经过io接口,使得互连距离更近,存储访问的功耗开销显著降低。形成第一可编程门阵列组合1与第一存储阵列组

件2的分布式、去中心化存储访问架构,实现第一可编程门阵列组合1上的可编程功能模块就近、独立的存储访问,避免传统共享总线的存储访问冲突和效率降低;节省了传统技术中用于互连第一可编程门阵列组合1与第一存储阵列组件2的io开销。

56.需要说明的是,本实施例中,在同一层中,第一接口模块11的数量至少为二,至少两个第一接口模块11与第一可编程门阵列组件间隔设置。

57.在本技术的一实施例中,如图4所示,图4提供了第一可编程门阵列组件对第一存储阵列组件2的存储访问结构。具体的,如图4所示,第一接口模块仅连接一个第一可编程门阵列组件。本实施例中,以存储控制单元设置于第一接口模块上为例进行说明。具体的,存储控制单元h21设置于第一接口模块h17上。第一存储阵列组件2上包括存储单元g13,第二键合引出区域g14设置在存储单元g13上,存储控制单元h21与第一键合引出区域h19连接,第一键合引出区域h19与第一存储阵列组件2上的第二键合引出区域g14连接。

58.进一步的,第一可编程门阵列组件上设置有可编程逻辑单元k23,可编程逻辑单元k23通过接口路由单元h22连接存储控制单元h21。可编程逻辑单元k23引出逻辑信号,存储控制单元h21基于逻辑信号控制第一可编程门阵列组件对第一存储阵列组件2进行存储访问。

59.进一步的,若在同一层中,第一接口模块11连接了多个第一可编程门阵列组件,那么这多个第一可编程门阵列组件可以共用存储控制单元h21实现对第一存储阵列组件2的存储访问。可以理解的,为了避免访问冲突,存储控制单元h21可以分时选择性的选择其中一个第一可编程门阵列组件对第一存储阵列组件2进行存储访问。在另一实施例中,还可以在第一接口模块11上设置两个存储控制单元h21,其中一个存储控制单元h21控制一个可编程门阵列组件对第一存储阵列组件2进行存储访问,另一个存储控制单元h21控制另一个可编程门阵列组件对第一存储阵列组件2进行存储访问。需要说明的是,若两个存储控制单元h21均能够控制第一存储阵列组件2的所有存储单元,那么,在两个第一可编程门阵列组件访问第一存储阵列组件2的同一存储单元时,两个存储控制单元h21分时选择性的选择其中一个第一可编程门阵列组件对第一存储阵列组件2进行存储访问。可以理解的,若两个存储控制单元h21分别控制第一存储阵列组件2的不同存储单元,那么,在两个第一可编程门阵列组件访问第一存储阵列组件2的不同存储单元,且这两个不同的存储单元分别被两个存储控制单元h21控制,则两个存储控制单元h21可以同时控制两个第一可编程门阵列组件访问第一存储阵列组件2的不同存储单元。

60.可以理解的,可以将上述所述的两个第一可编程门阵列组件替换为第一专用集成电路阵列组件10,也即,第一接口模块11连接一个第一可编程门阵列组件以及一个第一专用集成电路阵列组件10,第一可编程门阵列组件以及第一专用集成电路阵列组件10也可以按照上述所述的方法,共用同一存储控制单元h21实现对第一存储阵列组件2的分时存储访问。或者,还可以按照上述所述的方法,分别利用不同的存储控制单元h21实现对第一存储阵列组件2的分时存储访问,或同时存储访问,具体过程与上述相同,在此不再赘述。

61.本技术中,第一逻辑组件100与第一存储阵列组件2的数量以及位置可以根据需求进行设置,如图5所示,图5为本发明集成芯片的第二实施例的结构示意图。与上述图2所示的第一实施例相比,区别在于,本实施例的集成芯片还包括:第二逻辑组件200。第二逻辑组件200设置于第一逻辑组件100远离第一存储阵列组件2的一侧。具体的,第二逻辑组件200

包括第二可编程门阵列组合3、第二专用集成电路阵列组件30、第二接口模块31以及接口路由单元312。其中,第二可编程门阵列组合3包括至少一个第二可编程门阵列组件,本实施例以第二可编程门阵列组合3包括两个第二可编程门阵列组件341以及342为例进行说明。具体的,第二专用集成电路阵列组件30与第二可编程门阵列组件341、第二可编程门阵列组件342位于同一层,并与第二可编程门阵列组件341和/或第二可编程门阵列组件342中的可编程路由网络建立互连;接口路由单元312是第二可编程门阵列组件341和/或第二可编程门阵列组件342中的可编程路由网络建立互连的扩展,第二接口模块31,通过接口路由单元312,与第二可编程门阵列组件341和/或第二可编程门阵列组件342中的可编程路由网络建立互连。第二接口模块31包括第三键合引出区域311,本实施例中,第一接口模块11还包括第四键合引出区域32,第三键合引出区域311与第四键合引出区域32构成三维异质集成互连;接口路由单元312是第二可编程门阵列组件341和/或第二可编程门阵列组件342的互连资源,通过接口路由单元312和第二接口模块31,以及第三键合引出区域311和第四键合引出区域32,跨芯片连接到第一逻辑组件100上的第一接口模块11,进而连接到第一存储阵列组件2上的大容量存储阵列;建立第二可编程门阵列组合3的可编程功能模块对第一存储阵列组件2上大容量存储阵列的可编程、大容量、高带宽和低功耗的存储访问。

62.集成芯片中,相邻组件之间通过三维异质集成互连,逐层建立芯片内高密度金属层互连,集成芯片中的构成组件被层叠设计和封装在同一个集成芯片内,无需现有技术中的io电路所提供的驱动、外部电平升压(输出时)、外部电平降压(输入时)、三态控制器、静电防护esd和浪涌保护电路等功能,不用通过现有技术的io接口和/或io电路互连,而直接建立跨组件高密度金属层互连。因此减少可编程门阵列组件io结构的使用,增加可编程门阵列组件和存储阵列组件的互连密度和互连速度;同时,三维异质集成互连因不通过传统io结构,且互连距离较短,降低了芯片之间的通讯功耗;进而提高了集成芯片的集成度以及可编程门阵列组件和存储阵列组件互连频率,并降低了互连功耗。由此可编程门阵列组件上广泛互连可编程资源的可编程路由网络跨芯片延伸至存储芯片上的大容量存储阵列,并形成广泛互连,实现可编程资源以高带宽、可编程的方式,对存储芯片上的大容量存储阵列的三维异质集成的存储访问。多层芯片同时兼具外部存储器的大容量,以及类似可编程门阵列组件上通过可编程路由网络互连存储块bram(现有技术,容量小)的,大位宽、高带宽的关键优势。从根本上突破了现有技术可编程门阵列芯片扩展大规模存储器的io数量瓶颈、访存带宽瓶颈和访存功耗瓶颈。

63.相对于图2所示的第一实施例,本实施例的集成芯片能够进一步提高计算密度,有利于更复杂的可重构计算。结合本实施例的集成芯片,可以根据需求设置更多可编程门阵列组件或者设置更多的专用集成电路阵列组件,以提高集成芯片中的可编程门阵列组件以及专用集成电路阵列组件的密度。

64.本实施例所示的第二逻辑组件200与第一逻辑组件100相同,在此不再赘述。

65.本实施例的集成芯片,设置有两层逻辑组件,也即第二逻辑组件200与第一逻辑组件100。具体地,本实施例的集成芯片中,包括两层专用集成电路阵列组件,如第一专用集成电路阵列组件10以及第二专用集成电路阵列组件30;包括两层可编程门阵列组合,如第一可编程门阵列组合1以及第二可编程门阵列组合3。

66.本实施例中,第二可编程阵列组合3可以通过第一接口模块11和第二接口模块31

实现对第一存储阵列组件2的存储访问。其中,第二专用集成电路阵列组件30通过第二接口模块31以及第一接口模块11实现对第一存储阵列组件2的存储访问。

67.在一实施例中,第三键合引出区域311即为第二可编程门阵列组合3中的跨芯片互连资源,也即第二可编程门阵列组合3通过跨芯片互连资源与第一接口模块11建立金属层直接互连,进而通过第一可编程门阵列组合1中的互连资源(也即第一键合引出区域111)实现与第一存储阵列组件2互连,实现存储访问,避免利用第二可编程门阵列组合3的io接口与第一存储阵列组件2互连,进而实现高带宽、低功耗的目的,并且具有可编程资源密度高,分布参数低,存储访问速度快的优点。

68.需要说明的是,第二可编程门阵列组合3还可以与第一可编程门阵列组合1不同,其可以按照实际需要设置功能和/或数量不同的功能模块。例如,在一实施例中,第二可编程门阵列组合3的功能模块包括但不限于可编程逻辑模块、嵌入式存储单元、嵌入式乘法单元的任意组合。第一专用集成电路阵列组件10以及第二专用集成电路阵列组件30包括专用集成电路实现的硬核运算/处理单元(processing element),例如乘加计算阵列、乘法计算阵列、脉动处理器阵列、哈希计算阵列、多种编码器阵列、机器学习的专用层阵列、检索功能阵列、图像/视频处理阵列以及cpu和mcu等硬核运算/处理单元的一种或多种任意组合。第一专用集成电路阵列组件10以及第二专用集成电路阵列组件30具备有限的可编程性或不具备可编程性,应用于特定需求的计算/处理加速,其计算/处理密度大很多,显著增加集成芯片计算/处理密度。

69.本实施例中,第一接口模块11连接第一存储阵列组件2,并且连接第一可编程门阵列组合1,以及第一专用集成电路阵列组件10。第一接口模块11提供了第一可编程门阵列组合1对第一存储阵列组件2的存储访问通道,还提供了第一专用集成电路阵列组件10对第一存储阵列组件2的存储访问通道。第二接口模块31连接第一可编程门阵列组合1的第一接口模块11,并且连接第二可编程门阵列组和3以及第二专用集成电路阵列组件30。第二接口模块31、第一接口模块11提供了第二可编程门阵列组合3对第一存储阵列组件2的存储访问通道,还提供了第二专用集成电路阵列组件30对第一存储阵列组件2的存储访问通道。

70.本实施例中,第一逻辑组件100以及第二逻辑组件200共用同一存储控制单元访问第一存储阵列组件的同一存储单元。具体的,第一可编程门阵列组合1/第一专用集成电路阵列组件10以及第二可编程门阵列组合3/第二专用集成电路阵列组件30共用同一存储控制单元113访问第一存储阵列组件2的同一存储单元,以实现共享存储访问。本实施例以第一可编程门阵列组合1以及第二可编程门阵列组合3共用同一存储控制单元113访问第一存储阵列组件2的同一存储阵列,以实现共享存储访问为例进行说明。具体的,存储控制单元113可以设置于第一接口模块11上;存储控制单元113还可以设置于第二接口模块31上;或者,存储控制单元113还可以设置于第一存储阵列组件2上,具体不做限定。

71.具体的,在一实施例中,第一逻辑组件100还包括第一可编程逻辑单元,在一具体实施例中,第一可编程逻辑单元设置于第一可编程门阵列组件131和/或第一可编程门阵列组件132上,第一可编程逻辑单元连接存储控制单元113,并引出第一逻辑信号。第二可编程门阵列组合3包括第二可编程逻辑单元,具体的,第二可编程逻辑单元设置于第二可编程门阵列组件341和/或第二可编程门阵列组件342上,第二可编程逻辑单元连接存储控制单元113,并引出第二逻辑信号。存储控制单元113基于第一逻辑信号以及第二逻辑信号选择第

一可编程门阵列组合1访问第一存储阵列单元2或者选择第二可编程门阵列组合3访问第一存储阵列单元2。

72.具体的,如图6所示,图6以第一可编程门阵列组合1包括一个第一可编程门阵列组件,第二可编程门阵列组合3包括一个第二可编程门阵列组件为例进行说明。其中,存储控制单元h21设置在第一接口模块h17。具体的,第一存储阵列单元2上包括存储阵列单元g13,第二键合引出区域g14设置在存储阵列单元g13上,第一键合引出区域h19设置在第一接口模块h17上,且第一键合引出区域h19与第二键合引出区域g14键合连接。存储控制单元h21设置在第一接口模块h17上,且存储控制单元h21与第一键合引出区域h19连接。第一接口模块h17上还设置有第四键合引出区域h24,第四键合引出区域h24与存储控制单元h21连接。第二接口模块i27上设置有第三键合引出区域i28,第三键合引出区域i28与第四键合引出区域h24连接。进一步的,本实施例中,第一可编程门阵列组件上还包括第一可编程逻辑单元h23,第一可编程逻辑单元h23连接存储控制单元h21。第二可编程门阵列组件上还包括第二可编程逻辑单元i32,第二可编程逻辑单元i32,连接第三键合引出区域i28。

73.例如,在一实施例中,在第一可编程门阵列组件需要访问第一存储阵列组件2时,第一可编程逻辑单元h23引出第一逻辑信号至存储控制单元h21,此时,存储控制单元h21基于第一逻辑信号控制第一可编程门阵列组件通过第一键合引出区域h19、第二键合引出区域g14访问第一存储阵列组件2上的存储单元g13。在第二可编程门阵列组件需要访问第一存储阵列组件2时,第二可编程逻辑单元i32引出第二逻辑信号,第三键合引出区域i28、第四键合引出区域h24传输至存储控制单元h21。此时,存储控制单元h21基于第二逻辑信号控制第二可编程门阵列组件通过第三键合引出区域i28、第四键合引出区域h24访问第一存储阵列组件2上的存储单元g13。以此实现存储控制单元基于第一逻辑信号以及第二逻辑信号选择第一可编程门阵列组件访问第一存储阵列组件2或者第二可编程门阵列组件访问第一存储阵列组件2。

74.需要说明的是,上述第一可编程门阵列组件以及第二可编程门阵列组件可以替换为第一专用集成电路阵列组件以及第二专用集成电路阵列组件。

75.进一步的,上述第一可编程门阵列组件以及第二可编程门阵列组件的数量还可以为多个。多个第一可编程门阵列组件以及第二可编程门阵列组件对存储阵列组件的存储访问根据存储控制单元的数量而确定,具体如上述图4所述,在此不再赘述。

76.本实施例中,仅设计一个存储控制单元,存储控制单元可以位于第一接口模块h17上或附近,还可以位于第二接口模块i27上或附近,还可以位于第一存储阵列组件2上,具体不做限定。第一存储阵列组件2上的存储单元g13,通过第二键合引出区域g14和第一键合引出区域h19全部连接到存储控制单元h21,存储控制单元h21可直接连接两组存储访问接口(例如图5中的h19、h24),控制多组可编程门阵列组件通过该接口直接访问。

77.在一实施例中,第一可编程逻辑单元h23以及第二可编程逻辑单元i32包括可编程逻辑块、存储块、乘法单元、乘累加单元和硬核运算/处理单元等的任意组合。第一可编程逻辑单元h23引出第一逻辑信号,第二可编程逻辑单元i32引出第二逻辑信号。由存储控制单元h21根据第一逻辑信号以及第二逻辑信号,将存储控制单元h21的存储访问接口切换到第一键合引出区域h19和第二键合引出区域g14键合的方向,或者切换到第四键合引出区域h24和第三键合引出区域i28键合的方向,由第一可编程逻辑单元h23以及第二可编程逻辑

单元i32分时使用,实现了共享存储访问。

78.第一专用集成电路阵列组件10以及第二专用集成电路阵列组件30共用同一存储控制单元113访问第一存储阵列组件2的同一存储单元,以实现共享存储访问的方式与第一可编程门阵列组合1以及第二可编程门阵列组合3共享存储访问的方式相同,在此不再赘述。

79.需要说明的是,本实施例中,第三键合引出区域i28与接口路由单元i30连接。并且接口路由单元i30将第二可编程逻辑单元i32连接至第四键合引出区域h24。

80.本实施例中,共用存储控制单元,实现第一可编程逻辑单元h23和第二可编程逻辑单元i32对第一存储阵列组件2上大容量存储阵列的相同地址空间的存储访问,即共享存储访问,便于第一可编程逻辑单元h23和第二可编程逻辑单元i32之间的数据分享和同步,并且占用面积小。

81.在另一实施例中,第一逻辑组件100中的第一可编程门阵列组合1/第一专用集成电路阵列组件10以及第二逻辑组件200中的第二可编程门阵列组合3/第二专用集成电路阵列组件30分别利用独立的存储控制单元访问第一存储阵列组件2的存储单元。具体的,集成芯片包括第一存储控制单元以及第二存储控制单元,第一可编程门阵列组合1/第一专用集成电路单元10利用第一存储控制单元访问第一存储阵列单元2的存储单元。第二可编程门阵列组合3/第二专用集成电路单元30利用第二存储控制单元访问第一存储阵列单元2的存储单元。

82.在本实施例中,第二存储控制单元设置于第二接口模块31上或附近,第一存储控制单元设置于第一接口模块11上或附近。在本实施例中,第一逻辑组件100还包括第一可编程逻辑单元,具体的,第一可编程逻辑单元设置于第一可编程门阵列组合1上,第一可编程逻辑单元连接存储控制单元,引出第一逻辑信号。第二逻辑组件200还包括:第二可编程逻辑单元,具体的,第二可编程逻辑单元设置于第二可编程门阵列组合3上,第二可编程逻辑单元连接存储控制单元,引出第二逻辑信号。

83.响应于第一存储控制单元以及第二存储控制单元均控制第一存储阵列组件2的所有存储单元,且第一可编程门阵列组件以及第二可编程门阵列组件同时访问同一存储单元时,第一存储控制单元基于第一逻辑信号控制第一可编程门阵列组件在第一时间访问存储单元;第二存储控制单元基于第二逻辑信号控制第二可编程门阵列组件在第二时间访问存储单元。响应于第一存储控制单元以及第二存储控制单元分别控制第一存储阵列组件的不同存储单元,第一存储控制单元以及第二存储控制单元同时控制第一可编程门阵列组件以及第二可编程门阵列组件访问第一存储阵列组件2的不同存储单元。

84.具体的,本实施例中,若第一存储控制单元以及第二存储控制单元均控制第一存储阵列组件2的所有存储单元时,若第一可编程门阵列组件以及第二可编程门阵列组件同时访问同一存储单元时,第一存储控制单元以及第二存储控制单元分别控制第一可编程门阵列组件以及第二可编程门阵列组件访问该存储单元。具体的,第一存储控制单元基于第一逻辑信号控制第一可编程门阵列组件在第一时间访问存储单元,第二存储控制单元基于第二逻辑信号控制第二可编程门阵列组件在第二时间访问存储单元,实现不同可编程门阵列对同一个存储单元的分时访问,即消除访问冲突。

85.具体的,第一逻辑组件100可包含存储单元的仲裁逻辑,基于第一逻辑信号以及第

二逻辑信号,选择被第一逻辑组件100和第二逻辑组件200上的存储控制单元访问。具体的,当第一逻辑组件100的存储控制单元和第二逻辑组件200的存储控制单元分别同时访问第一存储阵列组件2的不同存储单元时,由于各自存储控制单元独立,第一逻辑组件100中的存储单元中的仲裁逻辑,基于第一逻辑信号以及第二逻辑信号,可以同时建立第一逻辑组件100的存储控制单元和第二逻辑组件200的存储控制单元对第一存储阵列组件2的存储单元的访问;当第一逻辑组件100的存储控制单元和第二逻辑组件200的存储控制单元分别同时访问第一存储阵列组件2的存储单元的相同区域时,第一逻辑组件100中的存储单元中的仲裁逻辑,基于第一逻辑信号以及第二逻辑信号,分时建立第一逻辑组件100的存储控制单元或第二逻辑组件200的存储控制单元访问。第一逻辑组件100中的存储单元的仲裁逻辑还可以设置在第一存储阵列组件2或第二逻辑组件200上。

86.在另一实施例中,在第一存储控制单元以及第二存储控制单元分别控制第一存储阵列组件的不同存储单元时,第一存储控制单元以及第二存储控制单元同时控制第一可编程门阵列组件以及第二可编程门阵列组件访问第一存储阵列组件2的不同存储单元。

87.具体的,当第一可编程门阵列组件的第一存储控制单元和第二可编程门阵列组件的第二存储控制单元分别同时访问第一存储阵列组件2的不同存储单元时,由于各自存储控制单元独立,第一可编程门阵列组件中的存储单元中的仲裁逻辑,基于第一逻辑信号以及第二逻辑信号,可以同时建立第一可编程门阵列组件的第一存储控制单元和第二可编程门阵列组件的第二存储控制单元对第一存储阵列组件2的存储单元的访问。

88.本实施例中,每个逻辑组件有独立存储访问接口,访存带宽最高,访问存储阵列的具体单元不同时,可以同时访问;写入存储阵列的共享区域,具体单元相同时出现冲突,需要仲裁和分时访问。具体的,在第一存储控制单元以及第二存储控制单元均控制第一存储阵列组件2的所有存储单元时,若同时访问同一存储单元时,则需要分时访问。在第一存储控制单元以及第二存储控制单元控制的存储单元不同时,则不需要分时访问。

89.在一实施例中,第二存储控制单元设置于第二接口模块31上或附近,第一存储控制单元设置于第一接口模块11上或附近。在本实施例中,第一存储控制单元基于第一逻辑信号控制第一可编程门阵列组件访问第一存储阵列组件2的部分存储单元;第二存储控制单元基于第二逻辑信号控制第二可编程门阵列组件访问第一存储阵列组件2的其余部分存储单元;第二可编程门阵列组件访问第一存储阵列组件2的存储单元与第一可编程门阵列组件访问区域不重叠。第一可编程逻辑单元利用第一存储控制单元,和第二可编程逻辑单元利用第二存储控制单元,独立同时访问各自对应的第一存储阵列组件2上不同存储单元。

90.本实施例中,每个逻辑组件有独立存储访问接口,访存带宽最高,访问切分第一存储阵列组件2给不同可编程逻辑单元利用存储控制单元组合;实现了不同可编程逻辑单元的并发存储访问,并无需因仲裁和分时访问而降低存储访问效率。

91.具体的,请参见图7,第一存储阵列组件2上包括存储阵列单元g13,其中,存储阵列单元g13上设置有两个第二键合引出区域,分别为第二键合引出区域g14以及第二键合引出区域g12。其中,第二键合引出区域g14连接到位于第一可编程门阵列组合1上的第一接口模块h17上的第一键合引出区域h19。第一可编程门阵列组合1的第一接口模块h17上设置有第一存储控制单元h20,第一存储控制单元h20用于控制第一可编程门阵列组合1访问第一存储阵列组件2。具体的,第一存储控制单元h20连接第一键合引出区域h19。第一可编程门阵

列组合1上设置有第一可编程逻辑单元h23,第一可编程逻辑单元h23通过接口路由单元h22连接至第一存储控制单元h20。在第一可编程门阵列组合1访问第一存储阵列组件2时,第一可编程逻辑单元h23引出第一逻辑信号至第一存储控制单元h20,第一存储控制单元h20基于第一逻辑信号控制第一可编程门阵列组合1通过第一键合引出区域h19、第二键合引出区域g14访问第一存储阵列组件2的部分存储单元单元g13。

92.另外,第二键合引出区域g12连接到第一接口模块h17上的第一键合引出区域h18上,第一键合引出区域h18与第二可编程门阵列组合3上的第三键合引出区域i28连接。第二可编程门阵列组合3还包括第二可编程逻辑单元i32,第二可编程逻辑单元i32通过接口路由单元i31连接位于第二可编程门阵列组合3的第二接口模块i27上的第二存储控制单元i29。在第二可编程门阵列组合3访问第一存储阵列组件2时,第二可编程逻辑单元i32引出第二逻辑信号至第二存储控制单元i29,第二存储控制单元i29基于第二逻辑信号控制第二可编程门阵列组合3通过第三键合引出区域i28、第一键合引出区域h18、第二键合引出区域g14访问第一存储阵列组件2的其余部分存储单元单元g13。

93.通过图7所示的连接方式实现第一可编程门阵列组合1以及第二可编程门阵列组合3对第一存储阵列组件2的独立存储访问。

94.第一专用集成电路阵列组件10以及第二专用集成电路阵列组件30利用不同的存储控制单元访问第一存储阵列组件2的不同的存储单元,以实现独立存储访问的方式与第一可编程门阵列组合1以及第二可编程门阵列组合3独立存储访问的方式相同,在此不再赘述。

95.需要说明的是,本技术的第一可编程门阵列组件以及第二可编程门阵列组件可以为fpga(现场可编程门阵列)或者efpga(非易失性现场可编程门阵列)。在一优选实施例中,第一可编程门阵列组件以及第二可编程门阵列组件为fpga(现场可编程门阵列)或efpga(嵌入式现场可编程门阵列)。

96.本实施例的集成芯片中,第二可编程门阵列组件对第一存储阵列组件的存储访问不经过io接口和/或io电路,使得互连距离更近,互连分布参数更低、存储访问的功耗开销显著降低。芯片制造过程中,可以同时生产第二可编程门阵列组件以及第一可编程门阵列组件,并且在将第二可编程门阵列组件与第一可编程门阵列组件键合后再与第一存储阵列组件2键合,能够降低工艺复杂度,节省成本。但是第二可编程门阵列组件对第一存储阵列组件2的存储访问需要经过第一接口模块11以及第二接口模块31,会造成轻微面积损失。

97.通过上述说明可知,本实施例的集成芯片中,第二可编程门阵列组合3/第二专用集成电路阵列组件30以及第一可编程门阵列组合1/第一专用集成电路阵列组件10对第一存储阵列组件2的存储访问不经过io接口,通过三维异质键合的连接,使得互连距离更近,存储访问的功耗开销显著降低。

98.在芯片制造过程中,可以同时生产第一逻辑组件100以及第二逻辑组件200,并且将第一逻辑组件100以及第二逻辑组件200键合并测试后再与第一存储阵列组件2键合,能够降低工艺复杂度,节省成本。这种结构第二逻辑组件200对第一存储阵列组件2的存储访问需要经过第一接口模块11以及第二接口模块31,这可能会造成一些功耗损失。

99.本技术还提出另一实施例,该实施例中,第二逻辑组件200设置于第一存储阵列组件2远离第一逻辑组件100的一侧。也即第一存储阵列组件2设置于第一逻辑组件100以及第

二逻辑组件200之间。其中,第一存储阵列组件2包括第四键合引出区域,第三键合引出区域311与第四键合引出区域构成三维异质集成互连。本实施例中,第二逻辑组件100以及第二逻辑组件200均能够实现与存储阵列组件2的直接互连,有利于更大的存储访问带宽。

100.本实施例中,第一逻辑组件100对第一存储阵列组件2的存储访问只需要经过第一接口模块11,且第二逻辑组件200对第一存储阵列组件2的存储访问只需要经过第二接口模块31。这种结构使得第二逻辑组件200与第一存储阵列组件2之间的互连距离更近,能够进一步降低存储访问功耗。但是这种结构的集成芯片在制备过程中,需要先将第一逻辑组件100与第一存储阵列组件2进行键合,再与第二逻辑组件200进行键合。

101.请参见图8,为本发明集成芯片的第三实施例的结构示意图,与上述图2所示的第一实施例相比,区别在于,本实施例的集成芯片还包括:第二存储阵列组件4。第二存储阵列组件4设置于第一存储阵列组件2远离第一逻辑组件100的一侧,第二存储阵列组件4设置有第三键合引出区域311,本实施例中,第一存储阵列组件2包括第四键合引出区域32,第三键合引出区域311与第四键合引出区域32构成三维异质集成互连。

102.本实施例中,集成更多的存储阵列组件,有利于增加存储密度,实现更大的存储访问带宽。本实施例中,集成更多的存储阵列组件,有利于增加存储密度,将多个存储阵列组件统一生产和测试构成标准产品后,与逻辑组件集成,有利于降低成本。

103.在一实施例中,第一可编程门阵列组件共用同一存储控制单元访问第一存储阵列组件2和第二存储阵列组件4。具体的,在第一可编程门阵列组件共用同一存储控制单元访问第一存储阵列组件2和第二存储阵列组件4,为了避免访问冲突,存储控制单元可以分时选择性的选择第一可编程门阵列组件访问第一存储阵列组件2或者第二存储阵列组件4。

104.具体请参见10,本实施例中,集成芯片还包括存储控制单元h21,存储控制单元h21设置于第一接口模块h17上。本实施例中,第一接口模块h17包括两个第一键合引出区域,分别为第一键合引出区域h19以及第一键合引出区域h18。第一存储阵列组件2上设置多个存储单元g13,存储单元g13上有两个第二键合引出区域,分别为第二键合引出区域g12以及第二键合引出区域g14。第二存储阵列组件4上设置有多个存储单元f01,存储单元f01上设置有第三键合引出区域i28。

105.具体的,第一键合引出区域h18连接第二键合引出区域g14。存储控制单元h21连接第一键合引出区域h18。以此,存储控制单元h21可以通过第一键合引出区域h18、第二键合引出区域g14控制第一可编程门阵列组件访问第一存储阵列组件2。

106.第一键合引出区域h19连接第二键合引出区域g12,第二键合引出区域g12连接第三键合引出区域i28。以此,存储控制单元h21可以通过第一键合引出区域h19、第二键合引出区域g12、第三键合引出区域i28控制第一可编程门阵列组件访问第二存储阵列组件4。需要说明的是,第二键合引出区域g12不连接存储单元g13。

107.本实施例中,第一可编程门阵列组件还包括可编程逻辑单元k23,可编程逻辑单元k23通过接口路由单元h22连接存储控制单元h21,可编程逻辑单元k23引出逻辑信号。存储控制单元h21基于逻辑信号分时选择性的控制第一可编程门阵列组件访问第一存储阵列组件2,或者控制第一可编程门阵列组件访问第二存储阵列组件4。具体的,在存储控制单元h21基于逻辑信号,在第一时间控制第一可编程门阵列组件访问第一存储阵列组件2,在第二时间控制第一可编程门阵列组件访问第二存储阵列组件4。

108.在一实施例中,第一可编程门阵列组件分别利用两个不同的存储控制单元访问第一存储阵列组件2和第二存储阵列组件4。具体的,在第一可编程门阵列组件分别利用两个不同的存储控制单元访问第一存储阵列组件2和第二存储阵列组件4,由于不存在访问冲突,存储控制单元可以同时控制第一可编程门阵列组件访问第一存储阵列组件2,并控制第一可编程门阵列组件访问第二存储阵列组件4。具体的,第一存储控制单元控制第一可编程门阵列组件访问第一存储阵列组件2,第二存储控制单元控制第一可编程门阵列组件访问第二存储阵列组件4。

109.具体请参见图10,本实施例中,集成芯片还包括第一存储控制单元h20以及第二存储控制单元i29,第一存储控制单元h20以及第二存储控制单元i29设置于第一接口模块h17上。本实施例中,第一接口模块h17包括两个第一键合引出区域,分别为第一键合引出区域h19以及第一键合引出区域h18。第一存储阵列组件2上设置多个存储单元g13,存储单元g13上有两个第二键合引出区域,分别为第二键合引出区域g12以及第二键合引出区域g14。第二存储阵列组件4上设置有多个存储单元f01,存储单元f01上设置有第三键合引出区域i28。

110.本实施例中,第一存储控制单元h20连接第一键合引出区域h18,第一键合引出区域h18连接第二键合引出区域g14。以此,第一存储控制单元h18可以通过第一键合引出区域h18、第二键合引出区域g14控制第一可编程门阵列组件访问第一存储阵列组件2。

111.进一步的,第二存储控制单元i29连接第一键合引出区域h19,第一键合引出区域h19连接第二键合引出区域g12,第二键合引出区域g12连接第三键合引出区域i28。以此,第二存储控制单元i29可以通过第一键合引出区域h19、第二键合引出区域g12、第三键合引出区域i28控制第一可编程门阵列组件访问第二存储阵列组件4。需要说明的是,第二键合引出区域g12不连接存储单元g13。

112.本实施例中,第一可编程门阵列组件还包括:可编程逻辑单元k23,可编程逻辑单元k23连接第一存储控制单元h20和第二存储控制单元i29,可编程逻辑单元k23引出逻辑信号。具体的,可编程逻辑单元k23通过接口路由单元h22分别连接第一存储控制单元h20和第二存储控制单元i29。本实施例中,第一存储控制单元h20基于逻辑信号控制第一可编程门阵列组件访问第一存储阵列组件2,第二存储控制单元i29同时基于逻辑信号控制第一可编程门阵列组件访问第二存储阵列组件4。

113.本技术还提出另一实施例,该实施例中,多个存储阵列组件对至少一个可编程门阵列组件,通过混合使用图9和图10方法设计复用或独立存储控制单元,实现混合存储访问。在同一个集成芯片中,部分区域的可编程逻辑单元,使用图9所示复用存储控制单元实现存储访问;部分区域的可编程逻辑单元使用图10所示独立存储控制单元实现存储访问。

114.在另一实施例中,如图11所示,第二存储阵列组件4还可以设置于第一逻辑组件100远离第一存储阵列组件2的一侧。其中,第二存储阵列组件4设置有第三键合引出区域311,第一接口模块11包括第四键合引出区域32,第三键合引出区域311与第四键合引出区域32构成三维异质集成互连。

115.本实施例中,集成更多的存储阵列组件,有利于增加存储密度,将多个存储阵列组件统一生产和测试构成标准产品后,与逻辑组件集成,有利于降低成本。并且由于第一存储阵列组件2与第二存储阵列组件4直接与第一可编程门阵列组件连接,减少三维异质集成中

专,互连距离更近,存储访问距离短,分布参数小,存储访问频率和功耗最优。

116.在一实施例中,第一可编程门阵列组件共用同一存储控制单元访问第一存储阵列组件2和第二存储阵列组件4。具体的,在第一可编程门阵列组件共用同一存储控制单元访问第一存储阵列组件2和第二存储阵列组件4,为了避免访问冲突,存储控制单元可以分时选择性的选择第一可编程门阵列组件访问第一存储阵列组件2或者第二存储阵列组件4。

117.具体请参见12,本实施例中,集成芯片还包括存储控制单元h21,存储控制单元h21设置于第一接口模块h17上。本实施例中,第一接口模块h17包括两个第一键合引出区域,分别为第一键合引出区域h19以及第一键合引出区域h18。第一存储阵列组件2上设置多个存储单元g13,存储单元g13上有第二键合引出区域g14。第二存储阵列组件4上设置有多个存储单元f01,存储单元f01上设置有第三键合引出区域i28。

118.具体的,第一键合引出区域h18连接第二键合引出区域g14。存储控制单元h21连接第一键合引出区域h18。以此,存储控制单元h21可以通过第一键合引出区域h18、第二键合引出区域g14控制第一可编程门阵列组件访问第一存储阵列组件2。

119.存储控制单元h21可以通过第一键合引出区域h19,第一键合引出区域h19连接第三键合引出区域i28。以此,存储控制单元h21可以通过第一键合引出区域h19、第三键合引出区域i28控制第一可编程门阵列组件访问第二存储阵列组件4。

120.本实施例中,第一可编程门阵列组件还包括可编程逻辑单元k23,可编程逻辑单元k23通过接口路由单元h22连接存储控制单元h21,可编程逻辑单元k23引出逻辑信号。存储控制单元h21基于逻辑信号分时选择性的控制第一可编程门阵列组件访问第一存储阵列组件2,或者控制第一可编程门阵列组件访问第二存储阵列组件4。具体的,在存储控制单元h21基于逻辑信号,在第一时间控制第一可编程门阵列组件访问第一存储阵列组件2,在第二时间控制第一可编程门阵列组件访问第二存储阵列组件4

121.在一实施例中,第一可编程门阵列组件分别利用两个不同的存储控制单元访问第一存储阵列组件2和第二存储阵列组件4。具体的,在第一可编程门阵列组件分别利用两个不同的存储控制单元访问第一存储阵列组件2和第二存储阵列组件4,由于不存在访问冲突,存储控制单元可以同时控制第一可编程门阵列组件访问第一存储阵列组件2,并控制第一可编程门阵列组件访问第二存储阵列组件4。具体的,第一存储控制单元控制第一可编程门阵列组件访问第一存储阵列组件2,第二存储控制单元控制第一可编程门阵列组件访问第二存储阵列组件4。

122.具体请参见图13,本实施例中,集成芯片还包括第一存储控制单元h20以及第二存储控制单元i29,第一存储控制单元h20以及第二存储控制单元i29设置于第一接口模块h17上。本实施例中,第一接口模块h17包括两个第一键合引出区域,分别为第一键合引出区域h19以及第一键合引出区域h18。第一存储阵列组件2上设置多个存储单元g13,存储单元g13上有第二键合引出区域g14。第二存储阵列组件4上设置有多个存储单元f01,存储单元f01上设置有第三键合引出区域i28。

123.本实施例中,第一存储控制单元h20连接第一键合引出区域h18,第一键合引出区域h18连接第二键合引出区域g14。以此,第一存储控制单元h18可以通过第一键合引出区域h18、第二键合引出区域g14控制第一可编程门阵列组件访问第一存储阵列组件2。

124.进一步的,第二存储控制单元i29连接第一键合引出区域h19,第一键合引出区域

h19连接第三键合引出区域i28。以此,第二存储控制单元i29可以通过第一键合引出区域h19、第三键合引出区域i28控制第一可编程门阵列组件访问第二存储阵列组件4。

125.本实施例中,第一可编程门阵列组件还包括:可编程逻辑单元k23,可编程逻辑单元k23连接第一存储控制单元h20和第二存储控制单元i29,可编程逻辑单元k23引出逻辑信号。具体的,可编程逻辑单元k23通过接口路由单元h22分别连接第一存储控制单元h20和第二存储控制单元i29。本实施例中,第一存储控制单元h20基于逻辑信号控制第一可编程门阵列组件访问第一存储阵列组件2,第二存储控制单元i29同时基于逻辑信号控制第一可编程门阵列组件访问第二存储阵列组件4。

126.本技术还提出另一实施例,该实施例中,多个存储阵列组件对至少一个可编程门阵列组件,通过混合使用图12和图13方法设计复用或独立存储控制单元,实现混合存储访问。在同一个集成芯片中,部分区域的可编程逻辑单元,使用图12所示复用存储控制单元实现存储访问;部分区域的可编程逻辑单元使用图13所示独立存储控制单元实现存储访问。

127.本技术中,存储阵列组件可以是多层芯片,通过三维异质集成键合的组合;专用集成电路阵列组件可以设置乘加计算阵列、乘法计算阵列、脉动处理器阵列、哈希计算阵列、多种编码器阵列、机器学习的专用层阵列、检索功能阵列、图像/视频处理阵列以及cpu和mcu等硬核运算/处理单元的一种或多种任意组合,用于与编程门阵列组件组合使用,提高集成芯片的处理密度。

128.具体的,组件可以为晶粒(die或者chip)、晶圆(wafer)中至少一种,但不以此为限,也可以是本领域技术人员所能想到的任何替换。其中,晶圆(wafer)是指制作硅半导体电路所用的硅晶片,芯片或晶粒(chip or die)是指将上述制作有半导体电路的晶圆进行分割后的硅晶片。例如,本技术的存储阵列组件可以为存储阵列晶粒(dram die或者dram chip)、存储阵列晶圆(dram wafer)。

129.本技术提供的集成芯片中,可编程门阵列组件以及专用集成电路阵列组件对存储阵列组件的存储访问不经过io接口,使得互连距离更近,存储访问的功耗开销显著降低。并且通过三维异质集成键合的方式实现了高宽带、低功耗的可编程存储一体结构。

130.基于与方法同样的发明构思,本发明实施例还提供了一种三维异质集成的集成芯片结构。该集成芯片上设有层次化堆叠组件,通过三维异质集成互连,这些组件可以为上文任一组件。在该集成芯片进行制备时,还可以,直接以晶圆(wafer)为单位进行制备,以及进行三维异质集成。

131.在集成芯片进行制备时,还可以,部分以晶圆(wafer)为单位进行制备,并及进行三维异质集成,具体有两种方法:先将部分晶圆层进行三维异质集成后,形成中间产品,再将其余晶圆层与中间产品进行上述迭代,直至完成制备;或先将部分晶圆层进行三维异质集成后,形成中间产品,后将中间产品切割成晶粒(die),与其它组件的晶粒进行晶粒对晶粒的三维异质集成,完成制备。

132.具体的,图5所述多层可编程门阵列组件与至少一层存储阵列组件组成集成芯片的制备过程有两种方法:将多层可编程门阵列组件以晶圆为单位,进行三维异质集成,形成中间产品,以提高互连密度,将中间产品,再与至少一层存储阵列组件形成的中间产品,进行三维异质集成,得到集成芯片;或者,将多层可编程门阵列组件以晶圆为单位,进行三维异质集成,形成中间产品,将中间产品切割成晶粒并测试后,再与至少一层存储阵列组件形

成的切割测试后的中间产品,进行晶粒对晶粒的集成,得到集成芯片,因为成品来源于切割和测试后的组件的三维异质集成,良率得到显著提高。

133.同样的,图8所述多层存储阵列组件与至少一层可编程门阵列组件组成集成芯片的制备过程有两种方法:将多层存储阵列组件以晶圆为单位,进行三维异质集成,形成中间产品,以提高互连密度,将中间产品,再与至少一层可编程门阵列组件形成的中间产品,进行三维异质集成,得到集成芯片;或者,将多层存储阵列组件以晶圆为单位,进行三维异质集成,形成中间产品,将中间产品切割成晶粒并测试后,再与至少一层可编程门阵列组件形成的切割测试后的中间产品,进行晶粒对晶粒的集成,得到集成芯片,因为成品来源于切割和测试后的组件的三维异质集成,良率得到显著提高。

134.集成芯片的可编程门阵列组件和存储阵列组件的层次数量和层次顺序,取决于应用场景、工程需求以及生产成本和生产良率的复杂博弈,所得最优结果不单一。不同层次数量和层次顺序的不同目标产品,所需生产制备工艺也是多样化的,并且对存储控制器的设计和复用设计存在有明显差异。

135.可编程门阵列组件中,可编程功能模块与可编程路由网络的广泛互连,参见图14,可编程门阵列组件基于现场可编程逻辑门阵列(field

‑

programmablegatearray,fpga/embedded field

‑

programmable gate array,efpga)技术的扩展,可编程门阵列组件包括可编程逻辑块11a和可编程路由网络11b(interconnect);可编程逻辑块11a通过路由网络11b而彼此互联而被配置为若干可编程功能模块,且可编程路由网络11b的至少一部分可扩展至接口路由单元,进而通过三维异质集成,跨层次互连大容量存储阵列,形成大容量、高带宽、可编程存储访问。

136.三维异质集成是一种层叠芯片互连键合的技术,例如混合键合(hybrid bonding)工艺等。通过在已制备的芯片(例如可编程门阵列组件或存储阵列组件)基础上,利用后道工序(beol)制造的三维异质集成键合层,实现芯片之间信号的高密度互连,制备得到集成芯片。

137.具体以图15为例说明。图15中,集成芯片包含功能组件210、功能组件220和功能组件230,功能组件210、功能组件220和功能组件230可以为可编程门阵列组件和/或存储阵列组件。功能组件210、功能组件220和功能组件230均包含顶层金属层、内部金属层有源层和衬底,其中,顶层金属层和内部金属层用于组件内信号互连;有源层用于实现晶体管,组成模块功能;衬底用于保护模块及提供机械支撑等。功能组件210和功能组件220上接近顶层金属层一面,通过后道工序制造三维异质集成键合层,并互连,形成面对面的互连结构;功能组件220上接近衬底一面和功能组件230上接近顶层金属层一面,通过后道工序制造三维异质集成键合层,并互连,形成背对面(或面对背)的互连结构。功能组件210、功能组件220和功能组件230之间,可以任意通过三维异质集成建立跨组件信号互连。区别于功能组件210、功能组件220和功能组件230的内核电压是否相同,对应两种互连技术。

138.当功能组件210和功能组件230的内核电压相同时,以功能组件210中的功能电路1,需要与功能组件230中的功能电路10建立跨组件互连为例:功能电路1在功能组件210中内部金属层的引出信号,通过功能组件210的顶层金属,连接功能组件210与功能组件220之间的面对面三维异质集成键合结构,进而与功能组件220的顶层金属互连;互连信号,通过功能组件220的内部金属层,以及贯穿功能组件220的有源层和减薄衬底的硅通孔(tsv),互

连至功能组件220与功能组件230之间的背对面三维异质集成键合结构,进而互连至功能组件230的顶层金属层;互连信号通过功能组件230的内部金属层,实现跨组件互连功能组件230中的功能电路10。

139.当功能组件210和功能组件230的内核电压不同时候,以功能组件中的功能电路2,需要与功能组件230中的功能电路10建立跨组件互连为例:在功能组件210中设计电平转换电路2,电平转换电路2与功能电路2在功能组件210中互连;电平转换电路2将功能电路2的互连信号转换成匹配功能组件230的内核电压后,使用前述方法跨组件互连至功能组件230中的功能电路20。并且,电平转换电路2也可以通过三维异质集成互连,被转移设计到功能模块230或功能模块220中。

140.本技术提供的集成芯片中,可编程门阵列组件以及专用集成电路阵列组件对存储阵列组件的存储访问不经过io接口和/或io电路,使得互连距离更近,存储访问的功耗开销显著降低。并且通过三维异质集成键合的方式实现了高宽带、低功耗的可编程存储一体结构。

141.以上仅为本发明的实施方式,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1