一种超大规模FPGA芯片的数据配置和回读方法与流程

一种超大规模fpga芯片的数据配置和回读方法

技术领域

1.本发明涉及一种超大规模fpga芯片的数据配置和回读方法,属于电子信息技术领域。

背景技术:

2.sram(static random access memory,即静态随机存取存储器)型fpga(field programmable gate array,即现场可编程门阵列)由于具有可编程性,内部资源丰富,包括丰富的接口类型,上亿门的逻辑资源,计算能力的多样性优势,在数据中心领域占据着硬件加速器的作用,并成为数据中心的关键核心器件。

3.传统的配置流程由4个主要的步骤组成,它们分别是清零(clearing configuration memory)、初始化(initialization)、装载配置数据(loading configuration data)和芯片启动(device startup)。(1)fpga芯片上电后配置控制器首先封锁全片的io,然后冻结芯核,随后对片内的cram逐行进行清零。对cram清零的目的是使cram被初始化为确定的数值,以防其不确定的输出值引起不期望的短路或其他问题,消除电路中的不确定性。(2)在初始化阶段中,fpga对配置模式选择进行采样,准备装载数据。(3)装载配置数据在这一步骤中,配置控制器内的状态机根据输入的码流进行跳转,从码流中解出配码并将它们送到相应的可配置逻辑单元。(4)配置控制器完成全部配置后,将芯核解冻,done拉高,用户电路开始运行。

4.传统的回读流程为用户将done信号拉低,并且在done的低电平期间送入回读命令。每送入一条回读命令,器件就将对应的cram配码一次性读出。回读结束后,用户将done释放为高电平,则器件自动执行后续的解冻操作。

5.而随着fpga芯片逻辑资源规模越来越大,配置数据量非常巨大,而由于配置控制器直接控制cram模块,两者之间存在配置数据传输的瓶颈,配置时间成本高,降低了fpga芯片配置和回读的整体性能。

技术实现要素:

6.本发明要解决的技术问题是:随着fpga芯片逻辑资源的规模越来越大,配置数据越来越多,导致的配置和回读阶段的时间过长,芯片性能下降的问题。

7.为了解决上述技术问题,本发明提出的技术方案是:一种超大规模fpga芯片的数据配置和回读方法:a.配置阶段,步骤1、预取数据更新模块接收配置控制器发出的方向信息、位置信息,并开始计数预取一帧的配置数据;步骤2、当预取数据更新模块接收完成一帧配置数据时,向配置数据存储模块发送写使能信号,并将一帧预取数据在一个时钟周期内输出到配置数据存储器;步骤 3、配置数据存储模块写方向写入配置控制器发出的位置信息和一帧预取配

置数据;配置数据存储模块读方向输出配置处理模块所需要的当前帧的配置数据;步骤4、配置处理模块接收来自配置数据存储模块的当前帧配置数据,接收来自配置控制器关于当前帧的位置信息,向相应的cram发出写使能控制并将整理好的配置数据发送到各个cram位单元;b.回读阶段,步骤1、配置处理模块接收配置控制器发出的方向信息、位置信息,并从打开相应cram位单元读使能写入回读数据,并将回读数据进行整理按照帧格式向预取数据更新模块输出回读数据;步骤2、当预取数据更新模块接收完成一帧回读数据时,向配置数据存储模块发送写使能信号,并将一帧预取数据在一个时钟周期内输出到配置数据存储器;步骤 3、配置数据存储模块写方向写入配置控制器发出的位置信息和一帧预取配置数据;配置数据存储模块读方向输出配置控制器模块所需要的当前帧的回读数据;步骤4、配置控制器模块接收来自配置数据存储模块的当前帧回读数据。

8.本发明的有益效果是:不采用常规的直接将配置控制器与cram直接对接的方式,在两者之间架设中间模块,并通过中间模块实现二者数据交互的缓冲。该方法以帧为单位,逐帧配置和回读数据,因此支持部分帧重配置和非连续重配置,较于常规的完全读取配置更为高效。

附图说明

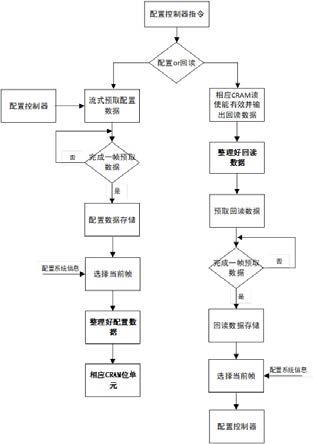

9.图1是本发明实施例一的一种超大规模fpga芯片的数据配置和回读方法的流程示意图。

10.图2是本发明实施例一的一种超大规模fpga芯片的数据配置和回读方法的所使用装置的结构示意图。

11.图3是本发明实施例一的一种超大规模fpga芯片的数据配置和回读方法中预取数据更新结构框图。

12.图4是本发明实施例一的一种超大规模fpga芯片的数据配置和回读方法中配置数据存储示意图。

具体实施方式

13.实施例一一种超大规模fpga芯片的数据配置和回读方法,如图1所示,a.配置阶段,步骤1、预取数据更新模块接收配置控制器发出的方向信息、位置信息,并开始计数预取一帧的配置数据;步骤2、当预取数据更新模块接收完成一帧配置数据时,向配置数据存储模块发送写使能信号,并将一帧预取数据在一个时钟周期内输出到配置数据存储器;步骤 3、配置数据存储模块写方向写入配置控制器发出的位置信息和一帧预取配置数据;配置数据存储模块读方向输出配置处理模块所需要的当前帧的配置数据;步骤4、配置处理模块接收来自配置数据存储模块的当前帧配置数据,接收来自配

置控制器关于当前帧的位置信息,向相应的cram发出写使能控制并将整理好的配置数据发送到各个cram位单元;b.回读阶段,步骤1、配置处理模块接收配置控制器发出的方向信息、位置信息,并从打开相应cram位单元读使能写入回读数据,并将回读数据进行整理按照帧格式向预取数据更新模块输出回读数据;步骤2、当预取数据更新模块接收完成一帧回读数据时,向配置数据存储模块发送写使能信号,并将一帧预取数据在一个时钟周期内输出到配置数据存储器;步骤 3、配置数据存储模块写方向写入配置控制器发出的位置信息和一帧预取配置数据;配置数据存储模块读方向输出配置控制器模块所需要的当前帧的回读数据;步骤4、配置控制器模块接收来自配置数据存储模块的当前帧回读数据。

14.本实施例中的各模块集成于缓冲装置中,包括原先的fpga芯片配置控制器和cram位单元,并在二者之间设置了预取数据更新模块、配置数据存储和配置处理模块,以便在配合和回读过程中为二者提供缓存空间。如图2所示,该装置包括配置控制器、预取数据更新模块、配置数据存储、配置处理模块和cram位单元。其中,配置控制器模块不仅用于对fpga全芯片的配置控制,还用于对整个高效配置回读缓冲装置进行控制,同时,在配置阶段对所述预取数据更新模块提供相应的预取数据,在回读阶段回读数据从所述预取数据更新模块送回配置控制器;预取数据更新模块用于根据配置控制器提供的系统信息接收预取的配置数据;配置数据存储用于配置处理模块所需要的配置数据;配置处理模块用于控制配置数据传输到cram位单元;cram位单元用于存储有效的配置位流码信息。

15.本实施例的预取数据更新结构框图如图3所示。m和n的值取决于芯片配置数据一帧的结构。配置方向数据从最左列m个pe单元左侧同时进入,回读方向数据从左列m个pe单元上方同时进入,经过n个周期的脉动传播,将一帧的数据进行输出。

16.本市实施例的的配置数据存储示意图如图4所示。作为配置数据存储模块,存储了当前帧和预取数据帧.在存储空间允许的情况下可存放多帧预取数据,保证整个配置回读过程中的满效率。

17.本发明不局限于上述实施例所述的具体技术方案,除上述实施例外,本发明还可以有其他实施方式。对于本领域的技术人员来说,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等形成的技术方案,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1