基于高层次综合的神经网络卷积FPGA嵌入式硬件加速器

基于高层次综合的神经网络卷积fpga嵌入式硬件加速器

技术领域

1.本发明涉及一种硬件加速器。特别是涉及一种基于高层次综合的神经网络卷积fpga嵌入式硬件加速器。

背景技术:

2.近些年来,基于神经网络的深度学习技术在人工智能领域大放异彩。其在图形分类、目标识别、语音处理等多个应用场景下性能优异,表现出色,已经成为越来越多人关注和研究的重要技术。深度学习技术一个重要特点是运算量特别巨大且有不断增长的趋势,其中的卷积运算占了很大一部分,用来执行通用逻辑运算的cpu(central processing unit,中央处理器)已经不能应付如此庞大的任务。目前,比较常用的处理方法是利用gpu(graphic processing unit,图形处理器)、asic(application specific integrated circuit,专用集成电路)和fpga(field

‑

programmable gate array,现场可编程门阵列)来进行专门的神经网络计算。在计算和存储资源都很有限的嵌入式移动平台上,gpu和asic有高成本、灵活性地、可扩展性差等缺点。

3.fpga是一种硬件可编程的集成电路,其可以根据使用场景和技术特点对电路进行定制化的配置,具有极高的灵活性。hls(high level synthesis)是一种通过c/c++语言描述算法和并行方式,由编译器直接生成硬件ip的电路设计方法,具有开发周期短、迭代速度快等优点。用hls方式进行fpga设计神经网络卷积硬件加速器并部署在嵌入式移动平台上是解决问题的有效方案。

4.然而,目前国内外对于此领域的技术方案存在一些问题。对于有很多卷积层的神经网络,现有技术要么把每一层都用单独的fpga电路资源去计算,这会耗费大量的硬件资源,且在资源紧张的嵌入式平台难以实现;要么用单一的硬件电路执行所有层的卷积计算,但这时的和外部存储器的数据交换速度成了性能瓶颈。

5.因此,为了进一步在嵌入式平台上调高神经网络卷积计算的速度、节约fpga硬件资源,本发明提出一种通用的、能处理所有卷积层运算的硬件加速器,并利用dma(direct memory access,直接内存存取)和axi

‑

stream技术相结合的方法提升数据交换速度的结构。

技术实现要素:

6.本发明所要解决的技术问题是,提供一种具有实现难度低、开发周期短、迭代速度快等优点的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器。

7.本发明所采用的技术方案是:一种基于高层次综合的神经网络卷积fpga嵌入式硬件加速器,包括,直接存取控制器、axi4总线接口协议、用于存放高并行卷积核与特征图数据的高并行缓存区、卷积计算器、用于存放分段式卷积结果的分段式缓存区、缓存区控制器和状态控制器;其中,所述axi4总线接口协议与所述直接存取控制器之间通过总线fifo做为一级缓存,所述直接存取控制器与外部存储器和处理器通过总线连接,所述直接存取控

制器通过一级缓存和总线分别与所述高并行缓存区和分段式缓存区连接;所述缓存区控制器分别连接高并行缓存区和分段式缓存区用于控制高并行缓存区和分段式缓存区的读写使能和地址操作,所述状态控制器分别连接外部存储器和处理器、卷积计算器和缓存区控制器,用于根据处理器的使能信号控制卷积计算器和缓存区控制器的工作,所述高并行缓存区、卷积计算器和分段式缓存区依次连接。

8.本发明的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器,采用通用卷积加速器设计和dma结合axi

‑

stream的技术,在嵌入式移动平台上显著提高计算性能并降低资源占用。本发明能在计算资源和存储资源都非常有限的嵌入式平台设备上高性能地执行神经网络中卷积层的计算,从而使得功能强大的神经网络在该类设备上流畅运行。同时,本发明几乎适用于所有以卷积为主要计算的神经网络,具有很大的通用性。本发明在嵌入式fpga异构平台zynq

‑

7000系列上得到验证,在该平台上测试mobilenet+ssd目标检测神经网络,得到了较高的准确度和预测性能。

附图说明

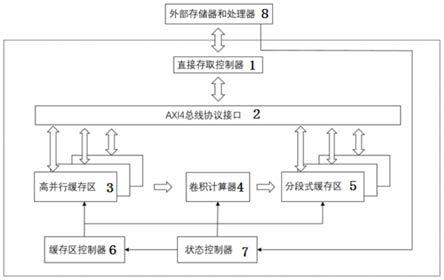

9.图1是本发明基于高层次综合的神经网络卷积fpga嵌入式硬件加速器的构成框图;

10.图2是本发明中卷积核大小为3

×

3的卷积计算过程示意图;

11.图3是本发明中卷积计算器的计算过程示意图。

具体实施方式

12.下面结合实施例和附图对本发明的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器做出详细说明。

13.如图1所示,本发明的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器,包括,直接存取控制器1、axi4总线接口协议2、用于存放高并行卷积核与特征图数据的高并行缓存区3、卷积计算器4、用于存放分段式卷积结果的分段式缓存区5、缓存区控制器6和状态控制器7;其中,所述axi4总线接口协议2与所述直接存取控制器1之间通过总线fifo(先入先出队列)做为一级缓存,所述直接存取控制器1与外部存储器和处理器8通过总线连接,所述直接存取控制器1通过一级缓存和总线分别与所述高并行缓存区3和分段式缓存区5连接;所述缓存区控制器6分别连接高并行缓存区3和分段式缓存区5用于控制高并行缓存区3和分段式缓存区5的读写使能和地址操作,所述状态控制器7分别连接外部存储器和处理器8、卷积计算器4和缓存区控制器6,用于根据处理器8的使能信号控制卷积计算器4和缓存区控制器6的工作,所述高并行缓存区3、卷积计算器4和分段式缓存区5依次连接。

14.axi总线是一种嵌入式设备常用的高性能高扩展的通用总线结构,本发明的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器挂载在axi总线上,使其能在支持该总线的移动平台上使用,其中,axi4总线接口协议具有逻辑简单、信号精简等特点,适合与嵌入式设备的cpu相连,由cpu发出控制信号给卷积计算器,来控制卷积计算器的运行、停止等。

15.本发明的基于高层次综合的神经网络卷积fpga嵌入式硬件加速器中:

16.所述的直接存取控制器1为硬件加速器和外部存储器和处理器8进行通信,直接存

取控制器1和处理器8均遵循axi4总线协议,数据接收和发送均经过直接存取控制器1缓冲,输入和输出均由fpga中的fifo提供数据流缓存。

17.所述的高并行缓存区3是由64个特征图缓存区,64个卷积核缓存区共同构成,在存储数据时数据是串行依次进入对应的缓存区,读出数据时使用统一的地址并行读出数据。

18.所述的分段式缓存区5是由fpga中的63个fifo(先入先出队列)组成,其中63个fifo分为6个组,依次为32个一组、16个一组、8个一组、4个一组、2个一组、1个一组,以存放所述卷积计算器4的计算结果,所述分段式缓存区5的写使能由所述卷积计算器4给出,读出逻辑由所述缓存区控制器6控制。

19.所述的卷积计算器4为通用定点数计算器,以fpga中的dsp48为基础,由并行的64个计算单元和累加逻辑组成,单个时钟周期同时进行64个乘加计算,计算数据由所述高并行缓存区3提供,并将计算结果缓存至所述分段式缓存区5。卷积计算器4是神经网络卷积硬件加速器的核心,负责执行卷积计算,在计算时使用hls指导语句,充分利用了包括卷积核内、卷积核间等在内的多种并行和数据复用,达到快速计算卷积的效果。

20.所述的状态控制器7是由5个状态构成,分别为等待、卷积核缓存、特征缓存、计算和发送;其中,卷积核缓存和特征缓存状态将信号发到高并行缓存区3;计算状态将信号发到卷积计算器4;发送状态将信号发到分段式缓存区5;等待状态是状态控制器7等待外部处理器的使能信号。

21.所述的缓存区控制器6是由包含多路选择器在内的组合逻辑组成,负责接收状态控制器7发送来的对于高并行缓存区3和分段式缓存区5的信号,并进行处理后发送到高并行缓存区3和分段式缓存区5。

22.如图3所示,本发明所述的卷积计算器4的计算过程为:

23.待计算数据并行进入卷积计算器4,每个时钟共计有64组由卷积核和特征图构成的数据进入卷积器计算4,对于卷积核大小为3

×

3的卷积计算器4,具有9个乘法器卷积器计算共需十个时钟计算出结果,其中前九个时钟执行乘累加,第十个时钟将结果发送至分段式缓存区;当状态控制器7得知前九个时钟执行乘累加的结果不是最终结果时,则状态控制器7控制卷积计算器4继续进行计算,直至完成计算。

24.如图2所示,本发明的卷积核大小为3

×

3的卷积计算过程如下:

25.对于一张图片,3x3的卷积核每次从图片中同一通道取9个点的数据,将该9个点的数据与3x3的卷积核中相同通道对应的权重相乘,然后将得到的9个乘积相加,所述的将得到的9个乘积相加,是将乘积每三个为一组进行相加,将该累加结果再相加完成一个3x3窗口的加法,即完成一个通道的卷积计算,窗口滑动1个步长,继续进行同样的计算,直至完成图中所有点的计算,将所有通道的卷积计算结果进行累加,并输出到分段式缓存区。

26.可以设置有9个乘法器同时完成9x9个点对应的乘积计算。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1