多处理器互连的性能评估的方法、装置、设备及可读介质与流程

1.本发明涉及计算机领域,并且更具体地涉及一种多处理器互连访问的性能评估的方法、装置、设备及可读介质。

背景技术:

2.共享内存多处理机是计算机体系结构中的一种重要结构,通过专用的处理器点对点一致性协议接口、复杂的拓扑结构和互连网络进行互连,实现多处理器的一致性互连和全局内存的共享。对于共享内存多处理机,根据处理器接口数量和接口支持一致性协议转发功能情况,可以进行多处理器直连或通过协同芯片代理实现多处理机系统。如ibm的power小型机,power处理器由于有足够的处理器直连接口,因此可以通过处理器直连实现16路系统。intel的xeon处理器通常只有3个处理器互连接口(qpi或upi),接口支持多跳步的一致性协议转发,基于xeon处理器最大能够实现8路系统,所以在实现16路系统时,需要通过处理器协同芯片作为中间代理,实现接口扩展和报文转发,基于协同芯片可以构建16路以上大规模的多处理机系统。其中,处理器协同芯片主要作用是根据处理器的一致性协议,实现多处理器间cache一致性协议报文的处理和转发,在面向处理器侧,需要设计处理器接口,面向其他处理器需要设计互连网络接口。在处理器协同芯片设计初期,由于芯片没有工程实现,无法对多处理机系统的节点间延迟和带宽进行测试。

技术实现要素:

3.有鉴于此,本发明实施例的目的在于提出一种多处理器互连访问的性能评估的方法、装置、设备及可读介质,通过使用本发明的技术方案,能够实现对特定一致性协议下的多处理器进行本地和远程访问的延迟和带宽进行测算,能够实现在协同芯片设计之初即可对系统的节点间访问延迟和带宽进行量化评估。

4.基于上述目的,本发明的实施例的一个方面提供了一种多处理器互连访问的性能评估的方法,包括以下步骤:

5.对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;

6.根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;

7.根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

8.根据本发明的一个实施例,系统性能包括远程访问总延迟数据和带宽数据。

9.根据本发明的一个实施例,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

10.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。

11.根据本发明的一个实施例,根据获取到的传输路径中的各个传输阶段的延迟数据

对系统性能进行评估包括:

12.获取处理器之间访问的最大请求书和数据包大小;

13.使用以下公式计算带宽数据:

14.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。

15.本发明的实施例的另一个方面,还提供了一种多处理器互连访问的性能评估的装置,装置包括:

16.建模模块,建模模块配置为对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;

17.获取模块,获取模块配置为根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;

18.评估模块,评估模块配置为根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

19.根据本发明的一个实施例,系统性能包括远程访问总延迟数据和带宽数据。

20.根据本发明的一个实施例,评估模块还配置为:

21.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。

22.根据本发明的一个实施例,评估模块还配置为:

23.获取处理器之间访问的最大请求书和数据包大小;

24.使用以下公式计算带宽数据:

25.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。

26.本发明的实施例的另一个方面,还提供了一种计算机设备,该计算机设备包括:

27.至少一个处理器;以及

28.存储器,存储器存储有可在处理器上运行的计算机指令,指令由处理器执行时实现上述任意一项方法的步骤。

29.本发明的实施例的另一个方面,还提供了一种计算机可读存储介质,计算机可读存储介质存储有计算机程序,计算机程序被处理器执行时实现上述任意一项方法的步骤。

30.本发明具有以下有益技术效果:本发明实施例提供的多处理器互连访问的性能评估的方法,通过对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估的技术方案,能够实现对特定一致性协议下的多处理器进行本地和远程访问的延迟和带宽进行测算,能够实现在协同芯片设计之初即可对系统的节点间访问延迟和带宽进行量化评估。

附图说明

31.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的实施例。

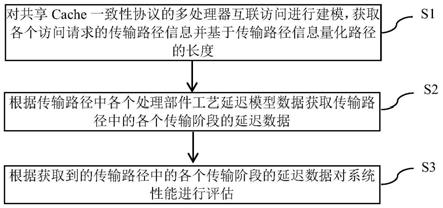

32.图1为根据本发明一个实施例的多处理器互连访问的性能评估的方法的示意性流程图;

33.图2为根据本发明一个实施例的多处理器互连访问的性能评估的装置的示意图;

34.图3为根据本发明一个实施例的计算机设备的示意图;

35.图4为根据本发明一个实施例的计算机可读存储介质的示意图。

具体实施方式

36.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明实施例进一步详细说明。

37.基于上述目的,本发明的实施例的第一个方面,提出了一种多处理器互连访问的性能评估的方法的一个实施例。图1示出的是该方法的示意性流程图。

38.如图1中所示,该方法可以包括以下步骤:

39.s1对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度。

40.通过对多处理器共享cache一致性协议进行建模分析,可以获取到各类型访存传输过程的路径信息。例如,针对某种一致性协议下的有目录远程访问请求,根据协议跳转过程可以获得该笔访问的路径,通过对协议跳转和传输接口路径的分析,以单flit传输延迟为单位,量化各类访存传输路经的长度,flit单位指的是传输处理一个flit报文数据包所用时间。

41.s2根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据。

42.基于特定处理器接口实际延迟数据、协同芯片采用的实现工艺延迟模型数据、协同芯片频率等,对访存过程的各个阶段进行赋值。例如,在某协同芯片具体实现中,按照芯片的模块划分,结合运行频率和工艺延迟模型,进行延迟假定,假定数据通过设计、参考模型综合测算得出,如下表所示:

43.表1各个处理部件的延迟时间

44.处理部件通过延时物理层15ns链路层15ns派发5ns远程协议处理15ns片上交换9ns网络接口15ns网路接口链路层25ns本地协议处理15ns访问cpu内存60ns协同芯片目录cache命中延迟5ns监听一个节点延迟50ns

45.s3根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

46.通过路径延迟累加计算路径总延迟和各类访存事务本地、远程平均延迟,单位时间获取的数据量除以时间即为带宽,即带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。例如,在某协同芯片中进行的延迟假定条件下,最大请求数为1024,数据包大小为64byte,总延迟725ns,则单个cpu通过单侧协同芯片的远程带宽约为:1024*64byte/(725+1023)=37gb/s。

47.处理器协同芯片是基于多处理器间cache一致性协议的多层结构设计的互连芯片。通常完整的cache一致性协议包括多层子协议,必须包括协议层、链路层和物理层,针对协议报文的传输和转发,还有传输层和路由层等。处理器协同芯片的结构一般包括物理层(负责与处理器互连)、链路层(负责将报文打包、流控和转发给物理层,或从物理层接收)、派发模块(负责将接口报文派发到各协议处理模块,或从协议处理模块接收)、协议处理引擎(一般根据远程和本地代理,将协议处理引擎划分为多条协议处理流水线实现)、片上交换(实现对协议处理模块和网络接口的报文的路由、交换)、网络接口(系统节点间的互连接口,协同芯片通过该接口与其他协同芯片进行互连)。

48.本发明主要目的是为了解决处理器协同芯片设计初期,多处理器性能评价没有有效方法的问题。通过对多处理器共享cache一致性协议的建模、延迟路径的量化分析、单元延迟时间的假定和带宽测算可以对特定一致性协议下的多处理机进行本地、远程访问的延迟和带宽进行评估,得到相应数据,实现了对多处理器系统,特别是带有协同芯片的多处理器系统,在协同芯片设计之初即可对系统的节点间访问延迟和带宽进行量化评估,评估结果可以作为设计方案可行性的重要评价依据。

49.通过本发明的技术方案,能够实现对特定一致性协议下的多处理器进行本地和远程访问的延迟和带宽进行测算,能够实现在协同芯片设计之初即可对系统的节点间访问延迟和带宽进行量化评估。

50.在本发明的一个优选实施例中,系统性能包括远程访问总延迟数据和带宽数据。

51.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

52.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。通过路径延迟累加,计算路径总延迟和各类访存事务本地、远程平均延迟。例如,在某协同芯片中进行的延迟假定条件下,远程访问总延时为:725ns。包括下列延迟总和:readclean to rdex延迟:135ns;rdex to readclean延迟:200ns;compdata_uc to pger延迟:170ns;pger to compdata_uc延迟:135ns;compack延迟:85ns。

53.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

54.获取处理器之间访问的最大请求书和数据包大小;

55.使用以下公式计算带宽数据:

56.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。单位时间获取的数据量除以时间即为带宽,即带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。例如,在某协同芯片中进行的延迟假定条件下,最大请求数为1024,数据包大小为64byte,总延迟725ns,则单个cpu通过单侧协同芯片的远程带宽约为:1024*64byte/(725+1023)=37gb/s。

57.通过本发明的技术方案,能够实现对特定一致性协议下的多处理器进行本地和远程访问的延迟和带宽进行测算,能够实现在协同芯片设计之初即可对系统的节点间访问延迟和带宽进行量化评估。

58.需要说明的是,本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,可以通过计算机程序来指令相关硬件来完成,上述的程序可存储于计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中存储介质可为磁碟、光盘、只读存储器(read

‑

only memory,rom)或随机存取存储器(random access memory,ram)等。上述计算机程序的实施例,可以达到与之对应的前述任意方法实施例相同或者相类似的效果。

59.此外,根据本发明实施例公开的方法还可以被实现为由cpu执行的计算机程序,该计算机程序可以存储在计算机可读存储介质中。在该计算机程序被cpu执行时,执行本发明实施例公开的方法中限定的上述功能。

60.基于上述目的,本发明的实施例的第二个方面,提出了一种多处理器互连访问的性能评估的装置,如图2所示,装置200包括:

61.建模模块201,建模模块201配置为对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;

62.获取模块202,获取模块202配置为根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;

63.评估模块203,评估模块203配置为根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

64.在本发明的一个优选实施例中,系统性能包括远程访问总延迟数据和带宽数据。

65.在本发明的一个优选实施例中,评估模块还配置为:

66.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。

67.在本发明的一个优选实施例中,评估模块还配置为:

68.获取处理器之间访问的最大请求书和数据包大小;

69.使用以下公式计算带宽数据:

70.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。

71.基于上述目的,本发明实施例的第三个方面,提出了一种计算机设备。图3示出的是本发明提供的计算机设备的实施例的示意图。如图3所示,本发明实施例包括如下装置:至少一个处理器21;以及存储器22,存储器22存储有可在处理器上运行的计算机指令23,指令由处理器执行时实现以下方法:

72.对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;

73.根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;

74.根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

75.在本发明的一个优选实施例中,系统性能包括远程访问总延迟数据和带宽数据。

76.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟

数据对系统性能进行评估包括:

77.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。

78.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

79.获取处理器之间访问的最大请求书和数据包大小;

80.使用以下公式计算带宽数据:

81.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。

82.基于上述目的,本发明实施例的第四个方面,提出了一种计算机可读存储介质。图4示出的是本发明提供的计算机可读存储介质的实施例的示意图。如图4所示,计算机可读存储介质s31存储有被处理器执行时执行如下方法的计算机程序s32:

83.对共享cache一致性协议的多处理器互联访问进行建模,获取各个访问请求的传输路径信息并基于传输路径信息量化路径的长度;

84.根据传输路径中各个处理部件工艺延迟模型数据获取传输路径中的各个传输阶段的延迟数据;

85.根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估。

86.在本发明的一个优选实施例中,系统性能包括远程访问总延迟数据和带宽数据。

87.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

88.将各个访问请求的传输路径信息中的各个阶段的延迟数据相加以得到各个访问请求的总延迟数据。

89.在本发明的一个优选实施例中,根据获取到的传输路径中的各个传输阶段的延迟数据对系统性能进行评估包括:

90.获取处理器之间访问的最大请求书和数据包大小;

91.使用以下公式计算带宽数据:

92.带宽=最大发送请求数*数据包大小/(总延迟+最大请求数减1)。

93.此外,根据本发明实施例公开的方法还可以被实现为由处理器执行的计算机程序,该计算机程序可以存储在计算机可读存储介质中。在该计算机程序被处理器执行时,执行本发明实施例公开的方法中限定的上述功能。

94.此外,上述方法步骤以及系统单元也可以利用控制器以及用于存储使得控制器实现上述步骤或单元功能的计算机程序的计算机可读存储介质实现。

95.本领域技术人员还将明白的是,结合这里的公开所描述的各种示例性逻辑块、模块、电路和算法步骤可以被实现为电子硬件、计算机软件或两者的组合。为了清楚地说明硬件和软件的这种可互换性,已经就各种示意性组件、方块、模块、电路和步骤的功能对其进行了一般性的描述。这种功能是被实现为软件还是被实现为硬件取决于具体应用以及施加给整个系统的设计约束。本领域技术人员可以针对每种具体应用以各种方式来实现的功能,但是这种实现决定不应被解释为导致脱离本发明实施例公开的范围。

96.在一个或多个示例性设计中,功能可以在硬件、软件、固件或其任意组合中实现。如果在软件中实现,则可以将功能作为一个或多个指令或代码存储在计算机可读介质上或

通过计算机可读介质来传送。计算机可读介质包括计算机存储介质和通信介质,该通信介质包括有助于将计算机程序从一个位置传送到另一个位置的任何介质。存储介质可以是能够被通用或专用计算机访问的任何可用介质。作为例子而非限制性的,该计算机可读介质可以包括ram、rom、eeprom、cd

‑

rom或其它光盘存储设备、磁盘存储设备或其它磁性存储设备,或者是可以用于携带或存储形式为指令或数据结构的所需程序代码并且能够被通用或专用计算机或者通用或专用处理器访问的任何其它介质。此外,任何连接都可以适当地称为计算机可读介质。例如,如果使用同轴线缆、光纤线缆、双绞线、数字用户线路(dsl)或诸如红外线、无线电和微波的无线技术来从网站、服务器或其它远程源发送软件,则上述同轴线缆、光纤线缆、双绞线、dsl或诸如红外线、无线电和微波的无线技术均包括在介质的定义。如这里所使用的,磁盘和光盘包括压缩盘(cd)、激光盘、光盘、数字多功能盘(dvd)、软盘、蓝光盘,其中磁盘通常磁性地再现数据,而光盘利用激光光学地再现数据。上述内容的组合也应当包括在计算机可读介质的范围内。

97.以上是本发明公开的示例性实施例,但是应当注意,在不背离权利要求限定的本发明实施例公开的范围的前提下,可以进行多种改变和修改。根据这里描述的公开实施例的方法权利要求的功能、步骤和/或动作不需以任何特定顺序执行。此外,尽管本发明实施例公开的元素可以以个体形式描述或要求,但除非明确限制为单数,也可以理解为多个。

98.应当理解的是,在本文中使用的,除非上下文清楚地支持例外情况,单数形式“一个”旨在也包括复数形式。还应当理解的是,在本文中使用的“和/或”是指包括一个或者一个以上相关联地列出的项目的任意和所有可能组合。

99.上述本发明实施例公开实施例序号仅仅为了描述,不代表实施例的优劣。

100.本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

101.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本发明实施例公开的范围(包括权利要求)被限于这些例子;在本发明实施例的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,并存在如上的本发明实施例的不同方面的许多其它变化,为了简明它们没有在细节中提供。因此,凡在本发明实施例的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明实施例的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1