一种芯片验证自动化控制方法与流程

1.本发明涉及芯片验证技术领域,尤其涉及一种芯片验证自动化控制方法。

背景技术:

2.随着芯片设计复杂度的提升,验证工作面临着越来越大的挑战。作为独立于设计的工种,在设计人员完成代码的初步开发后,验证人员需要在仿真平台上对设计进行代码级的测试。测试的内容主要在功能和性能两部分,功能是芯片要做什么,性能是芯片跑多快。功能测试需要验证人员根据芯片规格编写测试pattern通过仿真观察芯片运行是否符合预期。性能测试需要评估系统处理激励消耗的时间,需要根据芯片工作主频、模块设计时序进行初步评估,实际性能与综合结果、后端工艺实现均有关联。从前仿的角度看,验证人员需要根据方案划分来对不同层面的验证需求进行分解,通过仿真以确认芯片工作正常。

3.那么如何保证验证的完备性呢?验证工程师会制定一份验证计划来指导验证进程,典型做法如下:

4.(1)编写定向测试用例,通过特定的配置和激励,测试设计能否实现预期的功能。这种方式单条用例的场景比较单一,需要维护大量的测试条目,且容易遗漏feature。

5.(2)对配置和场景进行随机化处理,通过配置和激励的随机组合,模拟不同的测试场景。这种方式在面对复杂的设计时,由于场景比较多,容易漏测并造成仿真资源的浪费。

6.(3)分析coverage以补充测试场景。这种方式的缺点是可能会漏测某些功能,因为代码上的覆盖并不能保证功能上的覆盖。

7.(4)编写参考模型。目的是与rtl处理结果进行自动化比对,提高问题定位效率;

8.从上面的分析可以看出,在芯片开发周期比较紧张的情况下,面对复杂的设计,验证工程师除了制定一份完备的验证计划,也需要搭建一个高效的仿真平台,来相对快速的遍历测试场景。验证平台的搭建本身并无标准,主要结合项目需求进行开发,如下几种:

9.(1)使用verilog/sv语言编写,进行简单测试,激励比较简单,多用于开发人员自测;

10.(2)基于specman e语言。作为一种面向对象的开发语言,e语言可以在行为级对激励,行为进行描述,灵活性比较好;

11.(3)基于sv编写的vmm/uvm框架。考虑到sv同时作为代码开发和验证的工作语言,可以提高开发和验证的沟通效率,且框架提供了一系列的仿真库,可以加速验证平台的开发,这一方式已成为业界主流。

12.从实际来看,越来越多的项目在采用基于uvm框架搭建验证平台,那么如何加速仿真进程呢?依靠服务器性能的提升固然可以缩短仿真时间,但这会引入额外的项目成本。

技术实现要素:

13.本发明提供了一种芯片验证自动化控制方法,在仿真启动后,能够根据设定的参数自动控制仿真平台重复运行,直至将预期的场景遍历完后,仿真才退出,极大的提高了芯

片的仿真效率和验证工作的价值。

14.为了实现本发明的目的,一种芯片验证自动化控制方法,包括如下步骤:

15.1)基于uvm建立一个仿真平台组件的树形结构,树形结构的根节点由uvm控制,根节点通过实例化一个继承自uvm_test的类产生,一般为用例名。在用例类中,例化平台的env/agent等组件;

16.2)建立阶段进行仿真组件的实例化,根据指定的例化名来生成各个组件,并通过parent参数指定父节点;同时建立covergroup,对待监控的场景配置进行建仓,指定需要监控的触发场景;

17.3)连接阶段将各个组件连接起来;

18.4)复位阶段将硬件复位,所有触发器回到初始状态,对待测配置进行随机处理,随机值由仿真器随机得到;

19.5)在配置阶段,对硬件进行配置,并将步骤4)随机处理后的结果同步配置到平台;

20.6)在运行阶段,硬件接收输入激励,相应的监控同时实时监测硬件运行的正确性;

21.7)在main阶段发送激励,通过行为对比,而在此之前会对硬件进行相应的配置;

22.8)在关断阶段运行covergroup的采样,如果未达到目标,则跳转到步骤4),执行下一轮仿真,否则跳转到步骤9);

23.9)在检查阶段检查硬件退出仿真后的状态。

24.作为本发明的优化方案,在步骤2)中还完成接口和配置参数的传递,指定待测配置的随机范围。

25.作为本发明的优化方案,在步骤3)中,组件连接包括接口连接和组件互联。

26.作为本发明的优化方案,在步骤4)中,test case中的随机类进行随机化得到测试的一组随机值,随机值方式为sv自带的randomize函数。

27.作为本发明的优化方案,在步骤6)中,监控包括参考模型和断言。

28.作为本发明的优化方案,在步骤9)中,硬件退出仿真后的状态包括统计状态、fifo状态或状态机。

29.作为本发明的优化方案,运行阶段与复位阶段、配置阶段、main阶段、关断阶段4个子阶段并行执行。

30.本发明具有积极的效果:1)相对定向测试,uvm的phase跳转可以在一条测试用例中覆盖多种模式,避免重复的编写测试用例,提高单条用例的覆盖范围,降低维护成本;

31.2)本发明相对全随机测试,通过sv的randomize函数能够对变量式范围进行模糊指定,如inside可以在范围内随机,dist可以进行带权重随机,避免无意义的重复,能够更快的触发期望的测试场景;

32.3)本发明相对单次仿真模式,能够通过重复仿真增加对待测配置的遍历,可以在无人工干预下由仿真器自行对待测模式进行遍历,提高仿真效率;

33.4)本发明相对代码覆盖率,功能覆盖率covergroup侧重从功能角度对场景进行监控,更贴近实际使用;

34.5)本发明对芯片验证过程中的定向测试方式进行了改进,又避免了全随机模式对仿真资源造成的浪费,提高了仿真效率,加快仿真的收敛。

附图说明

35.下面结合附图和具体实施方式对本发明作进一步详细的说明。

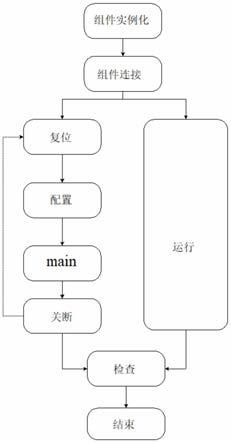

36.图1是本发明的流程图。

具体实施方式

37.下面结合附图对本发明的实现做进一步详细的描述:。

38.如图1所示,一种芯片验证自动化控制方法,包括如下步骤

39.1)基于uvm建立一个仿真平台组件的树形结构,树形结构的根节点由uvm控制,根节点通过实例化一个继承自uvm_test的类产生,一般为用例名。在用例类中,例化平台的env/agent等组件;

40.2)建立阶段进行仿真组件的实例化,根据指定的例化名来生成各个组件,并通过parent参数指定父节点;同时建立covergroup,对待监控的场景配置进行建仓;

41.3)连接阶段将各个组件连接起来;

42.4)复位阶段将硬件复位,所有触发器回到初始状态,对待测配置进行随机处理,随机值由仿真器随机得到;

43.5)在配置阶段,对硬件进行相应的配置,并将步骤4)随机处理后的结果同步配置到平台;

44.6)在运行阶段,硬件接收输入激励,相应的监控同时实时监测硬件运行的正确性;

45.7)在main运行阶段发送激励,通过行为对比,而在此之前会对硬件进行相应的配置;仿真阶段分为复位、配置、main、关断4个部分;

46.8)在关断阶段运行covergroup的采样,如果未达到目标(覆盖率未达到100%),则跳转到步骤4),执行下一轮仿真,否则跳转到步骤9);

47.9)在检查阶段检查硬件退出仿真后的状态

48.芯片验证自动化控制方法整个进程基于uvm phase机制控制,各个阶段如图1所示。

49.在步骤2)中还完成接口和配置参数的传递,指定待测配置的随机范围。tese case中初始化covergroup(功能覆盖率),指定covergroup的采样区间及交叉覆盖率等。

50.在步骤3)中,组件连接包括接口连接和组件互联。

51.在步骤4)中,test case中的随机类进行随机化得到测试的一组随机值,随机值方式为sv自带的randomize函数。同时,数字电路中的基本存储单元如触发器/ram在复位阶段均回到默认值,以提供一个初始化环境。

52.在步骤6)中,监控包括参考模型和断言。使用断言可以创建更稳定、品质更好且不易于出错的代码。

53.在步骤7)中,在main阶段发送激励,通过行为对比,测试相应的配置下能否对输入激励进行正确处理;通过参考模型和断言会对运行过程进行监控,error会打印到log中,方便问题定位。

54.在关断阶段同时会打印出覆盖率数据和重复次数,能够对仿真进度有一个量化。

55.在步骤9)中,硬件退出仿真后的状态包括统计状态、fifo状态或状态机,如果发现异常,会打印出来方便后续侦错。

56.所有步骤结束后退出仿真,报告仿真资源的消耗和时间等信息。

57.运行阶段与复位阶段、配置阶段、main阶段、关断阶段4个子阶段并行执行。

58.以上所述实施例仅表达了本发明的实施方式,其描述较为具体和详细,并不能因此而理解为对本发明专利范围的限制。应当指出的是,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1