随机数产生器及其操作方法以及产生随机数的方法与流程

1.本揭露涉及一种随机数产生器领域,且有关于一种随机数产生器、随机数产生器的操作方法以及产生随机数的方法。

背景技术:

2.具有恰当偏置的基于选择器的振荡器实施随机数产生器可被使用。举例来说,基于选择器的振荡器需要偏置,使得跨越选择器的电压在其阈值电压(vth)与保持电压(vhold)之间。然而,因为工艺电压温度(process-voltage-temperature;pvt)变化,所以难以将跨越选择器的偏置电压适当地设置成正好是在阈值电压与保持电压之间。因此,减弱由基于选择器的振荡器产生的振荡,且偏置所产生的随机数。期望设计能够跨越pvt变化自保持振荡的随机数产生器。

技术实现要素:

3.根据本揭露的实施例,随机数产生器包括控制电路、动态标头电路、振荡电路、振荡检测电路以及锁存器电路。控制电路扫描多个配置当中的偏置控制信号的配置。动态标头电路基于偏置控制信号的配置而产生偏置电压。振荡电路包括选择器。振荡电路基于偏置电压而产生振荡信号。选择器在非导电状态与导电状态之间交替地切换以产生振荡信号。振荡检测电路检测振荡信号的起始,且在检测振荡信号的起始后输出锁定信号。锁存器电路根据触发信号锁存振荡信号以输出随机数。在通过振荡检测电路输出锁定信号之后确证触发信号。偏置控制信号的配置根据锁定信号被锁定。

4.根据本揭露的实施例,产生随机数的方法适于包括选择器的随机数产生器。所述方法包括:扫描多个配置当中的偏置控制信号的配置;基于偏置控制信号的配置而产生偏置电压;基于偏置电压而产生振荡信号,其中选择器在非导电状态与导电状态之间交替地切换以产生振荡信号;检测振荡信号的起始且在检测振荡信号的起始后输出锁定信号;以及根据触发信号锁存振荡信号以输出随机数,其中在输出锁定信号之后确证触发信号,且偏置控制电压的配置根据锁定信号被锁定。

5.根据本揭露的实施例,操作方法用于随机数产生器。随机数产生器包括振荡电路、控制电路、动态标头电路、振荡检测电路以及锁存器电路,操作方法包括:通过控制电路,扫描多个配置当中的偏置控制信号的配置;通过动态标头电路,根据偏置控制信号的配置产生偏置电压;通过振荡电路,根据偏置电压产生振荡信号,其中振荡电路包括选择器和电容器,选择器在导电状态与非导电状态之间交替地切换且交替地充电和放电电容器以产生振荡信号;通过振荡检测电路,检测振荡信号的起始,且通过振荡检测电路,在检测振荡信号的起始后输出锁定信号,其中偏置控制信号的配置根据锁定信号被锁定;以及通过锁存器电路,根据触发信号锁存振荡信号以输出随机数,其中在通过振荡检测电路输出锁定信号之后确证触发信号。

附图说明

6.当结合随附图式阅读时从以下详细描述最好地理解本揭露的方面。应注意,根据业界中的标准惯例,各种特征未按比例绘制。实际上,为了论述清楚起见,可任意增大或减小各种特征的尺寸。

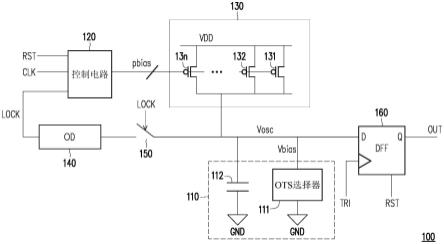

7.图1为根据一些实施例的随机数产生器的示意图。

8.图2a到图2j示出根据一些实施例的振荡检测电路的示意图和信号的波形图。

9.图3示出根据一些实施例的控制电路的示意图。

10.图4示出根据一些实施例的包括于控制电路中的计数器电路的示意图。

11.图5示出根据一些实施例的随机数产生器中的信号的波形图。

12.图6示出根据一些实施例的随机数产生器中的控制电路的示意图。

13.图7到图9示出根据一些替代性实施例的随机数产生器的示意图。

14.图10示出根据一些实施例的随机数产生器的振荡电路中的选择器的电流-电压(current-voltage;iv)曲线。

15.图11示出根据一些实施例的产生随机数的方法的流程图。

16.图12示出根据一些实施例的随机数产生器的操作方法的流程图。

17.附图标号说明

18.100、200、300、400:随机数产生器;

19.101、103:电流-电压曲线;

20.110、210:振荡电路;

21.111:选择器;

22.112:负载电容器;

23.120:控制电路;

24.121_0、121_n-1、121_x:计数器电路;

25.122、150:开关;

26.123、170、1413、1453:延迟电路;

27.130:动态标头电路;

28.131、132、13n:晶体管;

29.140、od:振荡检测电路;

30.141:下降沿检测电路;

31.143、143_1、143_2、147、147_1、147_2、160:锁存器电路;

32.145:上升沿检测电路;

33.1101、1103、1105、1107、1109、1201、1203、1205、1207、1209:框;

34.1211:触发器电路;

35.1213、1215、1411、1415、1417、1451、1455、1457:逻辑电路;

36.1231、1233:延迟元件;

37.clk:时钟信号;

38.d、j、k:输入端;

39.dlock、lock_d1、lockb_d1:延迟锁定信号;

40.fe1、fe2、fe3、fe4:下降沿;

41.gnd:参考端;

42.l1、l2、l3:预锁定信号;

43.lock:锁定信号;

44.lockb:反相锁定信号;

45.ne、pe:检测信号;

46.nq、q:输出端;

47.out:数字化随机数;

48.p11:负脉冲;

49.p12、p13、p21、p22、p23、p31、p41:正脉冲;

50.p51、p52:脉冲;

51.pbias:偏置控制信号;

52.prelock:预锁定信号;

53.rb:反相重置信号;

54.rs:电阻器;

55.re1、re2、re3、re4:上升沿;

56.rst:重置信号;

57.tri:触发信号;

58.vbias:偏置电压;

59.vdd:电源;

60.vhold:保持电压;

61.vosc:振荡信号;

62.vth:阈值电压。

具体实施方式

63.以下公开提供用于实施所提供主题的不同特征的许多不同实施例或实例。下文描述组件和布置的具体实例来简化本揭露。当然,这些仅为实例且并不意图为限制性的。举例来说,在以下描述中,第一特征在第二特征上方或第二特征上形成可包括第一特征与第二特征直接接触地形成的实施例,且还可包括可在第一特征与第二特征之间形成额外特征,使得第一特征与第二特征可以不直接接触的实施例。另外,本揭露可能在各种实例中重复附图标号和/或字母。这一重复是出于简化和清楚的目的,且本身并不指示所论述的各种实施例和/或配置之间的关系。

64.此外,为易于描述而,可在本文中使用例如“在

……

下方”、“在

……

之下”、“下部”、“在

……

之上”、“上部”以及类似物的空间相对术语,来描述如图中所示出一个元件或特征与另一元件或特征的关系。除图式中所描绘的定向外,空间相关术语意图涵盖装置在使用或操作中的不同定向。设备可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间相对描述词可同样相应地进行解释。

65.根据一些实施例,在多个配置当中扫描偏置控制信号的配置,且基于偏置控制信号的配置而产生偏置电压。包括选择器和电容器的振荡电路被配置成基于偏置电压而产生振荡信号。选择器在导电状态与非导电状态之间交替地切换且交替地充电和放电负载电容

器以产生振荡信号。振荡检测电路被配置成通过检测振荡信号的下降沿和上升沿中的至少一个来检测振荡信号的起始。在检测振荡信号的起始之后,振荡检测电路输出用以锁定偏置控制信号的配置的锁定信号,因此锁定施加到振荡电路的偏置电压的值。一旦输出锁定信号,就控制开关以从振荡电路解耦振荡检测电路。锁存器电路被配置成在输出锁定信号之后锁存振荡信号以产生数字化随机数。以这种方式,无论pvt变化,被确证(assert)给振荡电路的偏置电压都会自校准且锁定到恰当偏置电压。因此,改良振荡电路的振荡鲁棒性,且改良通过随机数产生器产生的数字化随机数的质量。

66.图1为根据一些实施例的随机数产生器100的示意图。随机数产生器100包括振荡电路110、控制电路120、动态标头电路130、振荡检测电路(od)140、开关150以及锁存器电路160。应注意,随机数产生器100可包括更多或更少绘示于图1中的元件。

67.在一些实施例中,振荡电路110包括选择器111和被并联耦接到选择器111的负载电容器112。振荡电路110被配置成基于施加到振荡电路110的偏置电压vbias而产生振荡信号vosc。在一些实施例中,选择器111包括双向阈值开关(ovonic threshold switch;ots),所述双向阈值开关具有表征为ots的阈值电压vth和保持电压vhold的滞后突返(hysteresis snapback)行为。经由图10中的电流-电压(iv)曲线101示出选择器111的滞后突返行为。参考图10,图10中的横轴示出跨越选择器111的电压,且图10中的纵轴示出流过选择器111的电流。当跨越选择器111的电压尚未超出阈值电压vth时,选择器111处于非导电状态。当跨越选择器111的电压超出ots的阈值电压vth时,跨越选择器111的电压下降或突返到保持电压vhold,且选择器111从非导电状态切换到导电状态。ots保持导电状态直到跨越选择器111的电压减小到低于保持电压vhold。当跨越选择器111的电压减小到低于保持电压vhold时,选择器111从导电状态切换到非导电状态。

68.在一些实施例中,当恰当偏置电压vbias被确证给振荡电路110时,负载电容器112被交替地充电和放电,且选择器111在导电状态与非导电状态之间交替地切换,因此产生振荡信号vosc。最初,选择器111处于非导电状态,且当偏置电压vbias被确证给所述振荡电路110时负载电容器112开始充电。当负载电容器112并联被耦接到选择器111时,跨越负载电容器112的电压与跨越选择器111的电压相同。当跨越选择器111的电压超出阈值电压vth时,选择器111从非导电状态切换到导电状态。因此,放电路径经由选择器111被形成于负载电容器112与参考端gnd之间。负载电容器112经由放电路径开始放电,且跨越选择器111的电压开始减小。当跨越选择器111的电压减小到低于ots的保持电压vhold时,选择器111切换到非导电状态,负载电容器112的放电路径被断开,且负载电容器开始再次充电。负载电容器112的交替充电和放电的过程在振荡电路110的输出处产生振荡信号vosc。因为基于选择器111的操作而产生振荡信号vosc,所以振荡电路110还被称为基于选择器的振荡器(selector-based oscillator)。

69.返回到图1,控制电路120被配置成产生用以控制动态标头电路130的操作的偏置控制信号pbias。在一些实施例中,控制电路120被配置成以减小或增加强度方式扫描偏置控制信号pbias的配置(例如值)。举例来说,如果偏置控制信号pbias为4位数字值,那么控制电路120可从“0000”到“1111”以增加方式扫描偏置控制信号pbias的配置。替代地,控制电路120可从“1111”到“0000”以减小方式扫描偏置控制信号pbias的配置。在一些替代性实施例中,偏置控制信号pbias为模拟信号。

70.在一些实施例中,控制电路120具有接收时钟信号clk和重置信号rst的输入端,其中基于时钟信号clk而产生偏置控制信号pbias,且重置信号rst用以重置控制电路120的操作。控制电路120还可具有接收锁定信号lock的输入端。当锁定信号lock被确证给控制电路120时,控制电路120锁定偏置控制信号pbias的配置。举例来说,当锁定信号lock确证给控制电路120时偏置控制信号pbias的配置为“1011”时,控制电路120将偏置控制信号pbias锁定在配置“1011”处。在一些替代性实施例中,控制电路120在锁定信号lock的确证的延迟时间段之后锁定偏置控制信号pbias的配置。

71.动态标头电路130被耦接到控制电路120以接收偏置控制信号pbias。动态标头电路130被配置成基于偏置控制信号pbias的配置而产生偏置电压。偏置电压用以偏置振荡电路110,从而产生振荡信号vosc。在一些实施例中,当输出锁定信号lock时,锁定偏置控制信号pbias的配置,且通过动态标头电路130输出的偏置电压固定对应于偏置控制信号pbias的锁定配置的值。在一些实施例中,动态标头电路130包括多个晶体管131~13n,所述晶体管通过从控制电路120所接收到的偏置控制信号pbias被控制。晶体管131~13n的栅极接收来自控制电路120的偏置控制信号pbias。晶体管131~13n的源极可接收电源vdd,且晶体管131~13n的漏极被配置成输出偏置电压vbias。

72.晶体管131~13n可以不同方式加权。在一些实施例中,晶体管131~13n为二进制加权,使得晶体管131具有20(或“1”)的权重系数,晶体管132具有21(或“2”)的权重系数且晶体管13n具有2

n-1

的权重系数,其中n为正整数。应注意,晶体管131~13n中的每一个的权重系数可根据设计需要设置。举例来说,晶体管131~13n的权重系数可设置成20*n到2

n-1

*n,其中n为正整数。在一些实施例中,晶体管131到13n根据其晶体管尺寸进行加权。举例来说,晶体管131~13n的晶体管尺寸可分别为1

×

、2

×

、4

×

、...、2

n-1

×

。晶体管尺寸指晶体管的长度或宽度或宽度和长度的比率中的至少一个。在一些实施例中,晶体管尺寸指晶体管的宽度和长度的比率(w/l)。在实施例中,动态标头电路130中的晶体管131~13n尺寸一致;且动态标头电路130根据偏置控制信号pbias选择性激活晶体管131~13n当中的晶体管以产生偏置电压。换句话说,动态标头电路130的强度通过晶体管131~13n当中的已激活晶体管的数目来确定。

73.振荡检测电路140被配置成通过检测振荡信号vosc的上升沿或下降沿中的至少一个来检测振荡信号vosc的起始。举例来说,当振荡信号的上升沿或下降沿中的所述至少一个匹配预定图案时,振荡检测电路140确定检测振荡信号vosc的起始。振荡检测电路140在检测振荡信号vosc的起始后输出锁定信号lock。检测振荡信号vosc的起始将被更多描述于图2a到图2j。

74.开关150耦接于振荡检测电路140与振荡电路110之间。开关150被配置成根据锁定信号lock耦接或解耦振荡检测电路140和振荡电路110。换句话说,开关150基于锁定信号lock而在振荡检测电路140与振荡电路110之间形成或断开电路径。在一些实施例中,当锁定信号lock被确证时,开关150从振荡电路110电解耦振荡检测电路140。以这种方式,当锁定信号lock被输出时,振荡检测电路140停止接收振荡信号vosc。

75.锁存器电路160被耦接到振荡电路110以接收振荡信号vosc。当触发信号tri被确证给锁存器电路160时,锁存器电路160对振荡信号vosc执行锁存操作以产生数字化随机数out(还称为随机数)。在实施例中,触发信号tri从外部装置被输入。在替代实施例中,触发

信号tri根据锁定信号lock被产生。触发信号tri可以在锁定信号lock被产生的时序下被确证给锁存器电路160,或可在锁定信号lock被产生的时序的延迟时间段之后被确证给锁存器电路160。在一些实施例中,锁存器电路160通过d-触发器(d-flip-flop;dff)来实施,但本揭露不限于此。能够执行锁存操作的任何电路处于本揭露的范围内。

76.根据一些实施例,锁定信号lock在检测振荡信号vosc的起始后被输出。一旦输出锁定信号被锁定,控制电路120就锁定偏置控制信号pbias的配置且振荡检测电路140从振荡电路110被解耦。以这种方式,偏置电压vbias被自校准以适当地偏置振荡电路110。因此,通过随机数产生器100所产生的数字化随机数的质量被改良。

77.图2a示出根据一些实施例的振荡检测电路140的示意图。振荡检测电路140可包括下降沿检测电路141、上升沿检测电路145以及锁存电路143和锁存电路147。下降沿检测电路141被配置成检测振荡信号vosc的下降沿,且当检测振荡信号vosc上的下降沿时输出检测信号ne。在一些实施例中,通过检测信号ne中的脉冲来指示检测振荡信号vosc的下降沿。上升沿检测电路145被配置成检测振荡信号vosc的上升沿,且当检测振荡信号vosc上的上升沿时输出检测信号pe。在一些实施例中,通过检测信号pe中的脉冲来指示检测振荡信号vosc的上升沿。

78.下降沿检测电路141可包括逻辑电路1411、1415、1417以及延迟电路1413。在一些实施例中,逻辑电路1411和逻辑电路1417为not逻辑电路,且逻辑电路1415为nand逻辑电路。not逻辑电路1411和延迟电路1413并联耦接于nand逻辑电路1415与接收振荡信号vosc的一端之间。not逻辑电路1411被配置成使振荡信号vosc反相以产生反相振荡信号,且延迟电路1413被配置成延迟振荡信号vosc以产生延迟振荡信号。nand逻辑电路1415可对反相振荡信号和振荡信号执行nand运算。通过not逻辑电路1417使nand逻辑电路1415的输出反相以产生检测信号ne。

79.锁存器电路143接收检测信号ne,且基于确证检测信号ne而执行锁存操作以产生预锁定信号prelock信号。因此,当振荡信号vosc的下降沿被检测到时,检测信号ne被确证给锁存器电路143,且锁存器电路143输出预锁定信号prelock信号。

80.上升沿检测电路145可包括逻辑电路1451、1455、1457以及延迟电路1453。在一些实施例中,逻辑电路1451和1457为not逻辑电路,且逻辑电路1455为nand逻辑电路。not逻辑电路1451和延迟电路1453串联耦接于nand逻辑电路1455与接收振荡信号vosc的一端之间。not逻辑电路1451被配置成使振荡信号vosc反相以产生反相振荡信号,且延迟电路1453被配置成延迟反相振荡信号以产生反相振荡信号的延迟信号。nand逻辑电路1455接收振荡信号vosc和反相振荡信号的延迟信号以作为输入信号,且对输入信号执行nand运算。通过not逻辑电路1457使nand逻辑电路1455的输出反相以产生检测信号pe。图2a中的下降沿检测电路141和上升沿检测电路145的示意图仅出于说明的目的。能够检测振荡信号的下降沿或上升沿的任何电路处于本揭露的范围内。

81.锁存器电路147串联被耦接到锁存器电路143,其中锁存器电路143的输出被耦接到锁存器电路147的输入。锁存器电路147接收来自上升沿检测电路145的检测信号pe和来自锁存器电路143的预锁定信号prelock信号。锁存器电路147基于检测信号pe的确证而锁存预锁定信号prelock信号以产生锁定信号lock。因此,当检测到下降沿后接着检测到上升沿时,通过振荡检测电路140输出锁定信号lock。在一些实施例中,锁存器电路143和锁存器

电路147由dff来实施,但本揭露不限于此。

82.图2b示出根据一些实施例的振荡信号vosc、检测信号ne、检测信号pe和预锁定信号prelock信号以及锁定信号lock的波形图。振荡信号vosc具有下降沿fe1接着又具有上升沿re1以在振荡信号vosc上形成负脉冲p11。参考图2a和2b,当振荡信号vosc的下降沿fe1被检测到时,下降沿检测电路141输出具有正脉冲p12的检测信号ne。接着,锁存器电路143通过检测信号ne被触发以产生如通过图2b中从“低”到“高”的转变所指示的预锁定信号prelock信号。类似地,当检测振荡信号vosc的上升沿re1时,上升沿检测电路145输出具有正脉冲p13的检测信号pe。接着,锁存器电路147通过检测信号pe触发且锁存预锁定信号prelock信号以产生如图2b中所指示的锁定信号lock。以这种方式,如图2a中所示出的振荡检测电路140可检测下降沿和上升沿对(pair),其中下降沿接着上升沿。

83.图2c示出根据一些实施例的振荡检测电路140的示意图。图2c和图2a中所绘示的相同元件以相同附图标号示出。图2c中所示出的振荡检测电路与图2a中所示出的振荡检测电路之间的不同为锁存器电路143和锁存器电路147的位置处的交换。在图2a中,锁存器电路143的输出端被耦接到锁存器电路147的输入端。在图2b中,锁存器电路147的输出端被耦接到锁存器电路143的输入端。因此,如图2a中所示出的振荡检测电路140可在检测上升沿后接着检查下降沿后输出锁定信号lock。

84.参考图2d中所绘示的波形图,振荡信号vosc具有上升沿re2接着又具有下降沿fe2以在振荡信号vosc上形成正脉冲p21。当振荡信号vosc的上升沿re2被检测到时,上升沿检测电路145输出具有正脉冲p23的检测信号pe。接着,锁存器电路147通过检测信号pe被触发以产生如通过图2d中从“低”到“高”的转变所指示的预锁定信号prelock信号。当振荡信号vosc的下降沿fe2被检测到时,下降沿检测电路141输出具有正脉冲p22的检测信号ne。接着,锁存器电路143通过检测信号ne被触发以锁存预锁定信号prelock信号以产生如图2d中所指示的锁定信号lock。以这种方式,如图2c中所示出的振荡检测电路140可在检测上升沿后检测下降沿后输出锁定信号lock。

85.图2e示出根据一些实施例的振荡检测电路140的示意图。图2e和图2a中所绘示的相同元件以相同附图标号示出。图2e中所示出的振荡检测电路与图2a中所示出的振荡检测电路之间的不同在于图2e中所示出的振荡检测电路仅基于检测上升沿而输出锁定信号lock。参考图2e,振荡检测电路140包括上升沿检测电路145和锁存器147。关于上升沿检测电路145和锁存器电路147的详细描述可指以上参考图2a的描述。

86.参考图2e和图2f,振荡信号vosc可包括通过上升沿re3和下降沿fe3所形成的正脉冲p31。当通过上升沿检测电路145检测到振荡信号vosc的上升沿re3时,上升沿检测电路145输出检测信号pe。检测信号pe触发锁存器电路147以产生锁定信号lock。因此,如图2e中所示出的振荡检测电路140可在检测振荡信号vosc中的上升沿后输出锁定信号lock。

87.图2g示出根据一些实施例的振荡检测电路140的示意图。图2g中所示出的振荡检测电路与图2a中所示出的振荡检测电路之间的差别在于图2g中所示出的振荡检测电路仅基于检测下降沿而输出锁定信号lock。参考图2g,振荡检测电路140包括下降沿检测电路141和锁存器143。关于上升沿检测电路141和锁存器电路143的详细描述可指以上参考图2a的描述。

88.参考图2g和图2h,振荡信号vosc可包括通过上升沿re4和下降沿fe4所形成的正脉

冲p41。当通过下降沿检测电路141检测振荡信号vosc的下降沿fe4时,下降沿检测电路141输出检测信号ne。检测信号ne触发锁存器电路143以产生锁定信号lock。因此,如图2g中所示出的振荡检测电路140可在检测振荡信号vosc中的下降沿后输出锁定信号lock。

89.图2i示出根据一些实施例的振荡检测电路140的示意图。图2i中所示出的振荡检测电路与图2a中所示出的振荡检测电路之间的不同在于图2i中所示出的振荡检测电路被配置成在检测多个上升沿和下降沿对后输出锁定信号lock。图2i中所示出的振荡检测电路140包括下降沿检测电路141和上升沿检测电路145。关于下降沿检测电路141和上升沿检测电路145的详细描述可指以上参考图2a的描述。图2i中所示出的振荡检测电路140进一步包括被串联耦接的锁存器电路143_1、143_2、147_1、147_2,其中所述锁存器电路通过检测信号ne被触发,且触发锁存器电路147_1和锁存器电路147_2通过检测信号pe被触发。锁存器电路147_1可根据检测信号pe执行锁存操作以产生预锁定信号l1。锁存器电路143_1可根据检测信号ne锁存预锁定信号l1以产生预锁定信号l2;锁存器电路147_2可根据检测信号pe锁存预锁定信号l2以产生预锁定信号l3;且锁存器电路143_2可根据检测信号ne锁存预锁定信号l3以产生锁定信号lock。

90.参考图2i和图2j,振荡信号vosc可包括脉冲p51和脉冲p52,其中脉冲p51和脉冲p52中的每一个通过上升沿和下降边沿对形成。在检测振荡信号vosc的脉冲p51的上升沿和下降沿后,上升沿检测电路145和下降沿检测电路141分别在检测信号pe和检测信号ne上输出第一脉冲。检测信号pe和检测信号ne中的第一脉冲用以分别触发锁存器电路147_1和锁存器电路143_1的锁存操作。在检测振荡信号vosc的脉冲p52的上升沿和下降沿后,上升沿检测电路145和下降沿检测电路141分别在检测信号pe和检测信号ne上输出第二脉冲。检测信号pe和检测信号ne中的第二脉冲用以分别触发锁存器电路147_2和锁存器电路143_2的锁存操作。以这种方式,图2i中所示出的振荡检测电路140可在检测振荡信号vosc上的多个上升沿和下降沿对后输出锁定信号lock。应注意,锁存器电路的数目和锁存器电路的布置不限于图2i中绘示的数目和布置。举例来说,锁存器电路147_1和锁存器电路147_2的位置可交换到锁存器电路143_1和锁存器电路143_2的位置。另外,基于本设计需要,锁存器电路的数目可更多或更少。

91.图3示出根据一些实施例的控制电路120的示意图。控制电路120包括被串联耦接的多个计数器电路121_0~121_n-1,其中计数器电路121_0~121_n-1中的每一个被配置成产生偏置控制信号pbias的位值。举例来说,计数器电路121_0被配置成产生位pbias《0》,且计数器电路121_n-1被配置成产生位pbias《n-1》。控制电路120可接收反相重置信号rb,且当反相重置信号rb确证给控制电路120时被配置成重置计数器电路121_0~121_n-1。在一些实施例中,反相重置信号rb为图1中所绘示的重置信号rst的反相信号。

92.控制电路120可包括从控制电路120的外部接收时钟信号clk的时钟输入端。控制电路120可进一步包括耦接于计数器电路121_0~121_n-1与时钟输入端之间的开关122。在一些实施例中,开关122受锁定信号lock和反相锁定信号lockb控制,以耦接或解耦输入时钟端和计数器电路121_0~121_n-1。当锁定信号lock尚未确证给控制电路120时,开关122将输入时钟端被耦接到计数器电路121_0~121_n-1。因此,计数器电路121_0~121_n-1基于时钟信号clk而产生偏置控制信号pbias。当锁定信号lock被确证给控制电路120时,开关122从计数器电路121_0~121_n-1解耦时钟输入端。因此,计数器电路121_0~121_n-1的输

出保持不变,且锁定偏置控制信号pbias的配置。

93.图5绘示根据一些实施例的4位偏置控制信号pbias、锁定信号lock、时钟信号clk以及电源vdd的波形图。参考图3和图5,当电源vdd和时钟信号clk确证给控制电路120时,控制电路120的计数器电路分别产生位pbias《0》到位pbias《3》。如图5中所绘示,位pbias《0》到位pbias《3》为具有不同循环的振荡信号。举例来说,位pbias《1》的循环长于位pbias《0》的循环;位pbias《2》的循环长于位pbias《1》的循环;且位pbias《3》的循环长于位pbias《2》的循环。参考图3和图5,当确证锁定信号lock时,位pbias《0》到位pbias《3》锁定到在确证锁定信号lock的时序下的值。如图5中所绘示,在确证锁定信号lock的时序下,位pbias《0》和位pbias《1》锁定到逻辑值“1”,且位pbias《2》和位pbias《3》锁定到逻辑值0。

94.图4示出根据一些实施例的计数器电路121_x的示意图。计数器电路121_x可为图3中所绘示的计数器电路121_0~121_n-1中的任一个。计数器电路121_x可包括触发器电路1211和逻辑电路1213以及逻辑电路1215。在一些实施例中,触发器电路1211为jk触发器(jk flip-flop;jkff),逻辑电路1213为nand逻辑电路,且逻辑电路1215为not逻辑电路。jk触发器、nand逻辑电路以及not逻辑电路的结构在相关领域中为熟知的,因此下文省略关于这些组件的详细描述。

95.在一些实施例中,nand逻辑电路1213的输入端被耦接到jkff的输出端q,且nand逻辑电路1213的另一输入端被耦接到jkff的输入端j和输入端k。nand逻辑门的输出被输入到not逻辑电路,且not逻辑电路的输出充当计数器电路121_x的输出端nq。另外,jkff的输出端q充当计数器电路121_x的输出端q。位pbias《0》到位pbias《n-1》中的每一个从控制电路120的相应计数器电路的输出端q输出。

96.图6示出根据一些实施例的控制电路120的示意图。图6中所示出的控制电路与图3中所示出的控制电路之间的差别在于图6中所示出的控制电路进一步包括延迟电路123。延迟电路123接收锁定信号lock和时钟信号clk,且被配置成延迟锁定信号lock以产生延迟锁定信号lock_d1和延迟锁定信号lockb_d1。在一些实施例中,延迟电路123包括被配置成将锁定信号lock延迟一延迟时间段的至少一个延迟元件1231和延迟元件1233。延迟元件的数目和延迟元件的设计根据本设计需要来确定。延迟元件1233可输出延迟锁定信号lock_d1。另外,延迟电路123包括被耦接到1233的输出以产生延迟锁定信号lockb_d1的not逻辑电路。

97.图6中所示出的控制电路与图3中所示出的控制电路之间的另一不同在于图6中的控制电路的开关122受延迟锁定信号lock_d1和延迟锁定信号lockb_d1控制。通过延迟电路123所产生的延迟锁定信号lock_d1和延迟锁定信号lockb_d1提供给开关122以控制开关122的切换操作。以这种方式,控制电路120不在产生锁定信号lock之后立刻锁定偏置控制信号pbias的配置。实际上,控制电路120在锁定信号lock的确证的延迟时间段之后锁定偏置控制信号pbias的配置。因为振荡信号vosc的振荡可在振荡信号vosc的起始的延迟时间段之后更稳定,所以所产生的随机数的质量在延迟时间段之后锁定偏置控制信号的配置时较好。

98.图7为根据一些实施例的随机数产生器200的示意图。图7中所示出的随机数产生器200与图1中所示出的随机数产生器100之间的不同在于随机数产生器200进一步包括被耦接于振荡检测电路140与控制电路120之间的延迟电路170。延迟电路170从振荡检测电路

140接收锁定信号lock,且将锁定信号lock延迟一延迟时间段以产生延迟锁定信号dlock。本揭露不意图限制延迟电路170的结构。能够延迟信号的任何电路处于本揭露的范围内。延迟锁定信号dlock提供给控制电路120以锁定偏置控制信号pbias的配置。换句话说,随机数产生器200的控制电路120基于延迟锁定信号dlock而锁定偏置控制信号pbias的配置。因为振荡信号vosc的振荡可在振荡信号vosc的起始的延迟时间段之后更稳定,所以所产生的随机数的质量在延迟时间段之后锁定偏置控制信号的配置时较好。

99.图8示出根据一些实施例的随机数产生器300的示意图。图8中所示出的随机数产生器300与图1中所示出的随机数产生器100之间的不同在于随机数产生器300进一步包括被耦接于振荡检测电路140与锁存器电路160之间的延迟电路170。延迟电路170从振荡检测电路140接收锁定信号lock,且将锁定信号lock延迟一延迟时间段以产生延迟锁定信号dlock。延迟锁定信号dlock作为触发信号tri而被提供给锁存器电路160。因此,锁存器电路160基于延迟锁定信号dlock而锁存振荡信号vosc。换句话说,锁存器电路160在振荡信号vosc的起始的延迟时间段之后锁存振荡信号vosc。

100.图9示出根据一些实施例的随机数产生器400的示意图。图9中所示出的随机数产生器400与图1中所示出的随机数产生器100之间的不同在于随机数产生器400的振荡电路210进一步包括被串联耦接到选择器111的电阻器rs。电阻器rs可耦接于选择器111与参考端gnd之间,但本揭露不限于此。电阻器rs被配置成在振荡电路210的操作期间对流过选择器111的峰值瞬变电流进行箝位。电阻器rs可增加负载电容器112的放电时间,从而减小流过选择器111的峰值瞬变电流。举例来说,当电阻器rs被串联耦接到选择器111时,增加放电路径(形成通过负载电容器112、选择器111、电阻器rs以及参考端gnd)的电阻。因此,在放电操作期间负载电容器112的放电时间增加,且与不包括电阻器的实施例相比较流过选择器111的电流较低。图10中示出被串联耦接到振荡电路210中的电阻器rs的选择器111的iv曲线103。以这种方式,随机数产生器400的振荡电路210被保护以避免在振荡电路210的操作期间出现瞬变电流,且振荡电路210的可靠度被改良。

101.图11示出根据一些实施例的用于产生随机数的方法的流程图。在框1101中,在偏置控制信号的多个配置当中扫描偏置控制信号的配置。在框1103中,基于偏置控制信号而产生偏置电压。在框1105中,基于偏置电压和选择器的操作状态而产生振荡信号。选择器在导电状态与非导电状态之间交替地切换以产生振荡信号。在框1107中,检测振荡信号的起始且在检测振荡信号的起始后输出锁定信号。在框1109中,根据触发信号锁存振荡信号以输出随机数,其中在输出锁定信号之后确证触发信号,且根据锁定信号锁定偏置控制电压的配置。

102.图12示出根据一些实施例的随机数产生器(即图1中的随机数产生器100)的操作方法的流程图。随机数产生器可包括振荡电路、控制电路、动态标头电路、振荡检测电路以及锁存器电路。在框1201中,随机数产生器的控制电路扫描多个配置当中的偏置控制信号的配置。在框1203中,被耦接到控制电路的动态标头电路根据偏置控制信号产生偏置电压。在框1205中,振荡电路根据偏置电压产生振荡信号,其中振荡电路包括选择器和电容器,选择器在导电状态与非导电状态之间交替地切换且交替地充电和放电电容器以产生振荡信号。在框1207中,振荡检测电路检测振荡信号的起始,且在检测振荡信号的起始后输出锁定信号。根据锁定信号锁定偏置控制信号的配置。在框1209中,锁存器电路根据触发信号锁存

振荡信号以输出随机数。在通过振荡检测电路输出锁定信号之后确证触发信号。

103.根据一些实施例,引入一种随机数产生器,所述随机数产生器包括控制电路、振荡电路、动态标头电路、振荡检测电路以及锁存器电路。控制电路扫描多个配置当中的偏置控制信号的配置。动态标头电路基于偏置控制信号的配置而产生偏置电压。振荡电路基于偏置电压而产生振荡信号,其中包括于振荡电路中的选择器被配置成在非导电状态与导电状态之间交替地切换以产生振荡信号。振荡检测电路检测振荡信号的起始,且在检测振荡信号的起始后输出锁定信号。锁存器电路根据触发信号锁存振荡信号以输出随机数,其中在通过振荡检测电路输出锁定信号之后确证触发信号,且偏置控制信号的配置根据锁定信号被锁定。

104.根据一些实施例,振荡电路进一步包括电容器。当选择器处于非导电状态时电容器执行充电操作且当选择器处于导电状态时电容器执行放电操作。选择器包括具有保持电压及阈值电压的双向阈值开关。当跨越双向阈值开关的电压超出阈值电压时选择器从非导电状态切换到导电状态,且当跨越双向阈值开关的电压减小到低于保持电压时选择器从导电状态切换到非导电状态。

105.根据一些实施例,随机数产生器进一步包括电阻器。电阻器串联耦接到选择器。电阻器对流过选择器的峰值瞬变电流进行箝位。

106.根据一些实施例,动态标头电路包括多个晶体管。所述多个晶体管中的每一个由权重系数加权。所述多个晶体管中的每一个包括控制端、第一端以及第二端。控制端接收偏置控制信号。第一端耦接到参考节点。第二端,耦接到振荡电路。所述多个晶体管被配置成根据偏置控制信号产生偏置电压。振荡电路通过偏置电压被偏置。其中所述多个晶体管当中的晶体管的权重系数对应于晶体管的尺寸。

107.根据一些实施例,振荡检测电路包括上升沿检测电路以及上升沿锁存器。上升沿检测电路检测振荡信号的上升沿。上升沿锁存器耦接到上升沿检测电路。当上升沿检测电路检测到振荡信号的上升沿时,上升沿锁存器执行锁存操作以产生锁定信号。

108.根据一些实施例,振荡检测电路包括下降沿检测电路以及下降沿锁存器。下降沿检测电路检测振荡信号的下降沿。下降沿锁存器耦接到下降沿检测电路。当下降沿检测电路检测到振荡信号的下降沿时,下降沿锁存器执行锁存操作以产生锁定信号。

109.根据一些实施例,振荡检测电路包括上升沿检测电路、下降沿检测电路、上升沿锁存器以及下降沿锁存器。下降沿锁存器电耦接到上升沿锁存器。振荡检测电路响应于确定检测上升沿和下降沿对而产生锁定信号。

110.根据一些实施例,振荡检测电路包括上升沿检测电路、下降沿检测电路、多个上升沿锁存器以及多个下降沿锁存器。上升沿检测电路检测振荡信号的上升沿。下降沿检测电路检测振荡信号的下降沿。所述多个上升沿锁存器耦接到上升沿检测电路。所述多个下降沿锁存器耦接到下降沿检测电路。所述多个下降沿锁存器中的每一个电耦接到上升沿锁存器中的一个。所述振荡检测电路响应于确定检测多个上升沿和下降沿对而产生锁定信号。

111.根据一些实施例,随机数产生器进一步包括第一开关。第一开关耦接于振荡检测电路与振荡电路之间。第一开关根据锁定信号对振荡电路与振荡检测电路进行解耦。

112.根据一些实施例,随机数产生器进一步包括第一延迟电路。第一延迟电路耦接于控制电路与振荡检测电路之间。第一延迟电路延迟锁定信号以产生第一延迟锁定信号。控

制电路在通过第一延迟电路产生第一延迟锁定信号时锁定偏置控制信号。

113.根据一些实施例,随机数产生器进一步包括第二延迟电路。第二延迟电路耦接于锁存器电路与振荡检测电路之间。第二延迟电路延迟锁定信号以产生第二延迟锁定信号。第二延迟时钟信号为锁存器电路的触发信号。控制电路在通过振荡检测电路输出锁定信号时锁定偏置控制信号。

114.根据一些实施例,控制电路包括时钟输入端、多个计数器电路以及第二开关。时钟输入端接收时钟信号。所述多个计数器中的每一个根据时钟信号输出偏置控制信号的位值。第二开关耦接于所述多个计数器电路与时钟输入端之间。第二开关根据锁定信号对时钟输入端与所述多个计数器电路进行解耦以锁定偏置控制信号。

115.根据一些实施例,控制电路进一步包括第三延迟电路。第三延迟电路延迟锁定信号以产生第三延迟锁定信号。第二开关在通过第三延迟电路产生第三延迟锁定信号时对时钟输入端与所述多个计数器电路进行解耦。

116.根据一些实施例,引入一种产生随机数的方法。方法包括进行以下操作的步骤:扫描多个配置当中的偏置控制信号的配置;基于偏置控制信号的配置而产生偏置电压;基于偏置电压而产生振荡信号,其中选择器在非导电状态与导电状态之间交替地切换以产生振荡信号;检测振荡信号的起始且在检测振荡信号的起始后输出锁定信号;以及根据触发信号锁存振荡信号以输出随机数,其中在输出锁定信号之后确证触发信号,且偏置控制电压的配置根据锁定信号被锁定。

117.根据一些实施例,检测振荡信号的起始包括:检测振荡信号的上升沿或下降沿;以及响应于检测到振荡信号的上升沿或下降沿而输出锁定信号。

118.根据一些实施例,检测振荡信号的起始包括:检测振荡信号的上升沿和下降沿对;以及响应于检测到振荡信号的上升沿和下降沿对而输出锁定信号。

119.根据一些实施例,产生随机数的方法进一步包括:延迟锁定信号以产生延迟锁定信号。触发信号为延迟锁定信号。

120.根据一些实施例,引入一种随机数产生器的操作方法,所述随机数产生器包括振荡电路、控制电路、动态标头电路、振荡检测电路以及锁存器电路。操作方法包括进行以下操作的步骤:通过控制电路,扫描多个配置当中的偏置控制信号的配置;通过动态标头电路,根据偏置控制信号的配置产生偏置电压;通过振荡电路,根据偏置电压产生振荡信号,其中振荡电路包括选择器和电容器,选择器基于偏置电压而在导电状态与非导电状态之间交替地切换且交替地充电和放电电容器以产生振荡信号;通过振荡检测电路,检测振荡信号的起始,且通过振荡检测电路,在检测振荡信号的起始后输出锁定信号,其中偏置控制信号的配置根据锁定信号被锁定;以及通过锁存器电路,根据触发信号锁存振荡信号以输出随机数,其中在通过振荡检测电路输出锁定信号之后确证触发信号。

121.根据一些实施例,选择器包括表征为保持电压和阈值电压的双向阈值开关。当跨越双向阈值开关的电压超出阈值电压时,选择器从非导电状态切换到导电状态,其中跨越双向阈值开关的电压根据施加到振荡电路的偏置电压被确定。当跨越双向阈值开关的电压减小到低于保持电压时,选择器从导电状态切换到非导电状态。当选择器处于导电状态时,电容器被放电。当选择器处于非导电状态时,电容器被充电。

122.根据一些实施例,操作方法进一步包括:在通过振荡检测电路输出锁定信号之后,

根据锁定信号切断耦接于振荡检测电路与振荡电路之间的开关以从振荡电路解耦振荡检测电路。

123.前文概述若干实施例的特征使得所属领域的技术人员可更好地理解本揭露的各方面。所属领域的技术人员应了解,其可容易地将本揭露用作设计或修改用于实施本文中所引入的实施例的相同目的和/或实现相同优势的其它工艺和结构的基础。所属领域的技术人员还应认识到,这种等效构造并不脱离本揭露的精神和范围,且所属领域的技术人员可在不脱离本揭露的精神和范围的情况下在本文中作出各种改变、替代以及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1