一种任务处理方法及装置与流程

本技术涉及计算机,尤其涉及一种任务处理方法及装置。

背景技术:

1、在多样性算力时代,同一计算设备内可以具有多种类型的处理器,如中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)、数据计算单元(data processing unit,dpu)等,其中,cpu可以作为主处理器可以将用户任务调度至协处理器如gpu来处理。gpu作为协处理器可以用于执行cpu分配的任务。

2、协处理器中任务执行完成后,在第一种实现方式中,协处理器可以向cpu发送中断请求,以指示任务执行完成,cpu接收到中断请求后,便可以获取协处理器得到的数据处理结果,之后cpu使用该数据处理结果进行下一步处理。应理解的是,协处理器的数量可能是多个,在这种方式中,cpu需要接收各种协处理器的中断请求,频繁交互会占用大量的cpu资源,并且响应中断请求以及中断处理也存在时延较大的问题。

3、在第二种通用的实现方式中,协处理器不需要再发送中断请求来通知任务执行完成了,而是由cpu通过轮询方式来确定每个协处理器的任务是否执行完成。在这种方式中,由于没有中断的相关处理,因此时延性优于第一种实现方式,但轮询方式会长期占用cpu的较多资源,cpu占用率高。

技术实现思路

1、本技术提供一种任务处理方法及装置,用于降低唤醒线程的cpu资源开销。

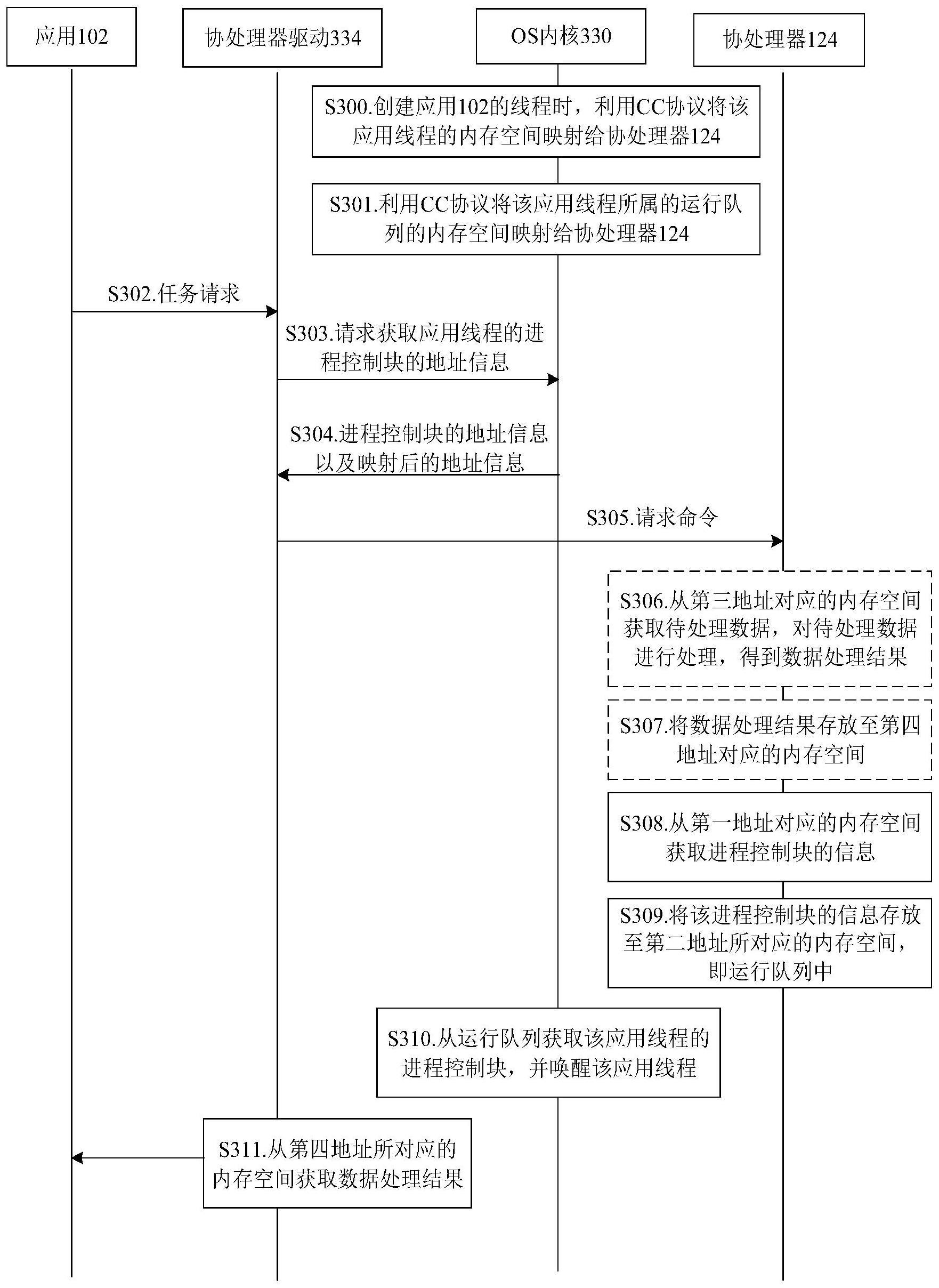

2、第一方面,本技术实施例提供了一种任务处理方法,该方法可以应用于计算设备(如服务器、主机等),该计算设备至少包括主处理器(如cpu)和协处理器(如gpu、dpu等),在该方法中,主处理器可以向协处理器发送请求命令,以用于请求协处理器处理任务,其中,主处理器维护有运行队列,请求命令用于指示第一地址和第二地址,第一地址为运行在主处理器上(与该任务相关)的线程的信息所在的内存空间的地址;第二地址为主处理器维护的运行队列所在的内存空间的地址;协处理器执行请求命令中指示的任务,并在该任务执行完成之后,将从第一地址对应的内存空间获取的线程的信息存放至所述第二地址所指示的运行队列中。

3、上述方式,主处理器向协处理器发送请求命令以请求协处理器处理任务,并通过该请求命令指示主处理器上(与该任务相关)的线程的信息的第一地址以及主处理器所维护的运行队列的第二地址,这样协处理器执行完成该任务后,可以从第一地址获取线程的信息,并根据第二地址将获取到的线程的信息存放至主处理器维护的运行队列中,这样不需要协处理器通过中断请求来通知主处理器协处理器的任务执行完成,也不需要主处理器询问协处理器任务是否执行完成,可以降低cpu的资源开销,有利于提高cpu利用率及系统性能。

4、在一种可能的实施方式中,请求命令包括第一地址和第二地址。或,请求命令包括第一地址,第一地址所指示的内存空间中存储的线程的信息包括第二地址。

5、上述方式,提供通过请求命令指示第一地址和第二地址的灵活性。

6、在一种可能的实施方式中,主处理器从运行队列获取线程的信息,并基于获取到的线程的信息唤醒该线程。

7、上述方式,协处理器执行任务完成后,将主处理器上与该任务相关的线程的信息存放至主处理器的运行队列,主处理器根据运行队列获取该线程的信息,并基于获取到的信息来唤醒线程。这样,主处理器不需要向协处理器询问任务是否执行完成,协处理器也不需要向主处理器发送中断请求,可以降低cpu的资源开销,提高cpu利用率及系统性能。

8、在一种可能的实施方式中,所述第一地址和所述第二地址均为通过缓存一致性(cache coherency,cc)协议映射给所述协处理器的。

9、上述方式,主处理器将第一地址、第二地址通过cc协议映射给协处理器,以使协处理器可以访问第一地址、第二地址所对应的内存空间,并且可以保证主处理器与协处理器关于该第一地址、第二地址对应的内存空间的数据一致性。

10、在一种可能的实施方式中,所述线程的信息为所述线程的线程控制块tcb信息。

11、上述方式,线程控制块信息可以唯一标识一个线程,并且包括主处理器管理该线程的信息,主处理器可以根据该线程控制块信息来唤醒线程。

12、在一种可能的实施方式中,该任务用于指示对待处理数据进行处理;

13、主处理器向协处理器发送用于指示第三地址的信息,第三地址为用于存储待处理数据的内存空间的地址;协处理器接收该用于指示第三地址的信息;协处理器执行所述任务,包括:从所述第三地址对应的内存空间获取所述待处理数据。

14、在一种可能的实施方式中,第三地址为通过cc协议映射给所述协处理器的。

15、上述方式,主处理器将第三地址通过cc协议映射给协处理器,以使协处理器可以访问第三地址所对应的内存空间,这样不需要主处理器将待处理的数据从第三地址对应的内存空间搬移至协处理器可访问的内存空间,降低cpu资源开销,并且可以保证主处理器和协处理器关于该第三地址对应的内存空间的数据一致性。

16、在一种可能的实施方式中,主处理器向协处理器发送中断下半部处理信息;中断下半部处理信息包括用于指示第四地址的信息,第四地址为用于存放任务的处理结果的内存空间的地址;协处理器接收中断下半部处理信息,并将得到的任务的处理结果存放至第四地址对应的内存空间。

17、在一种可能的实施方式中,第四地址为通过cc协议映射给所述协处理器的。

18、上述方式,主处理器通过cc协议将中断下半部流程中数据处理结果回传操作卸载到协处理器中,降低了对cpu处理能力的依赖,有利于提高cpu的资源利用率,且提升了协处理器的横向扩展(scale out)能力。

19、第二方面,本技术还提供了另一种计算设备,所述计算设备包括主处理器、协处理器和内存,内存,用于存储计算机程序指令;

20、所述主处理器执行所述内存中的程序指令执行上述第一方面或第一方面中任一可能的实现方式提供的主处理器执行的操作;所述协处理器执行上述第一方面或第一方面任一可能的实现方式提供的协处理器执行的操作。该计算设备可以为服务器等设备。

21、在一种可能的实施方式中,主处理器包括cpu;

22、协处理器包括gpu、dpu、特殊应用集成电路(application specific integratedcircuit,asic)、系统级芯片(system on chip,soc)、可编程门阵列(field programmablegate array,fpga)、嵌入式神经网络处理器(neural network processing unit,npu)、硬件计算引擎(hardware accelerator engine,hw ae)、硬件加速控制器(hardwareaccelerate controller,hac)、cpu。

23、第三方面,本技术还提供一种计算机芯片,所述芯片与存储器相连,所述芯片用于读取并执行所述存储器中存储的软件程序,执行上述第一方面以及第一方面的各个可能的实现方式中存储设备的操作,或执行上述第二方面以及第二方面的各个可能的实现方式中存储设备的操作。

24、上述第二方面至第三方面实现的有益效果,请参考第一方面的有益效果的描述,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!