基于PCIE总线的高速同步串口模块的制作方法

基于pcie总线的高速同步串口模块

技术领域

1.本发明涉及工业控制领域和军事通信领域,具体涉及一种工业控制领域和军事通信领域。

背景技术:

2.pci-express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3gio”,是由英特尔在2001年提出的,旨在替代旧的pci,pci-x和agp总线标准。

3.pcie属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(qos)等功能。pcie它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。pci express也有多种规格,从pci express x1到pci express x32,能满足将来一定时间内出现的低速设备和高速设备的需求。pci-express的接口是pcie3.0接口,其比特率为8gbps,约为上一代产品带宽的两倍,并且包含发射器和接收器均衡、pll改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。

4.串行通信可以分为同步通信和异步通信两类。所谓同步通信是指在约定的通信速率下,发送端和接收端的时钟信号频率和相位始终保持一致(同步),这就保证了通信双方在发送和接收数据时具有完全一致的定时关系。串行通信是指计算机主机与外设之间以及主机系统与主机系统之间数据的串行传送。使用串口通信时,发送和接收到的每一个字符实际上都是一次一位的传送的,每一位为1或者为0。

5.同步串口通信把许多字符组成一个信息组,或称为信息帧,每帧的开始用同步字符来指示。由于发送和接收的双方采用同一时钟,所以在传送数据的同时还要传送时钟信号,以便接收方可以用时钟信号来确定每个信息位。

6.同步串口通信要求在传输线路上始终保持连续的字符位流,若计算机没有数据传输,则线路上要用专用的“空闲”字符或同步字符填充。

7.同步串口通信传送信息的位数几乎不受限制,通常一次通信传的数据有几十到几千个字节,通信效率较高。但它要求在通信中保持精确的同步时钟,所以其发送器和接收器比较复杂,成本也较高,一般用于传送速率要求较高的场合。

8.目前,仍有很多场合应用着同步串口,例如军用飞机、航空制导、导弹与火箭运输等,因此地面测试设备也需要着同步串口。现在计算机和工控机pcie接口已经成为最基本的外设接口,通过此接口实现扩展同步串口进行通信与测试,应成为一个很好的方法。

技术实现要素:

9.本发明的目的在于克服现有技术中的缺陷,提供一种基于pcie总线的高速同步串口模块。

10.本发明的技术方案如下:

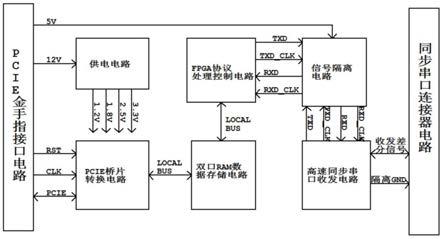

11.一种基于pcie总线的高速同步串口模块,其特征在于,包括pcie金手指接口电路、供电电路、pcie桥片转换电路、双口ram数据存储电路、fpga协议处理控制电路、信号隔离电路、高速同步串口收发电路和同步串口连接器电路,所述fpga协议处理控制电路、双口ram数据存储电路、pcie桥片转换电路、pcie金手指接口电路依次相连;所述fpga协议处理控制电路与所述信号隔离电路相连,所述信号隔离电路通过高速同步串口收发电路与所述同步串口连接器电路相连;所述pcie金手指接口电路采用标准pcie x1金手指板型,从金手指连接处引入系统12v电源、5v电源、复位信号rst、同源差差分pcie参考时钟和pcie总线;所述pcie桥片转换电路的功能用于将pcie串行总线转换成local bus并行总线并完成pcie枚举与映射;所述双口ram数据存储电路用于存储通信数据,挂载两片idt公司的70v28芯片,其中一片作为发送数据缓存,另一片作为接收数据缓存;所述pcie桥片转换电路将需要的发送数据通过local bus写入发送数据缓存,将接收的数据从接收数据缓存中读取;所述fpga协议处理控制电路则恰好相反,通过译码产生local bus读取发送数据缓存,写入接口数据缓存,由此实现两侧数据交换。

12.本发明的优点和有益效果是:通过pcie金手指引入pcie高速串行总线,经过协议转换实现高速同步串口总线协议,并通过高速收发器实现与外部设备通信,实现pcie总线转换高速同步串口,具有集成度高、可操作性强,方便携带、稳定高效等特点。

附图说明

13.图1为本发明提供的一种基于pcie总线的高速同步串口模块的连接原理框图。

具体实施方式

14.以下结合具体实施例对本发明作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

15.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

16.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个部件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明中的具体含义。

17.如图1所示,一种基于pcie总线的高速同步串口模块,包括pcie金手指接口电路、供电电路、pcie桥片转换电路、双口ram数据存储电路、fpga协议处理控制电路、信号隔离电路、高速同步串口收发电路和同步串口连接器电路,所述fpga协议处理控制电路、双口ram数据存储电路、pcie桥片转换电路、pcie金手指接口电路依次相连;所述fpga协议处理控制电路与所述信号隔离电路相连,所述信号隔离电路通过高速同步串口收发电路与所述同步串口连接器电路相连;所述pcie金手指接口电路采用标准pcie x1金手指板型,从金手指连

接处引入系统12v电源、5v电源、复位信号rst、同源差差分pcie参考时钟和pcie总线;所述pcie桥片转换电路的功能用于将pcie串行总线转换成local bus并行总线并完成pcie枚举与映射;所述双口ram数据存储电路用于存储通信数据,挂载两片idt公司的70v28芯片,其中一片作为发送数据缓存,另一片作为接收数据缓存;所述pcie桥片转换电路将需要的发送数据通过local bus写入发送数据缓存,将接收的数据从接收数据缓存中读取;所述fpga协议处理控制电路则恰好相反,通过译码产生local bus读取发送数据缓存,写入接口数据缓存,由此实现两侧数据交换。

18.所述供电电路是提供本装置dc电源转换的电路,采用adi公司的ltm4644 dc转换模块实现12v主电源的转换,向后级电路提供3.3v、2.5v、1.8v和1.2v次级电源。

19.所述pcie桥片转换电路的功能用于将pcie串行总线转换成local bus并行总线并完成pcie枚举与映射,采用plx公司的pex8311芯片,设备设备上电时通过spi接口从eeprom读取配置信息,完成枚举过程。之后将pcie总线转换成local bus总线,读写后级存储电路。

20.所述fpga协议处理控制电路用于通信数据交换、协议转换和数据与时钟同步;采用altera公司的ep3c5144i7 fpga实现协议数据处理,具体为发送数据时将需发送的数据进行打包,并通过pll锁相环产生发送同步时钟txd_clk,在同步时钟txd_clk上升沿将数据按照串口协议依次将txd发送。接收数据时,在外部输入同步时钟rxd_clk的激励下,依次沿时钟上升沿锁存接收rxd数据。

21.所述信号隔离电路用于将高速同步串口收发电路与前级各数字电路隔离,通过金升阳b0505隔离电源将5v电源转换产生5v隔离电源,供电给ti的隔离芯片iso7240和后级高速同步串口收发电路,数字测采用3.3v供电,其收发信号和时钟经此实现本装置与外部电气隔离。

22.所述高速同步串口收发电路用于进行数据与时钟接收和发送,将单端信号和差分信号进行转换传输,采用一片美信公司的max490芯片将rxd和txd转换成标准rs422差分信号进行传输,再采用一片美信公司的max490芯片将rxd_clk和txd_clk转换成标准rs422差分信号进行传输。

23.所述同步串口连接器电路用于将本模块与外部设备连接,采用标准db9接口将rxd、txd、rxd_clk、txd_clk四组差分信号和隔离电源gnd与外部设备连接在一起,实现数据通信。

24.以上对本发明的实例进行了详细说明,但所述内容仅为本发明的较佳实施例,不能被认为用于限定本发明的实施范围。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1