先进先出数据处理装置及数据处理方法与流程

1.本发明涉及了集成电路设计领域,具体的是一种先进先出数据处理装置及数据处理方法。

背景技术:

2.在集成电路设计的soc设计领域以及各种模块级设计领域中,尤其是在总线接口主设备设计中,写到总线接口模块的数据,通用的接口:如valid、 ready、data等信号交互,而data通常都是从先进先出存储器(fifo memory)直接输出到总线,其中的data包括但不仅限于:传输的数据wdata,以及每个数据对应的标识号wid,每一笔传输数据的最后数据标志位wlast信号,该数据对应的数据位/字节有效信号wstrb,等等。由于先进先出存储器本身的输出延时大,加上后端布局布线后电路延时更大导致时序很难收敛。而ready信号通常是由其它模块传入,经过各级模块逻辑以及布局布线后延时也很大,所述ready信号通常作为先进先出存储器的读条件的一部分,使得先进先出存储器的建立时间(setup time)很难收敛。

3.因此,本领域技术人员亟需研发一种低延时、高效率的先进先出数据处理装置/方法,在不影响总线接口模块的传输效率下,能够有效解决由ready信号和数据data造成先进先出存储器的时序难以收敛的问题。

4.应所述注意,上面对技术背景的介绍只是为了方便对本发明的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本发明的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现要素:

5.为了克服现有技术中的缺陷,本发明实施例提供了一种先进先出数据处理装置及数据处理方法。

6.本技术实施例公开了:一种先进先出数据处理装置,包括:准备信号延时调整模块、先进先出读信号产生模块、第一冲突缓存处理模块、第二冲突缓存处理模块、输出缓存模块和输出成功标志产生模块。准备信号延时调整模块耦接于总线接口模块,用于接收来自总线接口模块的数据准备好信号i_ready,并产生准备调整信号pipe_ready,其中当数据准备好信号i_ready为有效时,输出准备调整信号pipe_ready。先进先出读信号产生模块耦接于准备信号延时调整模块和先进先出存储器,用于接收来自准备信号延时调整模块的数据准备好信号i_ready以及来自先进先出存储器的先进先出空信号i_fifo_empty,并产生先进先出读信号o_fifo_rd,其中,当检测到先进先出空信号i_fifo_empty为无效、且准备调整信号pipe_ready为有效时,则输出先进先出读信号o_fifo_rd。第一冲突缓存处理模块耦接于先进先出存储器和总线接口模块,用于接收来自先进先出存储器的先进先出输入数据i_fifo_data以及来自总线接口模块的数据准备好信号i_ready,并产生第一冲突缓存有效信号backup1_valid。第二冲突缓存处理模块耦接于先进先出存储器和总线接口模块,用

于接收来自先进先出存储器的先进先出输入数据i_fifo_data以及来自总线接口模块的数据准备好信号i_ready,并产生第二冲突缓存有效信号backup2_valid。输出缓存模块耦接于先进先出存储器、第一冲突缓存处理模块和第二冲突缓存处理模块,用于接收来自先进先出存储器的先进先出输入数据i_fifo_data,并产生输出缓存有效信号o_pipe_valid。输出成功标志产生模块耦接于第一冲突缓存处理模块、第二冲突缓存处理模块、输出缓存模块和总线接口模块,用于接收第一冲突缓存有效信号backup1_valid、第二冲突缓存有效信号backup2_valid、输出缓存有效信号o_pipe_valid和数据准备好信号i_ready,并产生输出成功标志信号o_valid给总线接口模块,其中,当数据准备好信号i_ready为有效、且输出缓存有效信号o_pipe_valid为有效时,则输出成功标志o_valid为有效,否则,输出成功标志o_valid为无效。

7.进一步地,先进先出读信号产生模块还用于接收一流水线允许再读先进先出信号pipe_cap_lt3,其中,当检测到先进先出空信号i_fifo_empty为无效、且准备调整信号pipe_ready为有效或者流水线允许再读先进先出信号pipe_cap_lt3为有效时,则先进先出读信号产生模块输出先进先出读信号o_fifo_rd。

8.进一步地,先进先出存储器在接收到先进先出读信号o_fifo_rd后,下一时钟周期输出先进先出输入数据i_fifo_data;以及当先进先出输入数据i_fifo_data为有效时,利用寄存器将先进先出读信号o_fifo_rd直接打拍作为一先进先出数据有效信号fifo_valid。

9.进一步地,在写端处理时,当先进先出数据有效信号fifo_valid为有效、且输出缓存有效信号o_pipe_valid为有效、且数据准备好信号i_ready为无效或者冲突缓存(backup_valid)有效且当前冲突缓存写指针等于0时,则第一冲突缓存写信号为有效,否则,第一冲突缓存写信号为无效;在写端处理时,当先出数据有效信号fifo_valid为有效、且输出缓存有效信号o_pipe_valid为有效、且数据准备好信号i_ready为无效或者冲突缓存(backup_valid)有效且当前冲突缓存写指针等于1时,则第二冲突缓存写信号为有效,否则,第二冲突缓存写信号为无效;以及当第一冲突缓存写信号及/或第二冲突缓存写信号为有效时,进行冲突缓存处理。

10.进一步地,当第一冲突缓存写信号backup1_wr为有效时,更新第一冲突缓存处理模块的数据,并寄存拉高第一冲突缓存有效信号backup1_valid,否则,在第一冲突缓存读信号为有效时,寄存清零第一冲突缓存有效信号backup1_valid;当第二冲突缓存写信号backup2_wr为有效时,更新第二冲突缓存处理模块的数据,并寄存拉高第二冲突缓存有效信号backup2_valid,否则,在第二冲突缓存读信号为有效时,寄存清零第二冲突缓存有效信号backup2_valid;当冲突缓存读指针backup_rd_ptr等于0时,冲突缓存有效信号backup_valid等于第一冲突缓存有效信号backup1_valid,且冲突缓存数据backup_data等于第一冲突缓存数据backup1_data,否则,冲突缓存有效信号backup_valid等于所述第二冲突缓存有效信号backup2_valid,且冲突缓存数据backup_data等于第二冲突缓存数据backup2_data。

11.进一步地,在读端处理时,当输出缓存有效信号o_pipe_valid为有效、且数据准备好信号i_ready为有效或者冲突缓存backup_valid等于0时,则第一冲突缓存读信号为有效,否则,第一冲突缓存读信号为无效;在读端处理时,当先进先出数据有效信号fifo_

valid为有效、且输出缓存有效信号o_pipe_valid为有效、且数据准备好信号i_ready为无效或者冲突缓存backup_valid等于0且当前冲突缓存读指针等于1时,则第二冲突缓存读信号为有效,否则,第二冲突缓存读信号为无效;以及当第一冲突缓存读信号及/或第二冲突缓存读信号为有效时,进行冲突缓存处理。

12.进一步地,当第一冲突缓存读信号为有效、且第一冲突缓存写信号为无效时,则清零第一冲突缓存有效信号backup1_valid,否则,保持第一冲突缓存有效信号backup1_valid;以及当第二冲突缓存读信号为有效、且第二冲突缓存写信号为无效时,则清零第二冲突缓存有效信号backup2_valid,否则,保持第二冲突缓存有效信号backup2_valid。

13.进一步地,第一条件包括:数据准备好信号i_ready为有效、且输出缓存有效信号o_pipe_valid为有效;第二条件包括:先进先出数据有效信号fifo_valid为无效、且输出缓存有效信号o_pipe_valid为无效、且第一/第二冲突缓存有效信号backup1_valid/backup2_valid为无效;其中,当上述两个条件有一个满足时,则输出缓存写信号为有效,否则,输出缓存写信号为无效。

14.进一步地,当输出缓存写信号为有效、且第一/第二冲突缓存有效信号backup1_valid/backup2_valid为有效时,则寄存器更新输出缓存有效信号o_pipe_valid为有效,且寄存器更新输出缓存数据o_data等于冲突缓存数据backup_data;以及当输出缓存写信号为有效、且第一/第二冲突缓存有效信号backup1_valid/backup2_valid为无效时,则寄存器更新输出缓存有效信号o_pipe_valid等于输入数据有效信号i_valid, 且寄存器更新输出缓存数据o_data等于先进先出输入数据i_fifo_data。

15.本技术实施例公开了:一种数据处理方法,包括以下步骤:接收来自总线接口模块的数据准备好信号i_ready,并产生准备调整信号pipe_ready,其中当数据准备好信号i_ready为有效时,输出准备调整信号pipe_ready;接收数据准备好信号i_ready以及来自先进先出存储器的先进先出空信号i_fifo_empty,并产生先进先出读信号o_fifo_rd,其中,当检测到先进先出空信号i_fifo_empty为无效、且准备调整信号pipe_ready为有效时,则输出先进先出读信号o_fifo_rd;接收来自先进先出存储器的先进先出输入数据i_fifo_data以及数据准备好信号i_ready,并产生第一冲突缓存有效信号backup1_valid;接收先进先出输入数据i_fifo_data以及数据准备好信号i_ready,并产生第二冲突缓存有效信号backup2_valid;接收先进先出输入数据i_fifo_data,并产生输出缓存有效信号o_pipe_valid;以及接收第一冲突缓存有效信号backup1_valid、第二冲突缓存有效信号backup2_valid、输出缓存有效信号o_pipe_valid和数据准备好信号i_ready,并产生输出成功标志信号o_valid给总线接口模块,其中,当数据准备好信号i_ready为有效、且输出缓存有效信号o_pipe_valid为有效时,则输出成功标志o_valid为有效,否则,输出成功标志o_valid为无效。

16.借由以上的技术方案,本发明的有益效果如下:本发明的先进先出数据处理装置及数据处理方法,通过将读先进先出存储器的时序转化为通用的(如:总线接口模块可以使用的)valid和ready交互机制,整个数据处理装置和数据处理方法,对总线接口模块的输入

准备信号寄存打拍处理,提供了输出缓冲和冲突缓冲,以及对整个控制进行无气泡流水线处理,使得先进先出存储器和总线接口模块的数据交互高效,且没有气泡。总线接口模块的i_ready和先进先出存储器之间的关键路径被切断,且先进先出存储器的数据到总线接口模块的关键路径也被切断,如此一来,时序很容易收敛。换句话说,本发明不但解决数据准备好信号i_ready作为先进先出存储器的读信号的时序难收敛的问题,还解决data作为先进先出存储器的输出时序难收敛的问题,且不影响总线接口模块的传输效率。

17.为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附图式,作详细说明如下。

附图说明

18.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

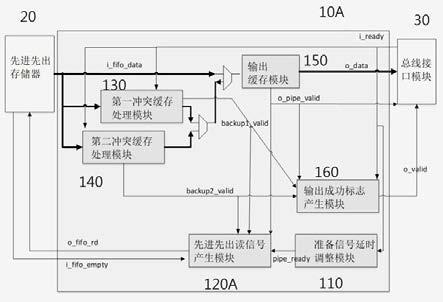

19.图1是本发明一实施例中的一种先进先出数据处理装置的框架图。

20.图2是本发明一实施例中的一种数据处理方法的流程图。

21.图3是本发明第一冲突缓存处理模块和第二冲突缓存处理模块在写端处理的步骤的流程图。

22.图4是本发明第一冲突缓存处理模块和第二冲突缓存处理模块在读端处理的步骤的流程图。

23.图5是本发明输出缓存模块的步骤的流程图。

24.图6是本发明一实施例中的时序波形图。

25.以上附图的附图标记:10a、先进先出数据处理装置;20、先进先出存储器;30、总线接口模块;110、准备信号延时调整模块;120a、先进先出读信号产生模块;130、第一冲突缓存处理模块;140、第二冲突缓存处理模块;150、输出缓存模块;160、输出成功标志产生模块;i_ready、数据准备好信号;pipe_ready、准备调整信号;i_fifo_empty、先进先出空信号;o_fifo_rd、先进先出读信号;i_fifo_data、先进先出输入数据;backup1_valid、第一冲突缓存有效信号;backup2_valid、第二冲突缓存有效信号;o_pipe_valid、输出缓存有效信号;o_valid、输出成功标志信号;pipe_cap_lt3、流水线允许再读先进先出信号;fifo_valid、先进先出数据有效信号;backup_data、冲突缓存数据;o_data、输出缓存数据;i_valid、输入有效信号;s310

‑

s360、s510

‑

s570、s610

‑

s680、s710

‑

s760、步骤。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

27.需要说明的是,在本发明的描述中,术语“第一”、“第二”等仅用于描述目的和区别

类似的对象,两者之间并不存在先后顺序,也不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

28.请参考图1,图1是本发明一实施例中的一种先进先出数据处理装置10a的框架图。如图1所示,先进先出数据处理装置10a耦接于先进先出存储器(fifo memory)20与总线接口模块30之间。先进先出数据处理装置10a包括准备信号延时调整模块110、先进先出读信号产生模块120a、第一冲突缓存处理模块130、第二冲突缓存处理模块140、输出缓存模块150和输出成功标志产生模块160。准备信号延时调整模块120a耦接于总线接口模块30,用于接收来自总线接口模块30的数据准备好信号i_ready,并产生一准备调整信号pipe_ready,其中当数据准备好信号i_ready为有效(即,等于1)时,输出准备调整信号pipe_ready。先进先出读信号产生模块120a耦接于准备信号延时调整模块110和先进先出存储器20,用于接收来自准备信号延时调整模块110的数据准备好信号i_ready以及来自先进先出存储器20的先进先出空信号i_fifo_empty,并产生先进先出读信号o_fifo_rd,其中,当检测到先进先出空信号i_fifo_empty为无效(即,等于0)、且准备调整信号pipe_ready为有效(即,等于1)时,输出先进先出读信号(o_fifo_rd)。第一冲突缓存处理模块130耦接于先进先出存储器20和总线接口模块30,用于接收来自先进先出存储器的先进先出输入数据i_fifo_data以及来自总线接口模块30的数据准备好信号i_ready,并产生第一冲突缓存有效信号backup1_valid。第二冲突缓存处理模块140耦接于先进先出存储器20和总线接口模块30,用于接收来自先进先出存储器20的先进先出输入数据i_fifo_data以及来自总线接口模块30的数据准备好信号i_ready,并产生第二冲突缓存有效信号backup2_valid。输出缓存模块150耦接于先进先出存储器20、第一冲突缓存处理模块130和第二冲突缓存处理模块140,用于接收来自先进先出存储器20的先进先出输入数据i_fifo_data,并产生缓存数据有效信号o_pipe_valid。输出成功标志产生模块160耦接于第一冲突缓存处理模块130、第二冲突缓存处理模块140、输出缓存模块150和总线接口模块30,用于接收第一冲突缓存有效信号backup1_valid、第二冲突缓存有效信号backup2_valid、缓存数据有效信号o_pipe_valid和数据准备好信号i_ready,并产生输出成功标志信号o_valid给总线接口模块30,其中,当总线接口模块30的数据准备好信号i_ready为有效、且输出缓存模块150的缓存数据有效信号o_pipe_valid为有效时,输出成功标志o_valid为有效(即,等于1),否则,输出成功标志o_valid为无效(即,等于0)。此外,先进先出读信号产生模块120a还包括一内部信号,即流水线允许再读先进先出信号pipe_cap_lt3。

29.其中,当检测到先进先出空信号i_fifo_empty为无效(即,等于0)、且准备调整信号(pipe_ready)为有效(即,等于1)或者流水线允许再读先进先出信号pipe_cap_lt3为有效(即,等于1)时,则先进先出读信号产生模块120b输出先进先出读信号o_fifo_rd。于本实施例中,流水线允许再读先进先出信号pipe_cap_lt3表示可用存储空间加上先进先出存储器20输出的有效数据总数量低于3,其真值表如下表一所示:

先进先出存储器20在接收到先进先出读信号o_fifo_rd后,下一时钟周期输出先进先出输入数据i_fifo_data。当先进先出输入数据i_fifo_data为有效时,利用一寄存器将先进先出读信号o_fifo_rd直接打拍作为一先进先出数据有效信号fifo_valid。

30.请一并参考图1和图2,图2是本发明一实施例中的一种数据处理方法的流程图。图2的数据处理方法包括以下步骤:步骤s310:接收总线接口模块的数据准备好信号i_ready,并产生准备调整信号pipe_ready,其中当数据准备好信号为有效时,输出准备调整信号pipe_ready。

31.步骤s320:接收总线接口模块的数据准备好信号i_ready、先进先出存储器的先进先出空信号i_fifo_empty和流水线允许再读先进先出信号pipe_cap_lt3,并产生先进先出读信号o_fifo_rd,其中,当检测到先进先出空信号i_fifo_empty为无效、且准备调整信号pipe_ready为有效或者流水线允许再读先进先出信号pipe_cap_lt3为有效时,则输出先进先出读信号o_fifo_rd。

32.步骤s330:当输入第一冲突缓存数据backup1_data接收先进先出输入数据i_fifo_data以及数据准备好信号i_ready,判断第一冲突缓存有效信号backup1_valid。

33.步骤s340:接收先进先出存储器的先进先出输入数据i_fifo_data以及总线接口模块的数据准备好信号i_ready,并产生第二冲突缓存有效信号backup2_valid。

34.步骤s350:接收先进先出存储器的先进先出输入数据i_fifo_data,并产生输出缓存有效信号o_pipe_valid。

35.步骤s360:接收第一冲突缓存有效信号backup1_valid、第二冲突缓存有效信号backup2_valid、输出缓存有效信号o_pipe_valid和数据准备好信号i_ready,并产生输出成功标志信号o_valid给总线接口模块,其中,当数据准备好信号i_ready为有效、且输出缓存有效信号o_pipe_valid为有效时,则输出成功标志o_valid为有效,否则,输出成功标志o_valid为无效。

36.请注意,步骤s310是由准备信号延时调整模块110所执行,步骤s320是由先进先出读信号产生模块120a所执行,步骤s330是由第一冲突缓存处理模块130所执行,步骤s340是

由第二冲突缓存处理模块140所执行,步骤s350是由输出缓存模块150所执行,步骤s360是由输出成功标志产生模块160所执行。

37.接下来,进一步说明第一冲突缓存处理模块130和第二冲突缓存处理模块140的功能与运作。由于这两个模块功能与运作相同,统一进行说明,并拆分成写端处理(如图5)和读端处理(如图6)。

38.请参考图3,图3是本发明第一冲突缓存处理模块和第二冲突缓存处理模块在写端处理的步骤的流程图。图3的写端处理包括以下步骤:步骤s510:当先进先出数据有效信号fifo_valid为有效、且输出缓存有效信号o_pipe_valid为有效、且数据准备好信号i_ready为无效或者冲突缓存backup_valid有效且当前冲突缓存写指针等于0时,则第一/第二冲突缓存写信号为有效,否则,第一/第二冲突缓存写信号为无效。

39.步骤s520:判断第一/第二冲突缓存写信号是否为有效。当第一/第二冲突缓存写信号为有效时,执行步骤s530;否则,执行步骤s570。

40.步骤s530:判断冲突缓存写指针等于0。当冲突缓存写指针等于0,执行步骤s540;否则,执行步骤s550。

41.步骤s540:第一冲突缓存写信号backup1_wr等于1,更新第一冲突缓存处理模块的数据,寄存拉高第一冲突缓存有效信号backup1_valid,否则,在第一冲突缓存读信号有效时寄存清零第一冲突缓存有效信号backup1_valid。

42.步骤s550:第二冲突缓存写信号backup2_wr等于1,更新第二冲突缓存处理模块的数据,寄存拉高第二冲突缓存有效信号backup2_valid,否则,在第二冲突缓存读信号有效时,寄存清零第一冲突缓存有效信号backup1_valid。

43.步骤s560:当

ꢀ“

冲突缓存写信号”有效,则更新

ꢀ“

冲突缓存写指针”为该指针的值取反,否则,保持

ꢀ“

冲突缓存写指针”的值。

44.步骤s570:结束。

45.请参考图4,图4是本发明第一冲突缓存处理模块和第二冲突缓存处理模块在读端处理的步骤的流程图。图4的读端处理包括以下步骤:步骤s610:当数据有效且输出缓存有效信号o_pipe_valid有效、且

ꢀ“

总线接口模块没有准备好,或者冲突缓存无效”,则第一/第二冲突缓存读信号有效,否则,第一/第二冲突缓存读信号为无效。

46.步骤s620:判断第一/第二冲突缓存读信号是否为有效。当第一/第二冲突缓存读信号为有效时,执行步骤s630;否则,执行步骤s680。

47.步骤s630:判断第一/第二冲突缓存读指针等于0。当第一/第二冲突缓存读指针等于0时,执行步骤s640;否则,执行步骤s650。

48.步骤s640:第一冲突缓存读信号赋值为1,如果第一冲突缓存写信号为无效,则清零第一冲突缓存有效信号backup1_valid,否则,保持第一冲突缓存有效信号backup1_valid。

49.步骤s650:第二冲突缓存读信号赋值为1,如果第二冲突缓存写信号为无效,则清零第二冲突缓存有效信号backup2_valid,否则,保持第二冲突缓存有效信号backup2_valid。

50.步骤s660:当冲突缓存读指针为0时,输出冲突缓存数据backup_data为第一冲突缓存数据,否则输出冲突缓存数据backup_data为第二冲突缓存数据。

51.步骤s670:当冲突缓存读信号有效,则更新冲突缓存读指针为该读指针的值取反,否则,保持冲突缓存读指针的值。

52.步骤s680:结束。

53.请参考图5,图5是本发明一实施例中输出缓存模块的步骤的流程图。图5包括以下步骤:步骤s710:第一条件包括:数据准备好信号i_ready为有效、且输出缓存有效信号o_pipe_valid为有效;第二条件包括:先进先出数据有效信号fifo_valid为无效、且输出缓存有效信号o_pipe_valid为无效、且冲突缓存有效信号backup_valid为无效;其中,当上述两个条件有一个满足时,则输出缓存写信号为有效,否则,输出缓存写信号为无效。

54.步骤s720:判断输出缓存写信号是否为有效。当输出缓存写信号为有效时,执行步骤s730;否则,执行步骤s760。

55.步骤s730:判断冲突缓存有效信号backup_valid是否为有效。当第一/第二冲突缓存有效信号backup1_valid/backup2_valid为有效时,执行步骤s740;否则,执行步骤s750。

56.步骤s740:寄存器更新输出缓存有效信号o_pipe_valid为有效,且寄存器更新输出缓存数据o_data等于冲突缓存数据backup_data。

57.步骤s750:寄存器更新输出缓存有效信号o_pipe_valid等于输入有效信号i_valid, 且寄存器更新输出缓存数据o_data等于先进先出输入数据i_fifo_data。

58.步骤s760:结束。

59.请参考图6,图6是本发明一实施例中的时序波形图。如图6所示,在第三个时钟周期,由于先进先出存储器20不空(即,先进先出空信号i_fifo_empty等于0),则产生了先进先出读信号o_fifo_rd,持续了3个时钟周期。先进先出存储器20的先进先出输入数据i_fifo_data输入d0、d1、d2,然后填满了输出缓存模块、第一冲突缓存处理模块和第二冲突缓存处理模块,输出缓存模块的数据o_data为d0, 此后,由于先进先出存储器20一直有数据,即使总线接口模块30连续读数据,而输出缓存模块、第一冲突缓存处理模块和第二冲突缓存处理模块的数据一直是满的,且不会溢出。在第九个时钟周期,总线接口模块30发出数据准备好信号i_ready,此时输出缓存有效信号o_pipe_valid为有效,则输出成功标志信号o_valid为有效,只要总线接口模块30要数据,而先进先出存储器20一直不空,则能在当前时刻实时给出数据,没有时钟周期延时,也没有效率损失。在第十五个时钟周期,总线接口模块30将数据准备好信号i_ready拉低,导致输出成功标志信号o_valid拉低,且在第十六个时钟周期输出给先进先出存储器20的先进先出读信号o_fifo_rd拉低,后来随着总线接口模块30的数据准备好信号i_ready拉高则上述两个信号随时变化,无论总线接口模块30的数据准备好信号i_ready如何变化,只要先进先出存储器20有足够数据,本发明的先进先出数据处理装置及数据处理方法都能够高效率实时供应数据,没有气泡,且不会造成流水线数据溢出。且总线接口模块30的数据准备好信号i_ready和先进先出存储器20之间的关键路径被切断,且先进先出存储器20的先进先出输入数据i_fifo_data到总线接口模块30的关键路径也被切断,时序很容易收敛。

60.本发明具体实施例提供一种先进先出数据处理装置及数据处理方法,通过将读先

进先出存储器20的时序转化为通用的(如:总线接口总线接口模块30可以使用的)valid和ready交互机制,且流水无气泡,效率高。

61.上述的本发明实施例可在各种硬件、软件编码或两者组合中进行实施。例如,本发明的实施例也可为在数据信号处理器(digital signal processor,dsp)中执行上述方法的程序代码。本发明也可涉及计算机处理器、数字信号处理器、微处理器或现场可编程门 阵列(field programmable gate array,fpga)执行的多种功能。可根据本发明配置上述处理器执行特定任务,其通过执行定义了本发明揭示的特定方法的机器可读软件代码或 固件代码来完成。可将软件代码或固件代码发展为不同的程序语言与不同的格式或形式。 也可为不同的目标平台编译软件代码。然而,根据本发明执行任务的软件代码与其他类型配置代码的不同代码样式、类型与语言不脱离本发明的精神与范围。

62.借由以上的技术方案,本发明的有益效果如下:本发明的先进先出数据处理装置及数据处理方法,通过将读先进先出存储器20的时序转化为通用的(如:总线接口模块30可以使用的)valid和ready交互机制,整个数据处理装置和数据处理方法,对总线接口模块30的输入准备信号寄存打拍处理,提供了输出缓冲和冲突缓冲,以及对整个控制进行无气泡流水线处理,使得先进先出存储器20和总线接口模块30的数据交互高效,且没有气泡。总线接口模块30的i_ready和先进先出存储器20之间的关键路径被切断,且先进先出存储器20的数据到总线接口模块30的关键路径也被切断,如此一来,时序很容易收敛。换句话说,本发明不但解决数据准备好信号i_ready作为先进先出存储器20的读信号的时序难收敛的问题,还解决data作为先进先出存储器20的输出时序难收敛的问题,且不影响总线接口模块30的传输效率。

63.本发明中应用了具体实施例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1