一种内部总线地址重映射装置的制作方法

1.本发明涉及数据存储技术领域,尤其是一种内部总线地址重映射装置。

背景技术:

2.目前,soc等系统的数据存储量越发庞大,对读写速度及效率的要求也越来越高,但在一些高速存储设备中,由于数据量增多,行、bank、page的数量也越来越多,这就导致在数据读写过程中存在部分跨行、跨bank操作。在这类操作过程中,由于各存储器设备自身原因,会导致数据读写效率的极大降低,进而导致读写速度变慢。

3.部分从设备会根据自身读写规则对地址进行手动排序,通过多次尝试,从而找出一种较为合适的重映射方式,但该方式以下弊端:1、需用户主动尝试各种地址排列方式,费时费力,且对用户技术水平有一定的要求;2、地址重排限制较大,可选配置方式较少,并不一定能够找到最优的地址排序方式。

技术实现要素:

4.针对上述问题,本发明提供了一种内部总线地址重映射装置,通过对地址的重映射、重排序,从而找到一种更为适合存储设备的地址映射方式,使得主设备在访问从设备时,减少频繁跨行、跨bank操作,从而提高数据的访问效率,提高主从设备的数据读写速度。

5.一种内部总线地址重映射装置,所述地址重映射装置部署于总线地址输出与存储器地址输入之间,对总线的读写地址进行训练,调整地址映射规则后,输出至存储器地址输入端口。

6.所述地址重映射装置包括地址输入输出单元、效率比较单元,所述地址输入输出单元与所述效率比较单元双向连接;所述效率比较单元在既定训练量下,通过计算比较得出变化率相对较低的地址重映射窗口位宽所在位置;所述地址输入输出单元接收地址总线的地址输入,根据所述效率比较单元计算出的变化率相对较低的地址重映射窗口位宽所在位置,将输入地址进行重映射排列后输出至存储器地址输入端口。

7.进一步的,所述效率比较单元包括对应n条地址线的n个变化次数计数器,n-c+1个窗口内变化总次数计数器,其中c为窗口位宽;当训练量达到既定量时,寄存n-c+1个窗口内变化总次数计数器中的数值并进行比较,找到其中的最小值,更新最小和数据位置count_min并输出训练结果。

8.进一步的,所述地址重映射装置还包括与所述效率比较单元连接的寄存器单元,用于工作模式配置、地址重映射窗口位置配置和地址有效位宽配置、训练量配置,工作模式包括训练模式和自定义模式两种。

9.当装置处于训练模式时,所述效率比较单元首先读取用户通过寄存器配置的训练量、地址有效位宽、窗口大小,然后在既定训练量下,通过计算比较得出变化率相对较低的地址重映射窗口位宽所在位置,将效率最高的地址重映射方式写回所述寄存器单元,完成训练,最终后续数据读写由所述地址输入输出单元按照训练后的配置进行地址重映射。

10.当装置处于自定义模式时,所述效率比较单元首先读取用户通过寄存器配置的地址有效位宽、窗口大小、地址重映射窗口位置,然后后续数据读写由所述地址输入输出单元按照自定义的配置进行地址重映射。

11.进一步的,总线地址输出与存储器地址输入之间级联部署多个地址重映射装置,每个地址重映射装置在自定义模式下,数据按照用户自定义的配置进行传输,对不同地址重映射装置进行不同的自定义配置,使得连续数据乱序地存储于存储器中。

12.本发明既可以根据训练得到的效率最高的地址重映射方式进行地址映射排列方案调整,又可以根据用户自定义的配置重映射排列地址窗口,给予用户更自由的选择,以及更大的地址调整空间,有效提高访问效率;本发明除用于提高访问效率之外,还可以用于数据加密传输,在数据传输时,通过自定义配置寄存器,将连续数据按乱序地址进行保存,通过多个地址重映射装置级联,提高保密性。

附图说明

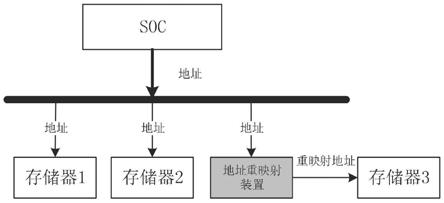

13.图1是实施例1中的地址重映射装置部署情况示意图;

14.图2是实施例1中的地址重映射装置内部结构框图;

15.图3是效率比较单元的训练机制示意图;

16.图4是效率比较单元的效率训练时序意图;

17.图5是实施例2中的地址重映射装置内部结构框图;

18.图6是两种工作模式下的流程图;

19.图7是实施例3中的地址重映射装置部署情况示意图。

具体实施方式

20.下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

21.实施例1

22.一种内部总线地址重映射装置,如图1所示,部署于总线地址输出与存储器地址输入之间,对总线的读写地址进行训练,调整地址映射规则后,输出至存储器地址输入端口。所述地址重映射装置如图2所示,包括地址输入输出单元、效率比较单元,所述地址输入输出单元与所述效率比较单元双向连接。

23.所述效率比较单元在既定训练量(用户自定义)下,通过计算比较得出变化率相对较低的地址重映射窗口位宽所在位置。本实施例结合图3,对效率比较单元的工作过程进行展开阐述。

24.从图3可以看出,所述效率比较单元包括对应40条地址线addr0-39的40个变化次数计数器cnt0-39,37个窗口内变化总次数计数器count0-36(窗口大小为4)。

25.图4给出效率比较单元的效率训练时序意图,在clk1-clk9时,输入地址addr0、addr1、addr2、addr3变化如图4所示,各地址线计数器cnt0、cnt1、cnt2、cnt3开始对该位地

址的变化进行计数。以cnt0为例,在clk1和clk2时,addr0为1,因而cnt0一直为0;在clk3时,addr0变为0,此时计数器cnt0变为1(addr0变化1次);在clk4时,addr0变为1,此时计数器cnt0变为2(addr0又变化1次)。

26.与此同时,37个窗口内变化总次数计数器count0-36同步进行求和计算:

27.count0=cnt0+cnt1+cnt2+cnt3;

28.count1=cnt1+cnt2+cnt3+cnt4;

29.count2=cnt2+cnt3+cnt4+cnt5;

30.......

31.count35=cnt35+cnt36+cnt37+cnt38;

32.count36=cnt36+cnt37+cnt38+cnt39。

33.当训练量达到既定量时,寄存37个窗口内变化总次数计数器中的数值并进行比较,找到其中的最小值,更新最小和数据位置count_min并输出训练结果,此即变化率相对较低的地址重映射窗口位宽所在位置,对应效率最高的地址重映射方式。所述效率比较单元将效率最高的地址重映射方式写回所述寄存器单元,完成训练。最终后续数据读写由所述地址输入输出单元按照训练后的配置进行地址重映射。

34.所述地址输入输出单元接收地址总线的地址输入,按照训练后的配置,将输入地址进行重映射排列后输出至存储器地址输入端口。

35.实施例2

36.所述地址重映射装置还包括与所述效率比较单元连接的寄存器单元,如图5所示,用于工作模式配置、地址重映射窗口位置配置和地址有效位宽配置、训练量配置,工作模式包括训练模式和自定义模式两种,工作流程图如图6所示。

37.当装置处于训练模式时,所述效率比较单元首先读取用户通过寄存器配置的训练量、地址有效位宽、窗口大小,然后在既定训练量下,通过计算比较得出变化率相对较低的地址重映射窗口位宽所在位置,将效率最高的地址重映射方式写回所述寄存器单元,完成训练,最终后续数据读写由所述地址输入输出单元按照训练后的配置进行地址重映射。此种工作模式下,对地址无变化要求,通过训练调整地址映射规则。

38.当装置处于自定义模式时,所述效率比较单元首先读取用户通过寄存器配置的地址有效位宽、窗口大小、地址重映射窗口位置,然后后续数据读写由所述地址输入输出单元按照自定义的配置进行地址重映射。此种工作模式下,需要对地址变化规则有一定了解,无需训练,但需要用户进行寄存器的自定义配置。

39.地址重映射窗口可配置,地址有效位宽可配置,使得地址重映射装置能够适配多种存储器媒介。

40.实施例3

41.总线地址输出与存储器地址输入之间级联部署多个地址重映射装置,如图7所示,每个地址重映射装置在自定义模式下,数据按照用户自定义的配置进行传输,对不同地址重映射装置进行不同的自定义配置,使得连续数据乱序地存储于存储器中,可以达到数据加密传输的效果。

42.显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所

获得的所有其他实施例,都应属于本发明保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1