一种闪存通道控制器运行方法、装置、设备及存储介质与流程

1.本发明涉及计算机技术领域,特别涉及一种闪存通道控制器运行方法、装置、设备及存储介质。

背景技术:

2.目前,固态硬盘中通常采用多个闪存通道控制器(flash channel controller,fcc)并行技术来实现多通道数据的并发读写操作,以提高固体盘整体的读写性能。闪存通道控制器读写操作的大致流程是先由硬件通知闪存通道控制器内某个逻辑处理单元(logical unit number,lun)有待处理消息,lun找到对应上下文(context,cnt)并获取消息内容,然后利用上下文接收并解析消息,并根据消息内容执行对应命令,执行完成后返回完成消息。但由于现有技术中默认单个逻辑处理单元对应单个上下文,即每个逻辑处理单元必须串行执行待处理的命令,在大压力场景下,单个逻辑处理单元极有造成阻塞,导致随机读时会影响产品层关键指标iops(input/output operations per second,每秒进行读写操作的次数)。

技术实现要素:

3.有鉴于此,本发明的目的在于提供一种闪存通道控制器运行方法、装置、设备及介质,能够提高闪存通道控制器的消息处理效率,提高闪存通道控制器的并发度。其具体方案如下:

4.第一方面,本技术公开了一种闪存通道控制器运行方法,包括:

5.为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;

6.当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;

7.通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。

8.可选的,所述为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,包括:

9.分别为闪存通道控制器内的每个逻辑处理单元创建对应的n个独立的上下文,使每个所述逻辑处理单元对应的上下文的数量相同;其中,n大于或等于2。

10.可选的,所述分别为闪存通道控制器内的每个逻辑处理单元创建对应的n个独立的上下文,包括:

11.在所述闪存通道控制器上电初始阶段,分别为闪存通道控制器内的每个逻辑处理单元创建对应的2个相互独立的上下文,以创建得到每个所述逻辑处理单元与该逻辑处理单元对应的2个上下文之间的映射关系,并将所述映射关系的属性设置为锁死不可修改。

12.可选的,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目

标上下文,包括:

13.所述目标逻辑处理单元通过遍历自身对应的所有上下文,获取自身对应的每个上下文的状态信息;所述状态信息包括闲置状态和工作状态;

14.从状态信息为闲置状态的上下文中随机选取一个上下文作为所述目标上下文。

15.可选的,所述通过所述目标逻辑处理单元修改所述目标上下文的状态信息,包括:

16.通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述工作状态;

17.相应的,在所述目标上下文处理完成所述待处理消息之后,还包括:

18.通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述闲置状态。

19.可选的,所述利用所述目标上下文处理所述待处理消息,包括:

20.利用所述目标上下文连续处理所述待处理消息对应的所有待处理任务。

21.可选的,所述为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文之后,还包括:

22.通过所述闪存通道控制器监测自身对应的所有上下文的资源状态;

23.当监测到所述上下文存在运行异常时,停用所述上下文并生成告警;所述运行异常包括所述上下文的资源被异常占用。

24.第二方面,本技术公开了一种闪存通道控制器运行装置,包括:

25.上下文配置模块,用于为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;

26.目标上下文确定模块,用于当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;

27.消息处理模块,用于通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。

28.第三方面,本技术公开了一种电子设备,包括:

29.存储器,用于保存计算机程序;

30.处理器,用于执行所述计算机程序,以实现前述的闪存通道控制器运行方法。

31.第四方面,本技术公开了一种计算机可读存储介质,用于存储计算机程序;其中计算机程序被处理器执行时实现前述的闪存通道控制器运行方法。

32.本技术中,为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。由上可见,通过为为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,即每个逻辑处理单元都对应有目标数量的上下文,且上述目标数量大于或等于2,从而当逻辑处理单元接收到待处理消息时,根据对应的上下文的状态信息选择出可以执行消息处理的目标上下文,利用该目标上下文进行上述待处理消息的处理,且由于不同上下文之间是独立的互不影响,在逻辑处理单元的某一个上下文在处理消息时,如果仍有待处理消息,则可以直接

使用另一个上下文处理,由此可以实现逻辑处理单元对待处理消息的并发处理,提高了闪存通道控制器的并发度,以实现更高性能,同时也提升了cpu资源利用率及效率。

附图说明

33.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

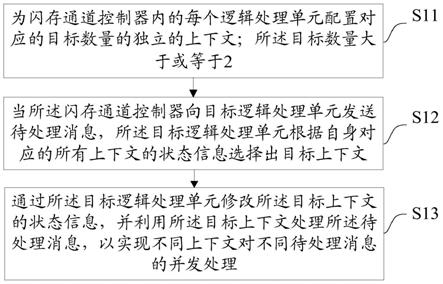

34.图1为本技术提供的一种闪存通道控制器运行方法流程图;

35.图2为本技术提供的一种闪存通道控制器运行装置结构示意图;

36.图3为本技术提供的一种电子设备结构图。

具体实施方式

37.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.现有技术中,每个逻辑处理单元必须串行执行待处理的命令,在大压力场景下,单个逻辑处理单元极有造成阻塞,导致随机读时会影响产品层关键指标iops,为了克服上述技术问题,本技术提出一种闪存通道控制器运行方法,能够提高闪存通道控制器的消息处理效率,提高闪存通道控制器的并发度。

39.本技术实施例公开了一种闪存通道控制器运行方法,参见图1所示,该方法可以包括以下步骤:

40.步骤s11:为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2。

41.本实施例中,首先在闪存通道控制器上电初始化阶段,为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,其中,上述目标数量大于或等于2。即每个逻辑处理单元至少对应有两个以上的上下文,且该上下文是独立的,即不同上下文之间是独立的,且一个上下文仅对应唯一一个逻辑处理单元。

42.本实施例中,所述为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,可以包括:分别为闪存通道控制器内的每个逻辑处理单元创建对应的n个独立的上下文,使每个所述逻辑处理单元对应的上下文的数量相同;其中,n大于或等于2。即本实施例中,为每个逻辑处理单元均配置n个对应的上下文,使每个逻辑处理单元包含的上下文的数量相同。

43.本实施例中,所述分别为闪存通道控制器内的每个逻辑处理单元创建对应的n个独立的上下文,可以包括:在所述闪存通道控制器上电初始阶段,分别为闪存通道控制器内的每个逻辑处理单元创建对应的2个相互独立的上下文,以创建得到每个所述逻辑处理单元与该逻辑处理单元对应的2个上下文之间的映射关系,并将所述映射关系的属性设置为锁死不可修改。可以理解的是,在闪存通道控制器上电初始化阶段,通过结合芯片手册,为

每个逻辑处理单元重新进行上下文分配,为每个逻辑处理单元创建对应的两个上下文的映射关系,且该映射关系一旦确定则不再修改。也就是说,考虑到上下文资源也存在数量限制,为合理且最大化利用上下文资源,本实施例中为每个逻辑处理单元映射了两个上下文cnt0、cnt1,即单个逻辑处理单元对应两个上下文,但一个上下文仅对应一个逻辑处理单元。

44.步骤s12:当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文。

45.本实施例中,当上述闪存通道控制器向目标逻辑处理单元发送待处理消息,目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文,即从可以使用的所有上下文中选择出空闲的上下文作为目标上下文,以便处理新接收到的待处理消息。

46.本实施例中,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文,可以包括:所述目标逻辑处理单元通过遍历自身对应的所有上下文,获取自身对应的每个上下文的状态信息;所述状态信息包括闲置状态和工作状态;从状态信息为闲置状态的上下文中随机选取一个上下文作为所述目标上下文。即每个逻辑处理单元在检测到有待处理消息时,遍历该逻辑处理单元所对应的所有上下文,如果有上下文处于闲置(idle)状态,则获取该上下文作为目标上下文。

47.步骤s13:通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。

48.本实施例中,确定出目标上下文后,通过其所属的目标逻辑处理单元修改目标上下文的状态信息,并利用目标上下文处理上述待处理消息,以实现不同上下文对不同待处理消息的并发处理。即确定出目标上下文后通过其所属的目标逻辑处理单元修改目标上下文的状态信息,修改目标上下文状态从闲置状态到工作状态(busy),并利用该上下文开始处理消息。由此,考虑到单个逻辑处理单元多plane场景,执行操作时必须串行执行命令,通过有效利用上下文资源,通过对逻辑处理单元与上下文的重新映射,为每个逻辑处理单元映射多个上下文,实现了多并发处理机制,可以更有效的利用cpu,充分利用了资源也提升了效率。

49.本实施例中,所述通过所述目标逻辑处理单元修改所述目标上下文的状态信息,可以包括:通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述工作状态;相应的,在所述目标上下文处理完成所述待处理消息之后,还包括:通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述闲置状态。即当上下文处理完消息、发送完成消息后,修改状态从busy到idle,释放资源,以备下次调用。

50.本实施例中,所述利用所述目标上下文处理所述待处理消息,可以包括:利用所述目标上下文连续处理所述待处理消息对应的所有待处理任务。也就是说,本实施例中对于关联的待处理消息需要由一个固定的上下文连续处理,即对于连续消息需保证是同一上下文连续处理。

51.本实施例中,所述为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文之后,还可以包括:通过所述闪存通道控制器监测自身对应的所有上下文的资源状态;当监测到所述上下文存在运行异常时,停用所述上下文并生成告警;所述运行异常包括所述上下文的资源被异常占用。上述运行异常包括不同上下文之间的交互使用,

或上下文被除存在映射关系外的其余逻辑处理单元占用,即每个逻辑处理单元负责维护所属上下文的资源及状态,保证不同上下文间不可以交互使用,且各个上下文不区分优先级。

52.由上可见,本实施例中为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。由上可见,通过为为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,即每个逻辑处理单元都对应有目标数量的上下文,且上述目标数量大于或等于2,从而当逻辑处理单元接收到待处理消息时,根据对应的上下文的状态信息选择出可以执行消息处理的目标上下文,利用该目标上下文进行上述待处理消息的处理,且由于不同上下文之间是独立的互不影响,在逻辑处理单元的某一个上下文在处理消息时,如果仍有待处理消息,则可以直接使用另一个上下文处理,由此可以实现逻辑处理单元对待处理消息的并发处理,提高了闪存通道控制器的并发度,以实现更高性能,同时也提升了cpu资源利用率及效率。

53.相应的,本技术实施例还公开了一种闪存通道控制器运行装置,参见图2所示,该装置包括:

54.上下文配置模块11,用于为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;

55.目标上下文确定模块12,用于当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;

56.消息处理模块13,用于通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。

57.由上可见,本实施例中为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文;所述目标数量大于或等于2;当所述闪存通道控制器向目标逻辑处理单元发送待处理消息,所述目标逻辑处理单元根据自身对应的所有上下文的状态信息选择出目标上下文;通过所述目标逻辑处理单元修改所述目标上下文的状态信息,并利用所述目标上下文处理所述待处理消息,以实现不同上下文对不同待处理消息的并发处理。由上可见,通过为为闪存通道控制器内的每个逻辑处理单元配置对应的目标数量的独立的上下文,即每个逻辑处理单元都对应有目标数量的上下文,且上述目标数量大于或等于2,从而当逻辑处理单元接收到待处理消息时,根据对应的上下文的状态信息选择出可以执行消息处理的目标上下文,利用该目标上下文进行上述待处理消息的处理,且由于不同上下文之间是独立的互不影响,在逻辑处理单元的某一个上下文在处理消息时,如果仍有待处理消息,则可以直接使用另一个上下文处理,由此可以实现逻辑处理单元对待处理消息的并发处理,提高了闪存通道控制器的并发度,以实现更高性能,同时也提升了cpu资源利用率及效率。

58.在一些具体实施例中,所述上下文配置模块11,还可以用于分别为闪存通道控制

器内的每个逻辑处理单元创建对应的n个独立的上下文,使每个所述逻辑处理单元对应的上下文的数量相同;其中,n大于或等于2。

59.在一些具体实施例中,所述上下文配置模块11,还可以用于在所述闪存通道控制器上电初始阶段,分别为闪存通道控制器内的每个逻辑处理单元创建对应的2个相互独立的上下文,以创建得到每个所述逻辑处理单元与该逻辑处理单元对应的2个上下文之间的映射关系,并将所述映射关系的属性设置为锁死不可修改。

60.在一些具体实施例中,所述目标上下文确定模块12具体可以包括:

61.状态信息获取单元,用于所述目标逻辑处理单元通过遍历自身对应的所有上下文,获取自身对应的每个上下文的状态信息;所述状态信息包括闲置状态和工作状态;

62.选取单元,用于从状态信息为闲置状态的上下文中随机选取一个上下文作为所述目标上下文。

63.在一些具体实施例中,所述消息处理模块13具体可以包括:

64.第一状态修改单元,用于通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述工作状态;

65.第二状态修改单元,用于通过所述目标逻辑处理单元将所述目标上下文的状态信息修改为所述闲置状态。

66.在一些具体实施例中,所述消息处理模块13,还可以用于利用所述目标上下文连续处理所述待处理消息对应的所有待处理任务。

67.在一些具体实施例中,所述闪存通道控制器运行装置具体可以包括:

68.资源状态监测单元,用于通过所述闪存通道控制器监测自身对应的所有上下文的资源状态;

69.告警单元,用于当监测到所述上下文存在运行异常时,停用所述上下文并生成告警;所述运行异常包括所述上下文的资源被异常占用。

70.进一步的,本技术实施例还公开了一种电子设备,参见图3所示,图中的内容不能被认为是对本技术的使用范围的任何限制。

71.图3为本技术实施例提供的一种电子设备20的结构示意图。该电子设备20,具体可以包括:至少一个处理器21、至少一个存储器22、电源23、通信接口24、输入输出接口25和通信总线26。其中,所述存储器22用于存储计算机程序,所述计算机程序由所述处理器21加载并执行,以实现前述任一实施例公开的闪存通道控制器运行方法中的相关步骤。

72.本实施例中,电源23用于为电子设备20上的各硬件设备提供工作电压;通信接口24能够为电子设备20创建与外界设备之间的数据传输通道,其所遵循的通信协议是能够适用于本技术技术方案的任意通信协议,在此不对其进行具体限定;输入输出接口25,用于获取外界输入数据或向外界输出数据,其具体的接口类型可以根据具体应用需要进行选取,在此不进行具体限定。

73.另外,存储器22作为资源存储的载体,可以是只读存储器、随机存储器、磁盘或者光盘等,其上所存储的资源包括操作系统221、计算机程序222及包括待处理消息在内的数据223等,存储方式可以是短暂存储或者永久存储。

74.其中,操作系统221用于管理与控制电子设备20上的各硬件设备以及计算机程序222,以实现处理器21对存储器22中海量数据223的运算与处理,其可以是windows server、

netware、unix、linux等。计算机程序222除了包括能够用于完成前述任一实施例公开的由电子设备20执行的闪存通道控制器运行方法的计算机程序之外,还可以进一步包括能够用于完成其他特定工作的计算机程序。

75.进一步的,本技术实施例还公开了一种计算机存储介质,所述计算机存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器加载并执行时,实现前述任一实施例公开的闪存通道控制器运行方法步骤。

76.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

77.结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(ram)、内存、只读存储器(rom)、电可编程rom、电可擦除可编程rom、寄存器、硬盘、可移动磁盘、cd-rom、或技术领域内所公知的任意其它形式的存储介质中。

78.最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

79.以上对本发明所提供的一种闪存通道控制器运行方法、装置、设备及介质进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1