包括eFuse模块的芯片、电子装置和芯片烧录控制方法与流程

包括efuse模块的芯片、电子装置和芯片烧录控制方法

技术领域

1.本发明涉及集成电路技术领域,尤其涉及一种包括efuse模块的芯片、电子装置和芯片烧录控制方法。

背景技术:

2.目前各架构mcu、mpu、cpu等控制单元的安全加密功能普遍采用内建efuse模块的方式实现。内建efuse模块可以用来装载芯片id、芯片生产封装以及密钥等等信息。此类信息有时需要厂商在cp、ft环节写入,有些则需要最终用户写入,因此与efuse烧录相关的引脚必须在封装中引出。同时需要满足非烧录一方无法读出的已烧录信息的要求。随着电子产品技术的不断发展迭代,客户对安全性要求越来越高,封装尺寸越来越苛刻。现有封装技术以及相关的基板、pcb水平并不足以在成熟量产产品中引出足够多的可复用引脚。在保证客户信息安全和灵活性的基础上大规模压缩测试引脚成为芯片设计厂商的必然选择。

技术实现要素:

3.为了解决现有包括efuse模块的芯片引脚过多的技术问题,本发明提供一种包括efuse模块的芯片、电子装置和芯片烧录控制方法,在保证芯片信息安全的同时减少芯片的引脚,降低芯片的封测成本。

4.本发明一方面提供一种包括efuse模块的芯片,其特征在于,包括:

5.efuse模块、串并转换单元、烧录信号分析单元、控制单元和引脚,

6.所述引脚包括串行输入信号引脚、烧录读取控制信号引脚和输出信号引脚,

7.所述控制单元用于当通过所述烧录读取控制信号引脚接收到烧录读取控制信号时,将所述芯片设置在烧录验证模式;

8.所述串并转换单元用于当通过所述烧录读取控制信号引脚接收到烧录读取控制信号时,将通过所述串行输入信号引脚输入的串行输入信号转换为并行输入地址信号;

9.所述efuse模块用于将经所述串并转换单元转换的并行输入地址信号对应位进行烧录处理;

10.所述烧录信号分析单元用于基于经所述efuse模块处理的烧录信号生成相应的烧录状态信号,所述烧录状态信号通过所述输出信号引脚被输出;以及

11.位于所述串并转换单元与所述efuse模块之间的第一多路选择器,所述第一多路选择器分别与所述串并转换单元、所述控制单元连接。

12.本发明优选的实施方式中,所述烧录信号分析单元为奇偶校验单元,所述奇偶校验单元用于将所述efuse模块的多位宽q做奇偶校验,所述输入信号引脚传输两次不同奇偶校验结果对应的输入信号,基于信号烧录前和信号烧录之后读取所述奇偶校验单元输出奇偶校验结果的变化,判断所述efuse模块是否烧录成功。

13.本发明优选的实施方式中,所述烧录信号分析单元为烧录信号比较单元,并根据两次不同的输入信号,所述烧录信号比较单元用于基于烧录前后两次读取信号进行比对,

并根据对比结果是否不同,确定所述efuse模块是否烧录成功。

14.本发明进一步优选的实施方式中,所述串行输入信号引脚为双线串行通信接口,并且双线串行通信接口接收自定义的串行协议通过芯片烧录装置发送串行地址及地址的锁存信号;并且所述第一选择器用于切换烧录动作的地址和读取动作的地址;其中,读取地址会读取两次,且地址相同,烧录和读取的地址位数不同。

15.本发明优选的实施方式中,所述控制单元、所述efuse模块分别与烧录读取控制信号引脚连接,所述烧录读取控制信号包含编程信号、读取信号和/或动作有效信号。

16.本发明优选的实施方式中,每次芯片上电或者复位之后,每当芯片被切换为芯片烧录验证模式时,所述控制单元还用于对所述efuse模块内容进行一次查空并记录结果;在芯片烧录装置第一次读取任意地址时,所述控制单元将查空结果经由第二多路选择器通过所述输出信号引脚送出。

17.本发明进一步优选的实施方式中,所述烧录信号分析单元、所述控制单元分别与第二多路选择器连接,所述第二多路选择器与所述输出信号引脚连接;并且当上电或者复位后第一次读取任意地址,所述第二多路选择器送出查空信号,之后的烧录、读取组合操作中,所述第二多路选择器送出烧录位变化标志或者奇偶效验位。

18.本发明第二方面还提供一种电子装置,其特征在于,包括:

19.如第一方面提供的任意一种所述的包括efuse模块的芯片,以及

20.与所述芯片连接的外围电路。

21.本发明第三方面还提供一种芯片烧录控制方法,应用于芯片,其特征在于,所述芯片为如第一方面提供的任意一种芯片,所述方法包括:

22.接收烧录读取控制信号,并且当芯片被切换为芯片烧录验证模式时,控制单元对efuse模块内容进行一次查空并记录结果;在芯片烧录装置第一次读取任意地址时,所述控制单元将查空结果通过输出信号引脚送出;

23.所述控制单元接收到烧录读取控制信号引脚传输的烧录读取控制信号时,所述输入信号引脚传输的串行输入信号被输入至所述串并转换单元,所述串并转换单元转换后的处理信号被输入至所述efuse模块;

24.所述烧录信号分析单元基于所述efuse模块处理的烧录信号是否满足预定条件,输出烧录状态信号,并通过所述输出信号引脚输出所述烧录状态信号。

25.本发明第四方面还提供一种芯片烧录控制方法,应用于芯片烧录装置,其特征在于,所述芯片为如第一方面提供的任意一种芯片,包括:

26.向所述芯片输入烧录读取控制信号,

27.接收所述芯片输出的烧录状态信号,

28.根据所述烧录状态信号是否满足预定的要求,判断所述芯片的烧录信息是否成功。

29.因此,本发明提供的上述技术方案中,通过在芯片内部设置有与efuse模块电连接的串并转换单元可以直接接收串行输入信号引脚,并且在芯片内部设置烧录信号分析单元,可以直接在芯片内部完成烧录是否成功的比对,无需将efuse模块内部的烧录数据信号传输至芯片外部,从而在保证芯片信息安全的同时减少芯片的引脚,降低芯片的封测成本。

30.发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书变得显

而易见,或者通过实施本发明的技术方案而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构和/或流程来实现和获得。

附图说明

31.图1为现有技术中一种soc芯片中efuse模块的引脚示意图。

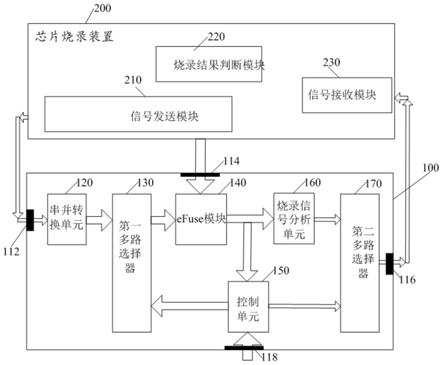

32.图2为本发明实施例提供一种包括efuse模块的芯片和芯片烧录装置的连接示意图。

33.图3为本发明实施例提供另一种包括efuse模块的芯片和芯片烧录装置的连接示意图。

34.图4为本发明实施例提供又一种包括efuse模块的芯片和芯片烧录装置的连接示意图。

35.图5为本发明实施例提供一种efuse模块数据烧录原理示意图。

36.图6为本发明实施例提供一种电子装置的结构框图。

37.图7为本发明实施例提供一种应用于芯片的芯片烧录控制方法流程图。

38.图8为本发明实施例提供一种应用于芯片烧录装置的芯片烧录控制方法流程图。

39.图9为现有efuse模块在第一模式下数据烧录原理示意图。

40.图10为现有efuse模块数据烧录中第一模式下数据烧录原理示意图。

41.图11为现有efuse模块在第二模式下数据烧录原理示意图。

42.图12为现有efuse模块数据烧录中第二模式下数据烧录原理示意图。

具体实施方式

43.以下将结合附图及实施例来详细说明本发明的实施方式,借此对本发明如何应用技术手段来解决技术问题,并达成技术效果的实现过程能充分理解并据以实施。需要说明的是,这些具体的说明只是让本领域普通技术人员更加容易、清晰理解本发明,而非对本发明的限定性解释;并且只要不构成冲突,本发明中的各个实施例以及各实施例中的各个特征可以相互结合,所形成的技术方案均在本发明的保护范围之内。

44.另外,在附图的流程图示出的步骤可以在诸如一组控制器可执行指令的控制系统中执行,并且,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤。

45.下面通过附图和具体实施例,对本发明的技术方案进行详细描述:

46.如图1所示为一种现有芯片(例如,soc芯片,soc为system on ch模块的缩写,称为系统级芯片,也有称片上系统)设计中使用的efuse模块模块,下文实施例中的芯片也可以为包括但不限于soc类型的芯片。图1中所示为一个常用的4k efuse,相关的引脚均需要通过pin_mux引至复用的gpio或者复用的各通用串口引脚上,如果换为其它容量的efuse地址线和数据线位宽会做相应调整,其它控制线和电源、地、烧录电源的引脚需求不变。部分端口的说明如下表:

[0047][0048][0049]

如果要满足集成此efuse模块的封装片烧录及验证功能,需要占用io资源如下:

[0050]

地址总线:a=12个

[0051]

数据总线:q=32个

[0052]

必要烧录读取控制信号:strobe+load+pgenb+ps+mr=5个

[0053]

烧录电源及复用选择信号:若干不计。

[0054]

不计算电源线、地线、烧录电源和复用配置引脚,总计需要占用49个可复用引脚资源。

[0055]

不同于flash或者eprom的读写方式,efuse在同一时间只能编程写入1个bit,而同一时间可以读出1~4byte(根据efuse的q位宽决定)。如下表所示在外部编程时,只需要支持read、margin_read、program模式,而standby和power-down模式则不需要支持。相应的,csb、pd引脚可以在片内选择,不需要引出到片外。

[0056]

烧录的过程:

[0057]

当cp、ft、或芯片烧录装置执行烧录动作时需要参照如图9所示内容寻址;地址高位a[11:7]和低位a[6:0]组合起来,直接寻址到要烧录的bit,并且按照图10所示的时序波形,把相应的信号以及烧录电源送入芯片。

[0058]

按图10中时序送入波形及烧录电源后,地址指定的efuse bit烧录完成,在完成后还需要通过读取操作验证此次烧录是否正确。

[0059]

读取的过程

[0060]

当cp、ft、或芯片烧录装置执行读取动作时,需要参照图11所示内容寻址:efuse模块普遍不能做单bit读取。根据efuse的q位宽不同,cp、ft及芯片烧录装置普遍只能一次读取整字节、双字节或四字节。因此只有地址低位a[6:0]有效,寻址到要读取的字节、双字节或四字节。并且按照图12所示的时序波形,把相应的信号送入芯片。

[0061]

按图12时序送入波形后,再根据烧录的位对应表,验证之前烧录的内容是否成功

写入。位对应表参见下图,根据各类型efuse模块的不同,此表有相应的变化。

[0062]

因此,现有包括efuse模块的芯片存在以下不足:

[0063]

封装引脚多:集成efuse模块的soc芯片在做ft测试和客户烧录时,需要在封装中引出并行的地址线和并行的数据线,因此会占用大量的可复用端口。(以图1中示意图来看,除测试所必要的引脚外还至少需要49个以上的额外引脚)

[0064]

efuse模块使用权限分配灵活度差:soc中集成的efuse模块需要装载很多信息和控制位,如芯片id、密钥、生产封装测试的追溯信息、芯片工作模式控制位和芯片引导及访问权限控制位等等。根据厂商和客户之间不同的商业合作模式或者厂商的销售策略,efuse模块中的内容需要满足厂商和客户烧录范围灵活分配,两方都可以烧录efuse模块中的各自被指定的位置,并且同时双方都不可以读取对方的烧录内容。

[0065]

现有通用的efuse模块烧录读取方案通常会规定好厂商和客户之间efuse模块内容的烧录读取范围并通过访问控制位对具体区域加以保护。这种方法在芯片投产后大部分厂商和客户烧录读取范围已被确定,不能随意修改,因此商业推广上的灵活性较差。

[0066]

封装片存在物理读取通路,破解成本低:现有普遍采用的烧录读取方式由于需要实现片外烧录功能,因此存在数据读出的物理通路(验证烧录正确性),而厂商或客户已写入信息都存在着被对方或第三方非法读出的可能性。比如fib修改掉的访问控制位,再通过片外直接读取方式获取相应的片内的加密信息;因此普遍上安全性较低。

[0067]

实施例

[0068]

为了解决现有包括efuse模块的芯片引脚过多的技术问题,本发明提供一种包括efuse模块的芯片、电子装置和芯片烧录控制方法,在保证芯片信息安全的同时减少芯片的引脚,降低芯片的封测成本。

[0069]

如图2所示,本实施例提供一种包括efuse模块的芯片,该芯片100包括:

[0070]

efuse模块140、串并转换单元120、烧录信号分析单元160、控制单元150和引脚,

[0071]

所述引脚包括串行输入信号引脚112、烧录读取控制信号引脚114、118和输出信号引脚116;引脚114为efuse烧录所必须的控制信号,如图一所示(strobe、csb、load、pgenb、pd等控制信号),引脚118为soc内工作所必要的复位和时钟信号,主要为了识别上电或复位后第一次烧录的读取,以便控制第二多路选择器向116送出查空结果信号。

[0072]

控制单元150用于当通过烧录读取控制信号引脚118接收到烧录读取控制信号时,将芯片100设置在烧录验证模式;

[0073]

串并转换单元120用于当通过烧录读取控制信号引脚114接收到烧录读取控制信号时,将通过串行输入信号引脚112输入的串行输入信号转换为并行输入地址信号;

[0074]

efuse模块140用于将经串并转换单元120转换的并行输入地址信号对应位进行烧录处理;

[0075]

烧录信号分析单元160用于基于经efuse模块140处理的烧录信号生成相应的烧录状态信号,烧录状态信号通过输出信号引脚116被输出。

[0076]

具体地,控制单元150接收到烧录读取控制信号引脚118传输的烧录读取控制信号时,输入信号引脚112传输的串行输入信号被输入至串并转换单元120,串并转换单元120转换后的处理信号(例如,并行处理信号)被输入至efuse模块140;

[0077]

烧录信号分析单元160基于efuse模块140处理的烧录信号是否满足预定条件,输

出烧录状态信号,并通过输出信号引脚116输出烧录状态信号。

[0078]

本实施例优选的实施方式中,控制单元150、efuse模块140分别与烧录读取控制信号引脚114、118连接,烧录读取控制信号包含编程信号、读取信号和/或动作有效信号。

[0079]

因此,本实施例提供的上述技术方案中,通过在芯片内部设置有与efuse模块电连接的串并转换单元可以直接接收串行输入信号引脚,并且在芯片内部设置烧录信号分析单元,可以直接在芯片内部完成烧录是否成功的比对,无需将efuse模块内部的烧录信号传输至芯片外部,从而在保证芯片信息安全的同时减少芯片的引脚,降低芯片的封测成本。

[0080]

关于烧录信号分析单元160的具体实现方式,本实施例提供了两种方式:

[0081]

1、奇偶校验方式:

[0082]

具体地,如图3所示,本实施例中,烧录信号分析单元160为奇偶校验单元162,奇偶校验单元162将efuse模块的多位宽q做奇偶校验,输入信号引脚传输两次不同奇偶校验结果对应的输入信号,基于信号烧录前和信号烧录之后读取奇偶校验单元输出奇偶校验结果的变化,判断efuse模块是否烧录成功。

[0083]

2、烧录信号比较方式:

[0084]

具体地,如图4所示,本实施例中,烧录信号分析单元160为烧录信号比较单元164(例如,shift比较单元),并根据两次不同的输出信号,(读取烧录前和烧录后各一次)烧录信号比较单元基于烧录前后两次读取输出数据进行比对,并根据对比结果是否不同,确定efuse模块是否烧录成功。

[0085]

这两种实现方式,分别如原理框图3和原理框图4所示:其主要实现方式相同,只是在输出串行数据的逻辑上存在差别,奇偶校验单元是把efuse模块的多位宽q做奇偶校验(例如q中存在偶数个1,输出0。q中存在奇数个1,输出1),之后把校验位送入多路选择器并且输出。shift比较单元是把连续两次读出的多位宽q做比较(例如连续两次读取,如果当前读取的q和上一次读取的q相同,输出0。不相同,输出1),比较的结果送入多路选择器并且输出。

[0086]

通过图3和图4能看到,本实施例在现有efuse模块复杂接口基础上做了大幅度的精简,并行地址输入和并行数据输出变为串行地址输入和串行数据输出。如上文举例,不计算电源线、地线、烧录电源和复用配置引脚,总计占用复用引脚由49个降为8个,即必要烧录读取控制信号5个,地址输入2个,数据输出1个。

[0087]

具体地:芯片烧录装置(也称芯片烧录器或者片外烧录器)200通过串行协议输入地址,通过串转并单元120转换为efuse模块所需的并行数据线。串行协议既可以是通用的串行协议,也可以是自定义的串行协议。既可以是单线,也可以是双线或多线。本案例按照自定义双线协议举例,比如芯片烧录装置发送串行地址及地址的锁存信号。本实施例所示电路利用地址锁存信号接收到地址信息,同时转换成并行地址送入多路选择器中。

[0088]

例如,串行输入信号引脚为双线串行通信接口,并且双线串行通信接口接收自定义的串行协议通过芯片烧录装置发送串行地址及地址的锁存信号;串并转换单元120与efuse模块140之间设置有第一多路选择器130;第一多路选择器130分别与串并转换单元120、控制单元150连接。其中,第一多路选择器130用于切换烧录动作的地址和读取动作的地址(例如,读取地址会读取两次,地址相同,查看被烧录后参数的变化情况),烧录和读取的地址位数不同。

[0089]

efuse模块140就是soc芯片内集成的efuse单元,控制单元150主要包含一下几个功能:

[0090]

1.每次芯片上电或者复位之后,一旦soc被切换为外部烧录器模式,控制单元150都会主动对efuse模块内容进行一次查空并记录结果。在芯片烧录装置第一次读取任意地址时,控制单元150会把查空结果经由第二多路选择器通过多路选择器串行送出。

[0091]

例如,每次芯片上电或者复位之后,每当芯片被切换为芯片烧录验证模式时,控制单元对efuse模块内容进行一次查空并记录结果;在芯片烧录装置第一次读取任意地址时。但是本实施例发明提供的技术方案不限于此,例如,还可以设置成如果芯片烧录装置不做读取任意地址,直接输出0,或者1或者脉冲或者某个电平也可以实现烧录装置获得查空信息;这些不同的实施方式都属于本发明保护的范围。控制单元将查空结果经由第二多路选择器通过输出信号引脚送出。具体地,烧录信号分析单元160、控制单元150分别与第二多路选择器170连接,第二多路选择器170与输出信号引脚连接。其中,优选地实施方式中,查空信号必不可少,因为无论从奇偶校验读取判断烧录成功,还是烧录前后各读取一次判断烧录成功,都只能向片外烧录器反应烧录位是否变化了。新生产芯片的原始查空(例如,瑕疵检测)操作结果,片外烧录器无法得知,因此需要通过第二多路选择器选择送出;当然,可以不需要专用引脚。

[0092]

2.控制地址和数据的两个多路选择器130、170,在上电进入外部烧录验证模式时,切换为控制单元提供efuse模块地址(查空)。在进入外部烧录验证模式后的第一次任意地址读取时,切换为控制单元150的数据输出(例如,查空结果经由第二多路选择器送出)。在之后的编程或者读取动作时,控制单元150切换多路选择器130、170至芯片烧录装置的正常工作状态(芯片烧录装置编程并校验),芯片烧录装置提供efuse模块地址,芯片烧录装置接收奇偶校验单元162或者shift比较单元164的数据输出。

[0093]

3.奇偶校验单元及shift比较单元

[0094]

奇偶校验单元或者shift比较单元的在实现原理上不相同,单都能达到相同的结果。因此在本实施例中,采用哪种校验或比较单元都可以,例如:

[0095]

1).都可以校验单次编程的结果是否正确。

[0096]

2).生成单bit结果通过多路选择器送出;减少校验信息位宽,减少复用信号占用。

[0097]

3).生成的校验信息都不可以倒退出efuse模块中包含的原始数据。

[0098]

4).在物理上,没有多根数据线由efuse模块附近连接至pad单元附近。因此采用常规破解方式(fib改写访问控制位,然后通过正常路径读出)很难实现;而且成本很高,成功率很低。

[0099]

5.关于奇偶校验单元和shift比较单元的实现原理:

[0100]

如图5所示,通常efuse模块采用单bit编程,多byte数据读出的方式。在编程时全地址(a[11:0])译码到要编程的bit,并且通过烧录控制线实现编程。读取数据时地址低位(a[6:0])译码到要读取的多byte(此例中q的位宽是32bit),并且通过烧录控制线实现读出。在本实施例中,无论是采用奇偶校验单元还是shift比较单元,芯片烧录装置要烧录某一bit,都须经过以下四个步骤:

[0101]

a).通过efuse模块的地址映射表中查询到烧录位(如l2箭头)对应的读取地址(如l1箭头)

[0102]

b).烧录之前读取一次含有烧录位的q输出。(l1箭头所对应地址的q[31:0])

[0103]

c).对烧录位进行烧录动作(l2箭头指定的位)

[0104]

d).烧录之后读取一次含有烧录位的q输出。(l1箭头所对应地址的q[31:0])

[0105]

奇偶校验单元原理:

[0106]

奇偶校验单元和shift比较单元在进行某一bit烧录时的区别在于,奇偶校验单元把烧录前和后的两次读取数据q[31:0]做奇偶校验,并把结果送入芯片烧录装置,芯片烧录装置通过发现烧录之后读取时奇偶校验结果的变化,判断烧录成功。

[0107]

而shift比较单元是把一个编程动作中的编程前后两次读取动作,前一次的q[31:0]输出缓存起来和后一次的q[31:0]输出做比较,如果比较结果相同,则比较结果输出0并缓存后一次q[31:0],如果比较结果不同,则比较结果输出1并缓存后一次q[31:0]。芯片烧录装置通过发现烧录之后读取时比较结果的是否为1,判断烧录成功。

[0108]

芯片烧录装置200包括信号发送模块210,例如发送串行信号和烧录读取控制信号;以及信号接收模块230,例如,接收芯片反馈的烧录结果信号,以及烧录结果判断单元,根据信号接收模块230接收的信号,确定烧录信号是否成功。

[0109]

如图8所示,本实施例提供一种芯片烧录控制方法,应用于芯片烧录装置,该芯片为上述提供的任意一种芯片,芯片烧录控制方法包括:

[0110]

s210.向芯片输入烧录读取控制信号,

[0111]

s220.接收芯片输出的烧录状态信号,

[0112]

s230.根据烧录状态信号是否满足预定的要求,判断芯片的烧录信息是否成功。

[0113]

更具体到,芯片烧录装置200编程采用本实施例所阐述的efuse模块的soc芯片时,需要按照以下逻辑进行工作:

[0114]

1.读取烧录配置文件,找到需要烧录的位的地址,以及对应的读取地址。

[0115]

2.被烧录soc芯片上电,并进入编程模式。

[0116]

3.对特定或者不特定地址进行一次读取(或者不读取地址,查空信息直接送出也可),根据输出的查空信息判断efuse模块内是否存在有信息。所有芯片烧录装置烧录之前都须做此读取动作。此步骤主要为soc厂商用以检查efuse模块是否存在制作缺陷使用(检查出厂时efuse是否有熔断)。

[0117]

4.对需要烧录的位进行烧录,做之前所描述的读取/烧录/读取动作。并根据后一次读取所获得的shift比较结果或者两次读取所获得的奇偶校验数据判断烧录是否成功。

[0118]

如图7所示,本实施例还提供一种芯片烧录控制方法,应用于芯片,该芯片为上述的任意一种芯片,该方法包括:

[0119]

s110.接收烧录读取控制信号,并且当芯片被切换为芯片烧录验证模式时,控制单元对efuse模块内容进行一次查空并记录结果;在芯片烧录装置第一次读取任意地址时,控制单元将查空结果通过输出信号引脚送出(例如,经由第二多路选择器通过输出信号引脚送出);

[0120]

s120.控制单元接收到烧录读取控制信号引脚传输的烧录读取控制信号时,输入信号引脚传输的串行输入信号被输入至串并转换单元,串并转换单元转换后的处理信号被输入至efuse模块;

[0121]

s130.烧录信号分析单元基于efuse模块处理的烧录信号是否满足预定条件,输出

烧录状态信号,并通过输出信号引脚输出烧录状态信号。

[0122]

如图6所示,本实施例还提供一种电子装置300,该电子装置300包括:

[0123]

如上述提供的任意一种的包括efuse模块的芯片100,以及

[0124]

与芯片连接的外围电路310,具体的外围电路可以结合电子装置300的具体应用场景来确定,例如,电子装置300可以是移动终端、pad、电脑、物联网终端(例如音响、家用电器)等,电子装置300内部的外围电路可以是电源或者电压输入电路,以及结合实际需求还可能包括显示器、声音播放器等。

[0125]

采用根本实施例提供的上述技术方案,可以实现以下技术效果中的一种或多种:需要占用可复用引脚资源少,封装的适配性强,小封装芯片也可做efuse烧录。2.没有物理的数据读出路径,破解的成本高,难度大。3.由于片外烧录器无法读出数据,厂商和客户的efuse模块中控制位和信息资源位分配更加灵活,可以开拓更广泛的商业合作模式。

[0126]

本领域普通技术人员可以理解:上述根据本发明实施例的方法可在硬件、固件中实现,或者被实现为可存储在记录介质(诸如cd rom、ram、软盘、硬盘或磁光盘)中的软件或计算机代码,或者被实现通过网络下载的原始存储在远程记录介质或非暂时机器可读介质中并将被存储在本地记录介质中的计算机代码,从而在此描述的方法可被存储在使用通用计算机、专用处理器或者可编程或专用硬件(诸如asic、fpga或soc)的记录介质上的这样的软件处理。可以理解,计算机、处理器、微处理器控制器或可编程硬件包括可存储或接收软件或计算机代码的存储组件(例如,ram、rom、闪存等),当所述软件或计算机代码被计算机、处理器或硬件访问且执行时,实现在此描述的处理方法。此外,当通用计算机访问用于实现在此示出的处理的代码时,代码的执行将通用计算机转换为用于执行在此示出的处理的专用计算机。

[0127]

本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元及方法步骤,能够以电子硬件、或者计算机软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明实施例的范围。

[0128]

最后需要说明的是,上述说明仅是本发明的最佳实施例而已,并非对本发明做任何形式上的限制。任何熟悉本领域的技术人员,在不脱离本发明技术方案范围内,都可利用上述揭示的做法和技术内容对本发明技术方案做出许多可能的变动和简单的替换等,这些都属于本发明技术方案保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1