监控电路的转变的制作方法

1.本公开大致涉及电子电路系统,且更特定来说涉及监控电路的转变。

背景技术:

2.在电子及计算机科学领域中,有限状态机(fms)是指用硬件或软件实施的可采用以模拟某些计算机程序的循序逻辑及/或执行的计算模型。fsm可采用以对许多领域,包含数学、人工智能、游戏及语言学中的问题进行建模。

3.数字电路中实施的fsm可包含但不限于可编程逻辑装置、可编程逻辑控制器、逻辑门、双稳态触发器(flip-flop)及/或继电器。在此情况下,fsm的可编程组件存储状态变量及组合逻辑以确定fsm的状态转变及输出。另外,在一些实例中,fsm可在计算平台,例如通用计算机或控制器上实例化。

技术实现要素:

4.在第一实例中,一种电路包含保护触发电路,所述保护触发电路包含经调适以耦合到第一状态信号的第一输入节点、经调适以耦合到第二状态信号的第二输入节点及经调适以提供触发信号的输出节点。所述保护触发电路经调适以基于所述第一状态信号及所述第二状态信号来确定正在进行的状态转变及基于所述状态转变是否正在进行来提供所述触发信号。所述电路可包含复位同步器电路,所述复位同步器电路包含耦合到所述保护触发电路的所述输出节点的输入节点、经调适以耦合到时钟信号的时钟节点及经调适以基于所述触发信号来提供同步信号的输出节点。所述电路可进一步包含超时电路,所述超时电路包含耦合到所述复位同步器电路的所述输出节点的输入节点、经调适以耦合到所述时钟信号的时钟节点及经调适以基于所述同步信号来提供超时信号的输出节点。所述电路还包含复位请求器电路,所述复位请求器电路包含耦合到所述保护触发电路的所述输出节点的第一输入节点、耦合到所述超时电路的所述输出节点的第二节点及经调适以基于所述触发信号及所述超时信号来提供复位信号的输出节点。

5.在第二实例中,一种方法包含响应于检测到电路中的转变正在进行而断言触发信号。所述方法还包含响应于检测到所述触发信号被断言达时钟信号中的第一数目个周期而断言同步信号。所述方法进一步包含响应于检测到所述同步信号被断言达所述时钟信号中的第二数目个周期而断言超时信号。所述方法还包含响应于检测到所述超时信号及所述触发信号同时被断言而断言复位信号。

附图说明

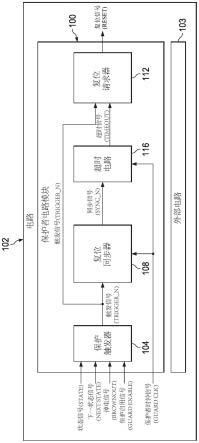

6.图1是可采用以监控外部电路的操作的保护者电路模块的框图。

7.图2是fsm的保护者电路模块的电路图。

8.图3是包含监控fsm中的状态的转变的保护者电路模块的电路的实例。

9.图4是fsm的状态图的实例。

10.图5是用于监控外部电路的操作的实例方法的流程图。

具体实施方式

11.本公开涉及用于外部电路(例如在电路(例如,ic芯片)上实施的有限状态机(fsm))的保护者电路(例如,子电路)。一些fsm在长时间段内快速切换状态。例如,在一个实例中,流量计电路可能在测量流量的第一状态与将值写入到特性化经测量流量的存储器的第二状态之间切换。在此类情况下,在fsm的整个寿命中,fsm可能卡在状态转变之间。例如,在流量计电路的实例中,第一状态(测量流量,模拟操作)与第二状态(写入到存储器,数字操作)之间的转变可包含切换功率模式。如果状态转变未按预期完成,那么此类状态转变可能减慢或拖延所述电路的操作。此外,面积及功率约束可能无法为此类问题提供足够复杂的解决方案。

12.保护者电路模块接收独立于所述电路内的其它时钟信号而操作的保护者时钟信号。为了提高此电路的稳健性,保护者电路检测fsm中的状态转变的开始(例如,基于状态信号及下一状态信号),且如果在状态转变完成之前给定一段时间流逝,那么作出响应。在一些实例中,响应于检测到状态转变,保护者电路模块断言触发信号。保护者电路模块经配置以响应于触发信号被断言达保护者时钟信号中的阈值数目个周期而断言复位信号。复位信号可采用来将fsm复位为已知的安全状态,例如初始通电状态。相反,如果状态转变在保护者时钟信号循环阈值数目个周期之前完成,那么触发信号被取消断言,且复位信号不被断言。以这种方式,如果状态转变花费太长时间(超过保护者时钟信号的阈值周期计数),那么保护者电路模块断言复位信号,这引起fsm复位。

13.图1是被实施为电路,例如可采用来监控在电路102(例如系统芯片(soc))上实施的外部电路103的操作的子电路的保护者电路模块100的框图。外部电路103是例如由在soc上操作的控制器实施。在此情况下,保护者电路模块100被实施为soc上的子电路。保护者电路模块100经配置以基于输入信号的状态来断言复位信号reset。复位信号reset被实施为高优先级复位信号。因此,电路102的组件(例如,例如外部电路103)响应于复位信号reset被断言而复位并恢复为安全状态,例如初始通电状态。

14.在一些实例中,外部电路103被实施为fsm。在其它实例中,外部电路103被实施为用于促进握手的电路。在其它实例中,外部电路103被实施为功率模块。出于简化解释的目的,描述其中外部电路103被实施为fsm的实例。在这些实例中的任一者及其它实例中,外部电路103可具有可能引起外部电路103延迟或拖延的转变(例如,状态转变、信号转变、反馈返回信号等)。

15.更特定来说,在一些实例中,外部电路103被实施为电路102的软件定义fsm,特别是在其中电路102被实施为具有嵌入式控制器的soc的情况下。在其它实例中,外部电路103被实施为电路102内的硬件模块。在任一情况(及其它情况)下,可能存在引起fsm中的状态转变延迟或拖延的竞争条件及/或优先级层次。另外,即使在其中外部电路103相对简单的情况下,功率骤降(例如,掉电)也可能引起外部电路103处的亚阈值电压电平,且此类亚阈值电压电平可能延迟或阻止转变完成。例如,在其中转变包含改变功率模式的情况下,功率骤降可能阻碍被实施为fsm的外部电路103完成从具有低功率模式的状态到具有高功率模式的状态的转变。

16.保护者电路模块100接收专用时钟信号guard clk,所述专用时钟信号可替代地被称为保护者时钟信号。在一些实例中,专用时钟信号guard clk被实施为独立于电路102上采用的其它时钟信号的时钟信号。在一些实例中,保护者电路模块100包含用于产生保护者时钟guard clk的组件(例如,时钟发生器)。在其它实例中,保护者时钟guard clk是由保护者电路模块100外部的电路102的组件产生。专用时钟信号guard clk具有比在外部电路103中完成的最长转变的最大容许时间长的时钟计数器间隔。例如,在一些实例中,专用时钟信号guard clk比控制外部电路103的操作的电路102的系统时钟信号的计数器间隔长三个数量级或更多。例如,在一些实例中,如果系统时钟信号驱动外部电路103上的操作,且具有约1微秒(μs)的计数器间隔,那么专用时钟信号guard clk将具有约1毫秒(ms)或更长的计数器间隔。以这种方式,专用时钟信号guard clk比系统时钟信号慢。

17.保护者电路模块100包含保护触发电路,所述保护触发电路被称为保护触发器104。保护触发器104经配置以基于输入信号的状态来断言触发信号trigger_n。特定来说,保护触发器104接收状态信号state及特性化外部电路103的当前状态的下一状态信号next state,其分别被实施为fsm及外部电路103的下一状态。状态信号state及下一状态信号next state表示基于外部电路103的状态矢量的比较来产生的信号。保护触发器104还接收特性化电路102的功率状态的掉电信号brownout。例如,在其中不存在足够功率来操作电路102及/或电路102被复位的情况下,掉电信号brownout被断言。在一些实例中,保护触发器104还接收经断言以启用保护触发器104的操作的保护启用信号guard enable。

18.在本文中所描述的实例中,关于给定信号的术语“断言”(及其派生词)是指取决于给定信号的类型给定信号被指派逻辑1或逻辑0。更特定来说,如果给定信号是高电平有效信号,那么给定信号的断言将给定信号设置为逻辑1。另外,如果给定信号是低电平有效信号,那么给定信号的断言将给定信号设置为逻辑0。相反,关于给定信号的术语“取消断言”(及其派生词)指示给定信号被指派与给定信号被指派以断言给定信号的逻辑值相反的逻辑值。例如,如果给定信号是高电平有效信号,那么取消断言给定信号将给定信号设置为逻辑0。另外,如果给定信号是低电平有效信号,那么取消断言给定信号将给定信号设置为逻辑1。此外,应理解,在实例中给定信号分别被描述为高电平有效或低电平有效,在其它实例中,给定信号分别被实施为低电平有效或高电平有效。

19.在一些实例中,保护触发器经配置以响应于检测到在外部电路103处正在进行状态转变而断言触发信号trigger_n。状态转变是由状态信号state及下一状态信号next state的状态指示。更特定来说,如果状态信号state被断言且下一状态信号next state未被断言,或反之亦然,那么保护触发器104确定外部电路103在转变(例如,状态转变)中,且保护触发器104断言触发信号trigger_n。相反,如果状态信号state及下一状态信号next state两者被断言,那么保护触发器104取消断言触发信号trigger_n。

20.另外,数个条件可能引起保护触发器禁止(阻止)触发信号trigger_n的断言。特定来说,保护触发器104经配置使得如果掉电信号brownout被断言,那么保护触发器104取消断言触发信号trigger_n。掉电信号brownout在其中电路102被复位且包含外部电路103的组件被设置为安全状态,例如初始通电状态的情况下被断言。保护触发器104经配置以取消断言触发信号trigger_n以允许电路102的外部电路103被设置为初始通电状态而不中断。

21.类似地,如果保护启用信号guard enable被取消断言,那么保护触发器104经配置

以禁止触发信号的断言。保护启用信号guard enable的取消断言指示保护者电路模块100的操作被停用。

22.在一些实例中,保护触发器104将触发信号trigger_n维持在断言状态直到(i)状态信号state及下一状态信号next state被断言,(ii)掉电信号brownout被断言或(iii)保护启用信号guard enable被取消断言。响应于检测到事件(i)到(iii)中的一者,保护触发器104取消断言触发信号trigger_n。在其它实例中,比事件(i)到(iii)更多或更少的事件引起保护触发器104取消断言触发信号trigger_n。

23.触发信号trigger_n被提供到被称为复位同步器108的复位同步器电路及被称为复位请求器112的复位请求器电路。复位同步器108还接收专用时钟信号guard clk作为输入。复位同步器108经配置以在触发信号trigger_n被断言达专用时钟信号guard clk的预定数目个周期的情况下,断言同步信号sync_n。在一些实例中,复位同步器108经配置为移位寄存器。作为一个实例,复位同步器108经配置以响应于触发信号trigger_n被断言达专用时钟信号guard clk的至少两个周期而断言同步信号sync_n。在其它实例中,复位同步器108经配置以在触发信号trigger_n已被断言达专用时钟信号guard clk的多于两个或少于两个周期之后断言同步信号sync_n。

24.同步信号sync_n被提供到超时电路116。超时电路116还接收专用时钟信号guard clk。超时电路116经配置以在同步信号sync_n被断言达专用时钟信号guard clk的预定数目个周期的情况下,断言超时信号timeout。在一些实例中,超时电路116经配置为移位寄存器。作为一个实例,超时电路116经配置以响应于同步信号sync_n被断言达专用时钟信号guard clk的至少三个周期而断言超时信号timeout。在其它实例中,超时电路116经配置以在同步信号sync_n已被断言达专用时钟信号guard clk的多于三个或少于三个周期之后断言超时信号timeout。

25.超时信号timeout及触发信号trigger_n被提供到复位请求器112。如果触发信号trigger_n及超时信号timeout两者被断言,那么复位请求器112产生复位信号reset。如所述,复位信号reset被实施为引起电路102将外部电路103复位为初始通电状态(或一些其它安全状态)的高优先级请求信号。

26.通过实施保护者电路模块100,为外部电路103提供相对简单且稳健的状态转变监控电路。特定来说,保护者电路模块100在其中外部电路103在状态转变之间延迟超过专用时钟信号guard clk的阈值数目个周期(例如,达专用时钟信号guard clk的5个周期)的情况下断言复位信号reset。通过以这种方式断言复位信号reset,保护者电路模块100提高电路102的稳健性。此外,保护者电路模块100消除对外部电路103的转变的高功率、复杂监控的需要。

27.图2是fsm的保护者电路模块200的电路图。保护者电路模块200可采用以实施图1的保护者电路模块100。出于简化解释的目的,在图1及2中采用相同信号及组件名称来表示相同信号或组件。

28.保护者电路模块200被实施为电路,例如图1的电路102的模块。除非另有所述,否则保护者电路模块200的组件可在亚阈值电平下操作。因此,在其中无足够功率可用来操作fsm的情况下,保护者电路模块200仍然可以预期方式操作。保护者电路模块200包含被采用以实施图1的保护触发器104的保护触发器204。保护触发器204接收特性化在电路(例如图1

的外部电路103)上实施的fsm的状态的输入。更特定来说,保护触发器204接收特性化fsm的状态的状态信号state及下一状态信号next state。在一些实例中,状态信号state及下一状态信号next state特性化fsm的状态矢量的比较。

29.状态信号state及下一状态信号next state经耦合到保护触发器204的xnor门208的输入。xnor门208将状态转变触发信号state transition trigger_n输出到保护触发器204的or门212的输入。

30.术语“耦合”(及派生词)在整个说明书中使用。所述术语可涵盖实现与本公开的描述一致的功能关系的连接、通信或信号路径。例如,如果装置a产生信号以控制装置b以执行动作,那么在第一实例中,装置a经耦合到装置b,或在第二实例中,如果中介组件c未基本上更改装置a与装置b之间的功能关系,使得装置b通过由装置a产生的控制信号而受装置a控制,那么装置a通过中介组件c耦合到装置b。

31.掉电信号brownout经耦合到or门212,且保护启用信号guard enable经耦合到or门212的反相输入。在所说明实例中,掉电信号brownout及保护启用信号guard enable是高电平有效信号。掉电信号brownout的断言指示fsm被复位为安全状态,例如初始通电状态。例如,掉电信号brownout是在其中fsm的功率降至低于阈值电平的情况下被断言。

32.or门212输出触发信号trigger_n。在所说明实例中,触发信号trigger_n是低电平有效信号。保护触发器204响应于状态转变触发信号state transition trigger_n被取消断言、掉电信号brownout(逻辑0)被取消断言且保护启用信号guard enable(逻辑1)被断言而断言触发信号(逻辑0)trigger_n。

33.触发信号trigger_n经耦合到复位同步器216的输入。专用时钟信号guard clk经耦合到复位同步器216的时钟输入。专用时钟信号guard clk具有比fsm中的最长转变的最大时间长的计数器间隔。例如,在一些实例中,专用时钟信号guard clk具有比被采用来驱动fsm的操作的电路的系统时钟信号长三个数量级的计数器间隔。例如,如果系统时钟信号具有约100纳秒(ns)的计数器间隔,那么专用时钟信号guard clk具有约100μs的计数器间隔。在其它实例中,系统时钟信号与专用时钟信号guard clk的计数器间隔之间的差是不同的。复位同步器216经配置以在触发信号trigger_n被断言(逻辑0)达专用时钟信号guard clk的至少两个周期的情况下,断言同步信号sync_n(逻辑0)。在所说明实例中,同步信号sync_n是低电平有效信号。在概念上,复位同步器216接收异步信号,即,触发信号trigger_n,且输出与专用时钟信号guard clk同步的信号,即,同步信号sync_n。

34.在一些实例中,复位同步器216经配置为移位寄存器。更特定来说,在所说明实例中,复位同步器216是用两个级联d双稳态触发器,即,第一d双稳态触发器220及第二d双稳态触发器224实施。触发信号trigger_n经耦合到第一d双稳态触发器220及第二d双稳态触发器224的预置输入pr。专用时钟信号guard clk经耦合到第一d双稳态触发器220及第二d双稳态触发器的时钟输入。接低输入228(例如,约0伏)经耦合到第一d双稳态触发器220的数据输入d以将逻辑0施加到第一d双稳态触发器220的数据输入d。第一d双稳态触发器220的非反相输出q经耦合到第二d双稳态触发器220的数据输入d。第二d双稳态触发器224的非反相输出q输出复位同步器216的同步信号sync_n。

35.同步信号sync_n经耦合到超时电路232的输入。另外,专用时钟信号guard clk经耦合到超时电路232的时钟输入。超时电路232经配置以在同步信号sync_n被断言(逻辑0)

达专用时钟信号guard clk的三个或更多个周期的情况下,断言超时信号timeout(逻辑1)。在所说明实例中,超时信号timeout是高电平有效信号。

36.在一些实例中,超时电路232被实施为移位寄存器。更特定来说,超时电路232可用三个级联d双稳态触发器,即,第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244实施。在其它实例中,超时电路232是用不同数目个d双稳态触发器实施。

37.专用时钟信号guard clk经耦合到超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244的时钟输入。同步信号sync_n经耦合到超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244的归零输入cl。超时电路232包含在第一d双稳态触发器236的数据输入d上断言逻辑1的接高输入248。

38.第一d双稳态触发器236的非反相输出q经耦合到第二d双稳态触发器240的数据输入d。类似地,第二d双稳态触发器240的非反相输出q经耦合到第三d双稳态触发器244的数据输入d。此外,第三d双稳态触发器244的非反相输出q提供超时信号timeout。

39.超时信号timeout经耦合到复位请求器250的输入。触发信号trigger_n也经耦合到复位请求器250的输入。复位请求器250响应于超时信号timeout及触发信号trigger_n同时被断言而断言复位信号reset(逻辑1)。在所说明实例中,复位信号reset是高电平有效信号。

40.在所说明实例中,复位请求器250是用具有反相输入的and门254实施。在其它实例中,复位请求器250是用更多逻辑门及/或其它电路组件实施。触发信号trigger_n经耦合到and门254的反相输入。超时信号timeout经耦合到and门254的非反相输入。

41.在所说明实例中,状态信号state及下一状态信号next state是高电平有效信号且状态转变触发信号state transition trigger_n是低电平有效信号。在其中fsm保持在相同状态的情况下,状态信号state及下一状态信号next state两者被断言(逻辑1)。在其中fsm在状态之间转变的情况下,状态信号state或下一状态信号next state被取消断言(逻辑0)。如果状态信号state或下一状态信号next state中的任一者(或两者)被取消断言(逻辑0),那么状态转变触发信号state transition trigger_n被断言(逻辑0)。保护触发器204响应于状态转变触发信号state transition trigger_n(逻辑0)被断言、掉电信号brownout(逻辑0)被取消断言且保护启用信号guard enable(逻辑1)被断言而断言触发信号(逻辑0)trigger。相反,保护触发器204响应于状态转变触发信号state transition trigger_n(逻辑1)被取消断言、掉电信号brownout(逻辑1)被断言或保护启用信号guard enable(逻辑0)被取消断言而取消断言触发信号trigger_n(逻辑1)。

42.触发信号trigger_n(逻辑1)被取消断言引起复位同步器216上的第一d双稳态触发器220及第二d双稳态触发器224以预置模式操作。在预置模式中,第一d双稳态触发器220及第二d双稳态触发器220两者在相应的非反相输出q上输出逻辑1。因此,如果触发信号trigger_n被取消断言(逻辑1),那么同步信号sync_n也被取消断言(逻辑1)。

43.同步信号sync_n(逻辑1)被取消断言引起超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244在归零模式中操作。在归零模式中,超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244在相应的非反相输出q上输出逻辑0。如所述,超时电路232的第三d双稳态触发器244的非反相输

出q提供在非反相输入q处耦合到复位请求器250的and门254的超时信号timeout。另外,触发信号trigger_n经耦合到复位请求器250的and门254的反相输入。超时信号timeout(逻辑0)被取消断言且触发信号trigger_n(逻辑1)被取消断言引起and门254取消断言复位信号reset(逻辑0)。因此,触发信号trigger_n(逻辑1)被取消断言引起复位信号reset被取消断言(逻辑0)。

44.相反,触发信号trigger_n(逻辑0)被断言引起复位同步器216的第一d双稳态触发器220及第二d双稳态触发器224在移位模式中操作。在移位模式中,由接低输入228施加的逻辑0经释放到复位同步器216的d双稳态触发器的级联中。在此情况下,复位同步器216的第一d双稳态触发器220的非反相输出q响应于专用时钟信号guard clk的下一脉冲而设置为逻辑0。随后,响应于在第二d双稳态触发器224的数据输入d处接收到逻辑0,第二d双稳态触发器响应于专用时钟信号guard clk的下一脉冲而在非反相输出q上输出逻辑0。如所述,复位同步器216的第二d双稳态触发器224上的非反相输出q将同步信号sync_n提供到超时电路232,使得同步信号sync_n被断言(逻辑0)。

45.总之,复位同步器216经配置以在触发信号trigger_n被断言(逻辑0)达专用时钟信号guard clk的至少两个周期的情况下,断言同步信号sync_n(逻辑0)。另外,如果触发信号trigger_n在专用时钟信号guard clk的至少两个时钟周期完成之前被取消断言(逻辑1),那么第一d双稳态触发器220及第二d双稳态触发器224两者转变为预置模式,且同步信号sync_n被取消断言(逻辑1)。

46.同步信号sync_n(逻辑0)的断言将超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244的归零输入cl设置为逻辑0。作为响应,超时电路232的第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244中的每一者在移位模式中操作。在移位模式中,接高输入248将逻辑1施加在第一d双稳态触发器236的数据输入d上。响应于专用时钟信号guard clk的下一脉冲,第一d双稳态触发器236在非反相输出q上输出逻辑1,所述非反相输出q经耦合到第二d双稳态触发器240的数据输入d。

47.随后,如果第二d双稳态触发器240的数据输入d被设置为逻辑1,那么第二d双稳态触发器240响应于专用时钟信号guard clk的下一时钟脉冲而在第二d双稳态触发器240的非反相输出q上输出逻辑1。如所述,第二d双稳态触发器240的非反相输出q经耦合到第三d双稳态触发器244的数据输入d。如果第三d双稳态触发器244的数据输入d被设置为逻辑1,那么第三d双稳态触发器244响应于专用时钟信号guard clk的下一时钟脉冲而在第三d双稳态触发器244的非反相输出q上输出逻辑1。如所述,第三d双稳态触发器244的非反相输出q是超时信号timeout。

48.总之,超时电路232经配置以在同步信号sync_n被断言(逻辑0)达专用时钟信号guard clk的至少三个周期的情况下,断言超时信号timeout(逻辑1)。另外,如果同步信号sync_n在专用时钟信号guard clk的至少三个时钟周期完成之前被取消断言(逻辑1),那么第一d双稳态触发器236、第二d双稳态触发器240及第三d双稳态触发器244转变为归零模式,且超时信号timeout被取消断言(逻辑0)。响应于超时信号timeout(逻辑1)被断言且触发信号trigger_n(逻辑0)被断言,复位请求器250断言复位信号reset。

49.总之,如果触发信号trigger_n保持被断言(逻辑0)达专用时钟信号guard clk的

阈值数目个周期(例如,保护者时钟周期guard clk的至少五个周期),那么复位同步器216、超时电路232及复位请求器250断言复位信号reset(逻辑1)。

50.在一些实例中,复位信号reset是高优先级复位请求。因此,响应于reset请求被断言,fsm被设置为初始通电状态或其它安全状态。因此,保护者电路模块200是用于fsm的相对简单且稳健的状态转变监控电路。特定来说,在其中fsm在状态转变之间延迟过长(例如,达专用时钟信号guard clk的5个周期)的情况下,保护者电路模块200断言复位信号reset。保护者电路模块200消除对fsm状态转变的高功率、复杂监控的需要。

51.图3说明包含监控fsm 308中的状态转变的保护者电路模块304的电路300(例如,soc)的实例。电路300可采用来实施图1的电路102。更特定来说,保护者电路模块304可采用来实施图1的保护者电路模块100及/或图2的保护者电路模块200。

52.在本实例中,fsm 308作为在电路300的控制器312上操作的软件实例化fsm来操作。在一些实例中,控制器312被实施为包含具有用于实施fsm 308的嵌入式指令的通用处理器的计算平台。在各种实例中,fsm 308被实施为mealy状态机、moore状态机或medvedev状态机或其组合。

53.在所说明实例中,控制器312与传感器316进行通信。在一些实例中,传感器316是模拟传感器,例如流量计、温度传感器、加速度计等。在任何此情况下,假设fsm 308控制传感器316的操作。例如,在一个实例中,在给定状态下,fsm 308引起传感器316测量外部条件(例如,流量、温度、加速度等)且在另一状态下,fsm 308将特性化经测量条件的数据写入到控制器312的非暂时性存储器。在此实例中,在给定状态下,fsm308在高功率模式中操作,而在另一状态下,fsm 308在低功率模式中操作。因此,在这个实例中,给定状态与另一状态之间的切换包含切换功率模式。在一些例子中,功率模式之间的切换阻碍或阻止fsm 308完成状态转变。

54.控制器312包含fsm状态逻辑模块320。fsm状态逻辑模块320被实施为监控fsm308的状态的门网络。作为实例,fsm状态逻辑模块320比较fsm 308的状态矢量以产生特性化fsm 308的当前状态的状态信号state及特性化fsm 308的下一状态的下一状态信号next state。状态信号state及下一状态信号next state被提供到保护者电路模块304。

55.在一些实例中,控制器312提供掉电信号brownout。掉电信号brownout特性化电路300的功率状态。掉电信号brownout例如在其中不存在足够功率来操作电路300及/或fsm 308被复位的情况下被断言。在一些实例中,控制器312还向保护者电路模块304提供经断言以启用保护者电路模块304的操作的保护启用信号guard enable。

56.电路300还包含产生专用时钟信号guard clk的时钟发生器324。专用时钟信号guard clk独立于所述电路中的其它时钟信号,包含但不限于由控制fsm 308的操作的控制器312的系统时钟发生器326(或其它组件)产生的系统时钟信号sys clk而操作。专用时钟信号guard clk具有比fsm 308的状态转变的最大转变时间长的计数器间隔。在一些实例中,专用时钟信号guard clk具有比系统时钟信号sys clk的周期时间长三个数量级(或更多)的周期时间(时段)。因此,如果系统时钟信号sys clk具有20μs的周期时间,那么专用时钟信号guard clk具有20ms或更长的周期时间。在其它实例中,选择专用时钟信号guard clk与系统时钟信号sys clk的周期时间之间的其它关系。

57.保护者电路模块304经配置以在某些条件下断言复位信号reset,如本文中所描

述。更特定来说,保护者电路模块304经配置以在其中保护启用信号guard enable被断言、掉电信号brownout被取消断言且状态信号state及下一状态信号next state指示fsm 308处于状态转变中达专用时钟信号guard clk的至少阈值数目个周期(例如,五个时钟周期)的情况下断言复位信号reset。复位信号reset被提供到控制器312。响应于复位信号reset的断言,控制器312命令fsm 308转变为安全状态,例如初始通电状态。

58.图4说明描绘图3的fsm 308的可能状态的实例的状态图400。状态图400说明四种可能的状态,即,状态0s0、状态1s1、状态2s2及状态3s3。另外,假设状态机还包含未展示的结束状态e0。状态机(包含由状态图400实施的fsm)的设计通常依赖于不准确的假设。特定来说,一些此类fsm假设时间仅在fsm处于离散状态中时,即,在fsm处于状态0s0、状态1s1、状态2s2或状态3s3中时流逝。另外,fsm通常以状态转变在逻辑上是瞬时的,使得仅在转变期间采取的动作是旗标及变量的设置及/或信号的发送的不准确假设进行设计。在此情况下,这些动作是在fsm进入下一状态之前采取。又此外,fsm通常以每次进入一种状态,就开始那个状态的动作的假设进行设计。因此,指向同一状态的状态转变引起从进入所述状态的开始重复动作,且在进入状态后开始的每一动作在进行任何测试以退出所述状态之前完成。此等假设简化fsm的设计,但可能导致可阻碍或阻止fsm完成从一种状态到另一状态的转变的亚稳条件。

59.在状态图400中,假设fsm包含影响fsm状态的变量。在本实例中,此类变量包含复位变量reset、递增计数变量upcnt、递减计数变量dncnt、启用变量en及错误变量err。另外,在状态图400中,根据操作的优先级在每一状态的纵轴上列出操作。因此,如果两个操作是可能的,那么基于变量的状态,执行对相应状态具有最高优先级的操作,且不执行较低优先级的操作。因此,操作的优先级影响状态转变,如本文中所描述。

60.在状态0s0中,在404,fsm检测到复位变量reset已被设置为逻辑1。在此情况下,无论先前或当前状态,fsm均转变为由状态矢量all:s0所指示的状态0s0。状态0s0是初始通电状态,其中变量被设置为已知值。在图4中所说明的实例中,假设图3中所说明的复位信号reset的断言将复位变量reset设置为逻辑1。另外,在状态0s0中,在408,如果递增计数变量upcnt及启用变量en两者被设置为真(逻辑1),那么fsm转变为状态1s1,如由状态矢量s0:s1所指示。此外,在状态0s0中,在412,如果递减计数变量dncnt或错误变量err被设置为真(逻辑1),那么fsm保持在状态0s0,如由状态矢量s0:s0所指示。另外,在状态0s0中,当递增计数变量upcnt及递减计数变量dncnt两者为真(逻辑1)时,假设递增计数变量upcnt具有比递减计数变量dncnt高的优先级。因此,如果递增计数变量upcnt及递减计数变量dncnt两者为真(逻辑1),那么执行408的操作,且fsm转变为状态1s1。

61.在状态1s1中,在416,如果递减计数变量dncnt为真(逻辑1),那么fsm转变为状态0s0,如由状态矢量s1:s0所指示。另外,在状态1s1中,在420,如果递增计数变量upcnt及启用变量en为真(逻辑1),那么fsm转变为状态2s2,如由状态矢量s1:s2所指示。在状态1s1中,假设递减计数变量dncnt具有比递增计数变量upcnt高的优先级。因此,如果递增计数变量upcnt及递减计数变量dncnt两者为真(逻辑1),那么执行416的操作,且fsm转变为状态0s0。

62.在状态2s2中,在424,如果递增计数变量upcnt为真(逻辑1),那么fsm转变为状态3s3,如由状态矢量s2:s3所指示。在状态2s2中,在428,如果递减计数变量dncnt为真(逻辑1),那么fsm转变为状态1s1,如由状态矢量s2:s1所指示。在状态2中,在操作432,如果递增

计数变量upcnt及启用变量en为真(逻辑1),那么fsm转变为状态e0(未展示),如由状态矢量s2:e0所指示。然而,在状态2s2中,不执行在操作432的状态转变为e0,因为在操作424及432两者中,递增计数变量upcnt被设置为真(逻辑1)且424的操作具有比432的操作高的优先级。因此,432的操作被假设是不必要的。

63.在状态3s3中,在436,如果递增计数变量upcnt及启用变量en为真(逻辑1),那么fsm转变为状态e0(未展示)。在状态3s3中,在440,如果递减计数变量dncnt为真(逻辑1),那么fsm转变为状态2,如由状态矢量s3:s2所指示。在状态3s3中,在操作444,如果递增计数变量upcnt为真(逻辑1),那么fsm转变为结束状态e0,如由状态矢量s3:e0所指示。此外,在状态3中,因为436的操作具有比444的操作高的优先级,所以在启用变量en为假(逻辑0)且递增计数变量upcnt为真(逻辑1)的情况下,将仅执行444的操作。

64.如由状态图400所展现,即使简单的fsm也可能具有可导致意外行为的复杂性,特别是如果在未完全考虑操作的优先级的情况下设计fsm。此外,如果fsm的功率达到亚阈值电平,那么一些变量可被设置为亚稳状态,这可能阻碍或阻止fsm完成状态之间的转变。

65.在状态图400中,假设保护者电路模块,例如图1的保护者电路模块100、图2的保护者电路模块200及/或图3的保护者电路模块304经配置以监控状态s0到s3之间的转变。在此情况下,保护者时钟模块响应于检测到状态转变(由所说明状态矢量所指示)而断言触发信号。如果状态转变未在提供到保护者电路模块的专用时钟信号的阈值数目个周期内完成,那么保护者电路模块断言复位信号,这引起状态图400中特性化的fsm执行操作404,使得fsm转变为状态0s0。

66.重新参考图3,如图1及2中所展现,保护者电路模块304是以简单设计实施。事实上,如图4中所展现,保护者电路模块304具有比fsm 308简单的逻辑。另外,如图4中所展现,如果fsm 308未在保护者时钟周期guard clk的阈值数目个(例如,五个)时钟周期内完成状态转变,那么复位信号reset的断言引起fsm进入安全状态(状态0s0,在图4中)。

67.图5说明用于监控外部电路的操作的实例方法500的流程图。在一些实例中,方法500是由电路,例如图1的保护者电路模块100、图2的保护者电路模块200及/或图3的保护者电路模块304实施。在一些实例中,外部电路是用图1的外部电路103实施。在此情况下,外部电路被实施为fsm。

68.在505,所述电路监控外部电路的操作。在510,由所述电路的保护触发电路(例如,图1的保护触发器104)做出有关外部电路中的转变是否正在进行的确定。在一些实例中,基于信号,例如图1的状态信号state、下一状态信号next state、掉电信号brownout及/或保护启用信号guard enable的比较来做出510的确定。在其它实例中,信号的其它组合及/或子集可采用以启用510的检测。如果510的确定是否定的(例如,否),那么方法500返回到505)。如果510的确定是肯定的(例如,是),那么方法500前进到515。

69.在515,所述电路的保护触发电路断言第一信号,例如图1的触发信号trigger_n。在517,做出有关转变是否仍然正在进行的确定。如果517的确定是否定的(例如,否),那么方法500前进到519。如果517的确定是肯定的(例如,是),那么方法前进到520。在519,取消断言第一信号,这指示转变已完成,且方法500返回到505。

70.在520,做出有关第一信号是否已被断言达专用时钟信号的第一预定数目个时钟周期的确定。例如,由所述电路的复位同步器电路,例如图1的复位同步器108做出520的确

定。如果520的确定是否定的(例如,否),那么方法500返回到517。如果520的确定是肯定的(例如,是),那么方法500前进到525。

71.在525,所述电路的复位同步器电路断言第二信号,例如图1的同步信号sync_n。在527,做出有关转变是否仍然正在进行的另一确定。如果527的确定是否定的(例如,否),那么方法500前进到529。如果在527的确定是肯定的(例如,是),那么方法前进到530。在529,取消断言第二信号,从而指示转变已完成,且方法500返回到519。

72.在530,做出有关第二信号是否已被断言达专用时钟信号的第二预定数目个时钟周期的确定。例如,由所述电路的超时电路,例如图1的超时电路116做出530的确定。如果530的确定是否定的(例如,否),那么方法500返回到527。如果530的确定是肯定的(例如,是),那么方法500前进到535。

73.在535,所述电路的超时电路断言第三信号,例如图1的超时信号timeout。在540,做出有关转变是否仍然正在进行的又一确定。例如,由所述电路的复位请求器电路,例如比较第一信号及第三信号的图1的复位请求器112做出540的确定。例如,如果复位请求器确定第三信号及第一信号两者同时被断言,那么540的确定是肯定的,且如果第三信号或第一信号中的任一者(或两者)被取消断言,那么540的确定是否定的。如果540的确定是否定的(例如,否),那么方法500前进到542。如果540的确定是肯定的(例如,是),那么方法500前进到545。在542,取消断言第三信号且方法500返回到529。在545,复位请求器断言输出信号,例如图1的复位信号reset。在一些实例中,输出信号被提供到包含外部电路的控制器,例如图3的控制器312的输入节点。

74.在所描述实施例中修改是可能的,且在权利要求书的范围内,其它实施例是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1